ECE 313 Computer Organization Name FINAL EXAM December 14 ...

ECE 313 Computer Organization Name FINAL EXAM December 14 ...

ECE 313 Computer Organization Name FINAL EXAM December 14 ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

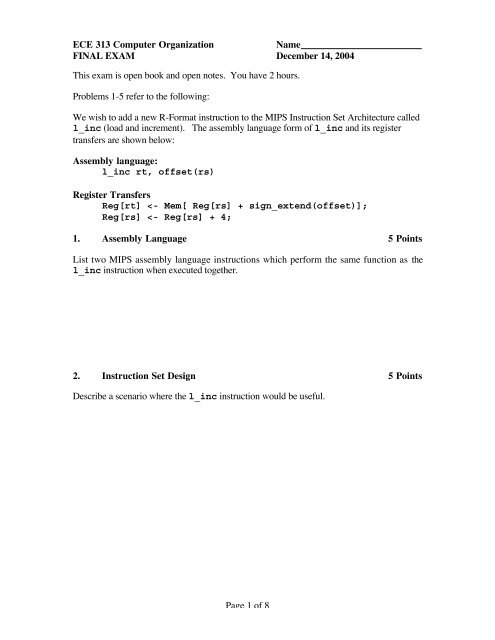

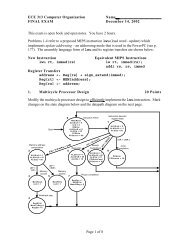

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 2004This exam is open book and open notes. You have 2 hours.Problems 1-5 refer to the following:We wish to add a new R-Format instruction to the MIPS Instruction Set Architecture calledl_inc (load and increment). The assembly language form of l_inc and its registertransfers are shown below:Assembly language:l_inc rt, offset(rs)Register TransfersReg[rt]

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 20043. Multicycle Processor Design 20 Points(a) Modify the multicycle processor design to efficiently implement the l_inc instruction.Mark changes on the state diagram below and the datapath diagram on the next page.(b) How much faster is the execution of the l_inc instruction in your modified design thanthe execution of the two instructions you listed in problem 1?Page 2 of 8

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 2004Page 3 of 8

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 20044. Pipelined Processor Design 20 PointsAssume that the register file is modified to add a second write port, with inputs WN2(selects the register to be written), WD2 (write data), and RegWrite2 (write enable). Modifythe pipelined processor datapath and control to implement the l_inc instruction .(a) Mark any changes to the datapath (including any additional hardware that you need) onthe diagram on the next page. In addition, show all control outputs in the table below:Instr.l_incRegDstALUOp1EX StageControl LinesALUOp0ALUSrcBranchMEM StageControl LinesMemReadMemWriteRegWriteWB StageControl LinesMemtoReg(b) Suppose that an additional write port cannot be added to the register file. Brieflydescribe how the l_inc instruction could still be implemented with the pipelineddesign. What impact would this change have on performance?Page 4 of 8

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 2004Page 5 of 8

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 20045. Data and Control Hazards 20 PointsAssume that the following sequence of MIPS instructions (including the new l_incinstruction) is executing on the modified pipeline design from Problem 3, but that thedesign is altered to perform forwarding, stalls, and flushing as required to deal with data andcontrol hazards.L: l_inc $2, 200($1)bne $1, $5, Ladd $7, $1, $4sw $8, 0($7)sub $7, $8, $7(a) Circle any data dependencies which exist between these instructions.(b) Mark any of the above instructions that will be stalled due to data hazards.(c) Assuming that the branch is taken, fill in the multicycle diagram shown below to showthe execution of the instruction sequence during one iteration, including stalls,forwarding, and flushes (if any). Shade active stages.Page 6 of 8

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 20046. Short Answers 10 PointsProvide a short answer for each of the following questions:(a) List three features of the Intel IA-32 (x86) Instruction Set Architecture that make itdifficult to implement.(b) List three different types of exceptions which can occur in a full implementation of theMIPS Instruction Set Architecture.(c) List two reasons why Virtual Memory is used in almost all modern computer systems.(d) How many levels of on-chip cache are common in current desktop computer systems?Page 7 of 8

<strong>ECE</strong> <strong>313</strong> <strong>Computer</strong> <strong>Organization</strong><strong>Name</strong><strong>FINAL</strong> <strong>EXAM</strong> <strong>December</strong> <strong>14</strong>, 20047. Cache Memories 20 PointsThe diagram below shows a direct-mapped cache memory design which contains 16 blocks.Each block stores one 32-bit word plus tag and valid bit.(a) How many bits will there be in the “Index” field of the address?(b) How many bits will there be in the “Tag” field of each address?(c) How many bits of storage will be required for this cache memory?(d) Assume that the is initially empty (i.e. a cold cache). Fill in the chart below to show thehits and misses encountered for each 32-bit word reference. Also, write the cachecontents in the diagram as the cache is updated.HitTagDataReference(word offset) Hit/MissTagV TagIndexByteOffset32 BitsDataBlock 0Block 1Block 2Block 3Block 4Block 5Block 6Block 7Block 8Block 9Block 10Block 11Block 12Block 13Block <strong>14</strong>Block 1534591610194934549174932=Page 8 of 8