Exercice 1 (VHDL)

Exercice 1 (VHDL)

Exercice 1 (VHDL)

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Exercice</strong> 1 (<strong>VHDL</strong>)Examen <strong>VHDL</strong> - Cours de R. Grisel - Durée : 1 heureDocuments autorisés : Cours, TD, TP exclusivementOn donne en annexe 4 fichiers <strong>VHDL</strong> qui sont : COMP1.VHD, COMP2.VHD, COMP3.VHD,MASTER.VHD.A) Expliquer le fonctionnement et le type de description des modèles <strong>VHDL</strong> des fichiers :COMP1.VHDCOMP2.VHDCOMP3.VHDB) Expliquer le fonctionnement du circuit MASTER.VHDC) Existe t'il d'autres manières de faire cette description <strong>VHDL</strong> ?.D) Compléter le chronogramme donné en annexe en faisant attention aux valeurs numériques dessignaux d’entrée.Note : Vous pouvez très bien dans un premier temps ne pas tenir compte des TPLH et TPHL,pour étudier uniquement la structure du circuit (dans ce cas vous ignorez les clause AFTER etGENERIC et GENERIC MAP) et si vous avez le temps revenir ensuite sur la structure avec ceque donnent les temps.

-- Fichier COMP1.VHD -----------------------library ieee;use ieee.std_logic_1164.all;entity COMP1 isgeneric (TPLH: time := 1 ns;TPHL: time := 1 ns);port (signal QN: out std_logic;signal A: in std_logic);end COMP1;architecture BEHAVIOR of COMP1 isbeginP1: process(A)variable STATE: std_logic;beginSTATE := not(A);if STATE = '1' thenQN

-- Fichier COMP2.VHDlibrary ieee;use ieee.std_logic_1164.all;entity COMP2 isgeneric (TPLH: time := 2 ns;TPHL: time := 3 ns);port (signal QN: out std_logic;signal A, B, C, D: in std_logic);end COMP2;architecture archCOMP2 of COMP2 iscomponent COMP1generic (TPLH: time;TPHL: time);port (QN: out std_logic;A: in std_logic);end component;signal STATE, NSTATE: std_logic;beginSTATE

-- Fichier MASTER.VHD ----------library ieee;use ieee.std_logic_1164.all;entity MASTER isport (VAL1, VAL2, VAL3: in std_logic;I1, I2, I3: in std_logic;nY7, nY6, nY5, nY4,nY3, nY2, nY1, nY0: out std_logic);end master;architecture STRUCTURAL of MASTER issignal nVAL1, EN, nI1, nI2, nI3: std_logic;component COMP1generic (TPLH: time := 1 ns;TPHL: time := 1 ns);port (QN: out std_logic;A: in std_logic);end component;component COMP2generic (TPLH: time := 2 ns;TPHL: time := 3 ns);port (QN: out std_logic;A, B, C, D: in std_logic);end component;component COMP3generic (TPLH: time := 1 ns;TPHL: time := 1 ns);port (QN: out std_logic;A, B, C: in std_logic);end component;beginU1 : COMP1 port map (nVAL1, VAL1);U2 : COMP3 generic map (3 ns, 5 ns)port map (EN, nVAL1, VAL2, VAL3);U3 : COMP1 port map (QN => nI1, A => I1);U4 : COMP1 port map (nI2, I2);U5 : COMP1 port map (nI3, I3);U6 : COMP2 generic map (1 ns, 1 ns)port map (nY0, nI1, nI2, nI3, EN);U7 : COMP2 port map (nY1, I1, nI2, nI3, EN);U8 : COMP2 port map (nY2, nI1, I2, nI3, EN);U9 : COMP2 port map (nY3, I1, I2, nI3, EN);U10: COMP2 port map (nY4, nI1, nI2, I3, EN);U11: COMP2 port map (nY5, I1, nI2, I3, EN);U12: COMP2 port map (nY6, nI1, I2, I3, EN);U13: COMP2 port map (nY7, I1, I2, I3, EN);end STRUCTURAL;

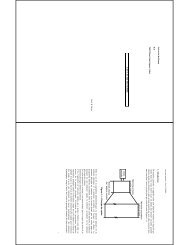

Project master123I1I2I3VAL1VAL2VAL3nY0nY1nY2nY3nY4nY5nY6nY7500.00 1000.00 1500.00 2000.00 2500.00 3000.00 3500.00 4000.00 4500.00 5000.00 5500.00 6000.00nsPage 1 / 1