Introducing the ARM Cortex-M0+ processor: The Ultimate in Low ...

Introducing the ARM Cortex-M0+ processor: The Ultimate in Low ...

Introducing the ARM Cortex-M0+ processor: The Ultimate in Low ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

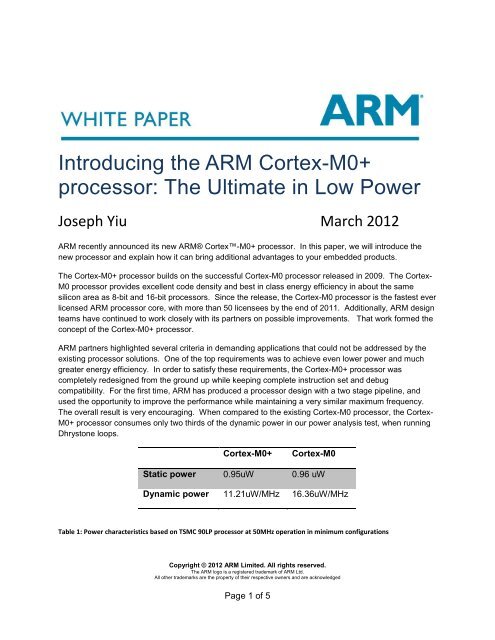

<strong>Introduc<strong>in</strong>g</strong> <strong>the</strong> <strong>ARM</strong> <strong>Cortex</strong>-<strong>M0+</strong><strong>processor</strong>: <strong>The</strong> <strong>Ultimate</strong> <strong>in</strong> <strong>Low</strong> PowerJoseph Yiu March 2012<strong>ARM</strong> recently announced its new <strong>ARM</strong>® <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong>. In this paper, we will <strong>in</strong>troduce <strong>the</strong>new <strong>processor</strong> and expla<strong>in</strong> how it can br<strong>in</strong>g additional advantages to your embedded products.<strong>The</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> builds on <strong>the</strong> successful <strong>Cortex</strong>-M0 <strong>processor</strong> released <strong>in</strong> 2009. <strong>The</strong> <strong>Cortex</strong>-M0 <strong>processor</strong> provides excellent code density and best <strong>in</strong> class energy efficiency <strong>in</strong> about <strong>the</strong> samesilicon area as 8-bit and 16-bit <strong>processor</strong>s. S<strong>in</strong>ce <strong>the</strong> release, <strong>the</strong> <strong>Cortex</strong>-M0 <strong>processor</strong> is <strong>the</strong> fastest everlicensed <strong>ARM</strong> <strong>processor</strong> core, with more than 50 licensees by <strong>the</strong> end of 2011. Additionally, <strong>ARM</strong> designteams have cont<strong>in</strong>ued to work closely with its partners on possible improvements. That work formed <strong>the</strong>concept of <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong>.<strong>ARM</strong> partners highlighted several criteria <strong>in</strong> demand<strong>in</strong>g applications that could not be addressed by <strong>the</strong>exist<strong>in</strong>g <strong>processor</strong> solutions. One of <strong>the</strong> top requirements was to achieve even lower power and muchgreater energy efficiency. In order to satisfy <strong>the</strong>se requirements, <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> wascompletely redesigned from <strong>the</strong> ground up while keep<strong>in</strong>g complete <strong>in</strong>struction set and debugcompatibility. For <strong>the</strong> first time, <strong>ARM</strong> has produced a <strong>processor</strong> design with a two stage pipel<strong>in</strong>e, andused <strong>the</strong> opportunity to improve <strong>the</strong> performance while ma<strong>in</strong>ta<strong>in</strong><strong>in</strong>g a very similar maximum frequency.<strong>The</strong> overall result is very encourag<strong>in</strong>g. When compared to <strong>the</strong> exist<strong>in</strong>g <strong>Cortex</strong>-M0 <strong>processor</strong>, <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> consumes only two thirds of <strong>the</strong> dynamic power <strong>in</strong> our power analysis test, when runn<strong>in</strong>gDhrystone loops.<strong>Cortex</strong>-<strong>M0+</strong><strong>Cortex</strong>-M0Static power 0.95uW 0.96 uWDynamic power 11.21uW/MHz 16.36uW/MHzTable 1: Power characteristics based on TSMC 90LP <strong>processor</strong> at 50MHz operation <strong>in</strong> m<strong>in</strong>imum configurationsCopyright © 2012 <strong>ARM</strong> Limited. All rights reserved.<strong>The</strong> <strong>ARM</strong> logo is a registered trademark of <strong>ARM</strong> Ltd.All o<strong>the</strong>r trademarks are <strong>the</strong> property of <strong>the</strong>ir respective owners and are acknowledgedPage 1 of 5

<strong>The</strong> lower power consumption of <strong>the</strong> <strong>processor</strong> is certa<strong>in</strong>ly important, but how about system level powerconsumption? By mov<strong>in</strong>g to a two stage pipel<strong>in</strong>e design, <strong>the</strong> branch shadow of <strong>the</strong> <strong>processor</strong> is reduced.As a result, <strong>the</strong> number of accesses to Flash memory is cut. Flash memory power often contributes <strong>the</strong>majority of <strong>the</strong> power consumed <strong>in</strong> a microcontroller so any reduction <strong>in</strong> Flash accesses has <strong>the</strong>n a verydirect effect on <strong>the</strong> overall power.Figure 1: Branch shadowSystem level features<strong>The</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> supports a new I/O <strong>in</strong>terface which allows s<strong>in</strong>gle cycle accesses and soenables faster I/O port operations. <strong>The</strong> <strong>processor</strong>’s I/O <strong>in</strong>terface is a generic 32-bit <strong>in</strong>terface to whichmicrocontroller vendors <strong>the</strong>n add <strong>the</strong>ir own I/O port peripherals. With this I/O <strong>in</strong>terface <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong><strong>processor</strong> can perform peripheral accesses faster than any of <strong>the</strong> popular microcontrollers.<strong>Cortex</strong>-<strong>M0+</strong>DataStrobeStartEnableOutputDisableOutputYSet DataOutput<strong>in</strong>cr ptrAssertstrobeDe-assertstrobeReadcharacterfrom ROMvia ptrNData==NULL?InstructionCycle SizeLoopSTR r4,[r1,#0] ;1 2ADDS r0,r0,#1 ;1 2STR r5,[r2,#4] ;1 2STR r6,[r2,#4] ;1 2; Loop entry po<strong>in</strong>tLDRB r4,[r0,#0] ;2 2CMP r4,#0 ;1 2BNE Loop ;2 2MCULoopcyclesLoop size(bytes)MSP430 12 2078K 10 148051 asm 15 12<strong>Cortex</strong>-<strong>M0+</strong> 9 14EndFigure 2: I/O <strong>in</strong>terface feature allows faster I/O operationsCopyright © 2012 <strong>ARM</strong> Limited. All rights reserved.<strong>The</strong> <strong>ARM</strong> logo is a registered trademark of <strong>ARM</strong> Ltd.All o<strong>the</strong>r trademarks are <strong>the</strong> property of <strong>the</strong>ir respective owners and are acknowledgedPage 2 of 5

S<strong>in</strong>ce <strong>the</strong> I/O <strong>in</strong>terface is part of <strong>the</strong> system’s memory map, <strong>the</strong> I/O register on this <strong>in</strong>terface can beaccessed with normal po<strong>in</strong>ters <strong>in</strong> C and does not require specific C language extension features such asspecial data types.Because accesses to <strong>the</strong> AMBA® AHB-Lite and <strong>the</strong> s<strong>in</strong>gle cycle I/O <strong>in</strong>terface can be madeconcurrently, <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> can fetch <strong>the</strong> next <strong>in</strong>structions while access<strong>in</strong>g <strong>the</strong> I/Os. Thisenables s<strong>in</strong>gle cycle I/O accesses to be susta<strong>in</strong>ed for as long as needed.Power-sensitive applications will also benefit from this improvement, by ei<strong>the</strong>r runn<strong>in</strong>g at lower speed for<strong>the</strong> same I/O toggl<strong>in</strong>g frequency, or by complet<strong>in</strong>g <strong>the</strong> I/O control more quickly, <strong>the</strong>n go<strong>in</strong>g faster <strong>in</strong>to asleep mode.<strong>The</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> also <strong>in</strong>cludes many useful features from <strong>the</strong> <strong>Cortex</strong>-M3 and <strong>Cortex</strong>-M4<strong>processor</strong>s previously not available <strong>in</strong> <strong>the</strong> <strong>Cortex</strong>-M0 <strong>processor</strong>. For example, it supports privileged andunprivileged execution levels, and a Memory Protection Unit (MPU) which is similar to that <strong>in</strong> <strong>the</strong> <strong>Cortex</strong>-M3 and <strong>Cortex</strong>-M4 <strong>processor</strong>s. <strong>The</strong> MPU is a programmable component with 8 programmable regions,and can be used by an OS to create access permission rules for various application tasks dynamicallydur<strong>in</strong>g run time. By us<strong>in</strong>g this mechanism, <strong>the</strong> design can prevent an application task from corrupt<strong>in</strong>gmemory space used by o<strong>the</strong>r tasks and <strong>the</strong> OS kernel.MPUMemoryI/O #2I/O #1I/O #0Data forOS kernelTask B<strong>Cortex</strong>-<strong>M0+</strong>Data forTask CData forTask BData forTask AOS kernelConfigFigure 3: Memory Protection Unit (MPU)Copyright © 2012 <strong>ARM</strong> Limited. All rights reserved.<strong>The</strong> <strong>ARM</strong> logo is a registered trademark of <strong>ARM</strong> Ltd.All o<strong>the</strong>r trademarks are <strong>the</strong> property of <strong>the</strong>ir respective owners and are acknowledgedPage 3 of 5

In addition, <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> supports vector table relocation, just like <strong>the</strong> <strong>Cortex</strong>-M3 and<strong>Cortex</strong>-M4 <strong>processor</strong>s. This allows easy reassignment of exception vectors at run time. All <strong>the</strong>se featuresare configurable options for silicon designers. In its m<strong>in</strong>imum configuration <strong>the</strong> silicon area of <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> is <strong>the</strong> same as <strong>the</strong> <strong>Cortex</strong>-M0 <strong>processor</strong>.For some silicon designers, more good news is that <strong>the</strong>y can very easily use <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong>with 16-bit Flash memories with m<strong>in</strong>imal impact to <strong>the</strong> performance or <strong>the</strong> system design. <strong>The</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> can be configured to generate <strong>in</strong>struction fetches as 16-bit ra<strong>the</strong>r than 32-bit accesses.Because most of <strong>the</strong> <strong>in</strong>structions <strong>in</strong> <strong>the</strong> <strong>ARM</strong>v6-M architecture are 16-bit, <strong>the</strong> system can still run withvery good performance.This focus on ma<strong>in</strong>ta<strong>in</strong><strong>in</strong>g a very low silicon area allows our partners to conceive size optimized solutionsthat address consumer and safety markets such as small sensors/actuators <strong>in</strong> factory automation,automotive and medical.Debug<strong>The</strong>re are also new features <strong>in</strong> <strong>the</strong> debug support. Beside <strong>the</strong> debug features <strong>in</strong> <strong>the</strong> exist<strong>in</strong>g <strong>Cortex</strong>-M0<strong>processor</strong>, <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> supports a Micro Trace Buffer (MTB) which provides simple<strong>in</strong>struction trace. <strong>The</strong> programmer allocates a small part of <strong>the</strong> system SRAM as a trace buffer and <strong>the</strong>MTB stores <strong>in</strong>struction flow <strong>in</strong>formation to <strong>the</strong> reserved SRAM as a circular buffer. After <strong>the</strong> <strong>processor</strong> ishalted, for example due to a breakpo<strong>in</strong>t, <strong>the</strong> debugger can <strong>the</strong>n retrieve <strong>the</strong> trace <strong>in</strong>formation via <strong>the</strong>widely adopted Serial Wire Debug (SWD) connection – this needs only two p<strong>in</strong>s – and <strong>the</strong>n reconstruct<strong>the</strong> recent execution history. <strong>The</strong> MTB can also support “one-shot” trigger<strong>in</strong>g.Figure 4 Instruction Trace support via MTB, already fully supported <strong>in</strong> Keil MDK-<strong>ARM</strong>Copyright © 2012 <strong>ARM</strong> Limited. All rights reserved.<strong>The</strong> <strong>ARM</strong> logo is a registered trademark of <strong>ARM</strong> Ltd.All o<strong>the</strong>r trademarks are <strong>the</strong> property of <strong>the</strong>ir respective owners and are acknowledgedPage 4 of 5

<strong>The</strong> Serial Wire Debug <strong>in</strong>terface <strong>in</strong> <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> can optionally <strong>in</strong>clude a feature calledMulti-drop Serial-Wire. This allows multiple Multi-drop Serial-Wire capable devices to share a s<strong>in</strong>gledebug connection, of particular benefit when build<strong>in</strong>g many-core SoC systems.Us<strong>in</strong>g <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong>-based microcontrollersFor software developers, <strong>the</strong> great news is that you can reuse all your exist<strong>in</strong>g software for <strong>Cortex</strong>-M0<strong>processor</strong>-based products. You can also use <strong>the</strong> same compiler suite, <strong>the</strong> same IDE and <strong>the</strong> samedebug adaptor. <strong>The</strong> <strong>in</strong>struction set of <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> is identical to that of <strong>Cortex</strong>-M0<strong>processor</strong>, and supports all features <strong>in</strong>cluded <strong>in</strong> <strong>the</strong> <strong>Cortex</strong>-M0 <strong>processor</strong>. <strong>The</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong>also supports <strong>the</strong> sleep mode features as <strong>in</strong> <strong>Cortex</strong>-M0 <strong>processor</strong>, and provides excellent <strong>in</strong>terruptprocess<strong>in</strong>g capability.Summary<strong>The</strong> <strong>ARM</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> <strong>in</strong>troduces a number of <strong>in</strong>novative new features to produce an MCU<strong>processor</strong> which offers unrivalled low power and energy efficiency toge<strong>the</strong>r with greater performance,simpler debug and memory protection. <strong>The</strong>se new features and capabilities are complemented by <strong>the</strong>recognized ease of use and upward compatibility features of <strong>the</strong> <strong>Cortex</strong>-M process series and provideMCU developers with a vast range of new application opportunities.Copyright © 2012 <strong>ARM</strong> Limited. All rights reserved.<strong>The</strong> <strong>ARM</strong> logo is a registered trademark of <strong>ARM</strong> Ltd.All o<strong>the</strong>r trademarks are <strong>the</strong> property of <strong>the</strong>ir respective owners and are acknowledgedPage 5 of 5