Introducing the ARM Cortex-M0+ processor: The Ultimate in Low ...

Introducing the ARM Cortex-M0+ processor: The Ultimate in Low ...

Introducing the ARM Cortex-M0+ processor: The Ultimate in Low ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

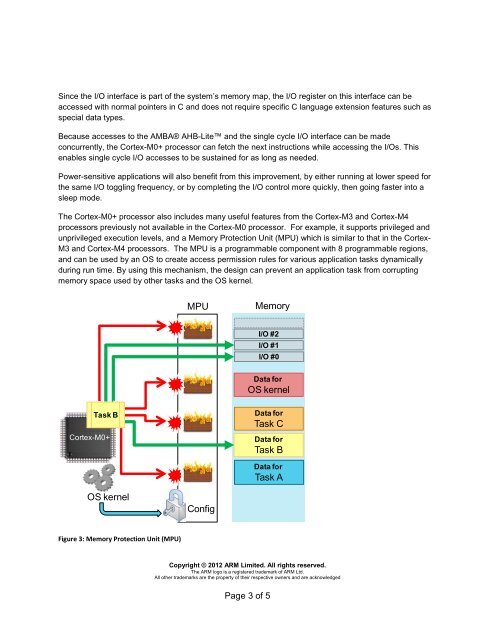

S<strong>in</strong>ce <strong>the</strong> I/O <strong>in</strong>terface is part of <strong>the</strong> system’s memory map, <strong>the</strong> I/O register on this <strong>in</strong>terface can beaccessed with normal po<strong>in</strong>ters <strong>in</strong> C and does not require specific C language extension features such asspecial data types.Because accesses to <strong>the</strong> AMBA® AHB-Lite and <strong>the</strong> s<strong>in</strong>gle cycle I/O <strong>in</strong>terface can be madeconcurrently, <strong>the</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> can fetch <strong>the</strong> next <strong>in</strong>structions while access<strong>in</strong>g <strong>the</strong> I/Os. Thisenables s<strong>in</strong>gle cycle I/O accesses to be susta<strong>in</strong>ed for as long as needed.Power-sensitive applications will also benefit from this improvement, by ei<strong>the</strong>r runn<strong>in</strong>g at lower speed for<strong>the</strong> same I/O toggl<strong>in</strong>g frequency, or by complet<strong>in</strong>g <strong>the</strong> I/O control more quickly, <strong>the</strong>n go<strong>in</strong>g faster <strong>in</strong>to asleep mode.<strong>The</strong> <strong>Cortex</strong>-<strong>M0+</strong> <strong>processor</strong> also <strong>in</strong>cludes many useful features from <strong>the</strong> <strong>Cortex</strong>-M3 and <strong>Cortex</strong>-M4<strong>processor</strong>s previously not available <strong>in</strong> <strong>the</strong> <strong>Cortex</strong>-M0 <strong>processor</strong>. For example, it supports privileged andunprivileged execution levels, and a Memory Protection Unit (MPU) which is similar to that <strong>in</strong> <strong>the</strong> <strong>Cortex</strong>-M3 and <strong>Cortex</strong>-M4 <strong>processor</strong>s. <strong>The</strong> MPU is a programmable component with 8 programmable regions,and can be used by an OS to create access permission rules for various application tasks dynamicallydur<strong>in</strong>g run time. By us<strong>in</strong>g this mechanism, <strong>the</strong> design can prevent an application task from corrupt<strong>in</strong>gmemory space used by o<strong>the</strong>r tasks and <strong>the</strong> OS kernel.MPUMemoryI/O #2I/O #1I/O #0Data forOS kernelTask B<strong>Cortex</strong>-<strong>M0+</strong>Data forTask CData forTask BData forTask AOS kernelConfigFigure 3: Memory Protection Unit (MPU)Copyright © 2012 <strong>ARM</strong> Limited. All rights reserved.<strong>The</strong> <strong>ARM</strong> logo is a registered trademark of <strong>ARM</strong> Ltd.All o<strong>the</strong>r trademarks are <strong>the</strong> property of <strong>the</strong>ir respective owners and are acknowledgedPage 3 of 5