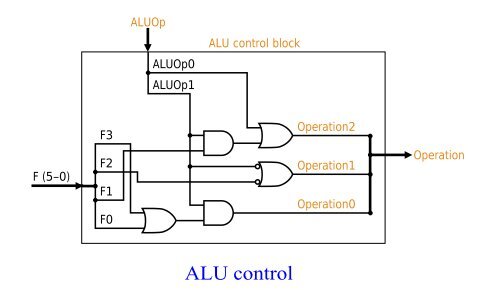

ALU control - Weblearn.hs-bremen.de

ALU control - Weblearn.hs-bremen.de

ALU control - Weblearn.hs-bremen.de

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

InputsOp5Op4Op3Op2Op1Op0R-format Iw sw beqOutputsRegDst<strong>ALU</strong>SrcMemtoRegRegWriteMemReadMemWriteBranch<strong>ALU</strong>Op1<strong>ALU</strong>OpO

2Memory addresscomputation<strong>ALU</strong>SrcA = 1<strong>ALU</strong>SrcB = 10<strong>ALU</strong>Op = 00StartInstruction fetch0MemRead<strong>ALU</strong>SrcA = 0IorD = 0IRWrite<strong>ALU</strong>SrcB = 01<strong>ALU</strong>Op = 00PCWritePCSource = 006(Op = 'LW') or (Op = 'SW')Execution<strong>ALU</strong>SrcA =1<strong>ALU</strong>SrcB = 00<strong>ALU</strong>Op= 108(Op = R-type)Branchcompletion<strong>ALU</strong>SrcA = 1<strong>ALU</strong>SrcB = 00<strong>ALU</strong>Op = 01PCWriteCondPCSource = 01Instruction <strong>de</strong>co<strong>de</strong>/register fetch1(Op = 'BEQ')9<strong>ALU</strong>SrcA = 0<strong>ALU</strong>SrcB = 11<strong>ALU</strong>Op = 00(Op = 'J')JumpcompletionPCWritePCSource = 103(Op = 'LW')Memoryaccess(Op = 'SW')5Memoryaccess7R-type completionMemReadIorD = 1MemWriteIorD = 1RegDst = 1RegWriteMemtoReg = 04Write-back stepRegDst= 0RegWriteMemtoReg=1

Control logicInputsOutputsPCWritePCWriteCondIorDMemReadMemWriteIRWriteMemtoRegPCSource<strong>ALU</strong>Op<strong>ALU</strong>SrcB<strong>ALU</strong>SrcARegWriteRegDstNS3NS2NS1NS0Op5Op4Op3Op2Op1Op0S3S2S1S0Instruction registeropco<strong>de</strong> fieldState register

Op5Op4Op3Op2Op1Op0S3S2S1S0PCWritePCWriteCondIorDMemReadMemWriteIRWriteMemtoRegPCSource1PCSource0<strong>ALU</strong>Op1<strong>ALU</strong>Op0<strong>ALU</strong>SrcB1<strong>ALU</strong>SrcB0<strong>ALU</strong>SrcARegWriteRegDstNS3NS2NS1NS0

PLA or ROM1StateAd<strong>de</strong>rMux3 2 1 0AddrCtl0Dispatch ROM 2Dispatch ROM 1Address select logicOpInstruction registeropco<strong>de</strong> field

Control unitMicroco<strong>de</strong> memoryInputOutputsPCWritePCWriteCondIorDMemReadMemWriteIRWriteBWriteMemtoRegPCSource<strong>ALU</strong>Op<strong>ALU</strong>SrcB<strong>ALU</strong>SrcARegWriteRegDstAddrCtlDatapath1Microprogram counterAd<strong>de</strong>rAddress select logicOp[5–0]Instruction registeropco<strong>de</strong> field