VHDL vs. Verilog - Weblearn.hs-bremen.de - Hochschule Bremen

VHDL vs. Verilog - Weblearn.hs-bremen.de - Hochschule Bremen

VHDL vs. Verilog - Weblearn.hs-bremen.de - Hochschule Bremen

- Keine Tags gefunden...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>Anke KampFrank SchmidtFlorian ThiemFachbereich Elektrotechnik und Informatik Hoc<strong>hs</strong>chule <strong>Bremen</strong>RST-L Prof. Risse8. Januar 2008<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>1 / 83

Einleitung Grundlagen Programbeispiele Fazit1 EinleitungAnfängeProgrammablaufKomplexität2 GrundlagenDatentypenFunktionenModularisierungZeitverhaltenOperatorenKonstrukte auf Gatterebene3 Programbeispiele<strong>VHDL</strong> Enco<strong>de</strong>r<strong>Verilog</strong> Deco<strong>de</strong>r4 FazitÜbersicht<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>2 / 83

Einleitung Grundlagen Programbeispiele FazitHardwarebeschreibungssprachenHDL - Hardware Description Language<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>3 / 83

Einleitung Grundlagen Programbeispiele FazitHardwarebeschreibungssprachenHDL - Hardware Description LanguageIntegrierte Schaltungen durch eine formale SyntaxZeitliche Abläufe und Parallelitäten sind beschreibbarSimulierung durch EDA - Werkzeuge(Electronic Design Automation)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>3 / 83

Einleitung Grundlagen Programbeispiele FazitHardwarebeschreibungssprachenHDL - Hardware Description LanguageIntegrierte Schaltungen durch eine formale SyntaxZeitliche Abläufe und Parallelitäten sind beschreibbarSimulierung durch EDA - Werkzeuge(Electronic Design Automation)<strong>VHDL</strong> in Europa und <strong>Verilog</strong> in <strong>de</strong>n USA<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>3 / 83

Einleitung Grundlagen Programbeispiele FazitEntwicklungsebenen1 Systemebene/Algorithmische EbeneGrobes algorithmisches Mo<strong>de</strong>lModulierung in C/C++, MATLAB, <strong>VHDL</strong>, <strong>Verilog</strong>2 Register-Transfer-Ebene3 GatterebeneBeschreibung kommunizieren<strong>de</strong>r Register und Logiceinheiten, mitDatenstrukturen und DatenüsseBeschreibung durch Logic-Gatter und Flipops4 SchaltkreisebeneBeschreibung durch Bauteile, z.B. TransistorenSimulation nicht praktiziert<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>4 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>VHDL</strong><strong>VHDL</strong> -> VHSIC Hardware Description LanguageVHSIC -> Very High Speed Integrated Circuit<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>5 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>VHDL</strong>Initiiert durch das amerikanische Verteidigungsministerium(Department of Defense - DoD)Anlehnung an ADA<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>6 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>VHDL</strong>Initiiert durch das amerikanische Verteidigungsministerium(Department of Defense - DoD)Anlehnung an ADAStandardisierte, einheitliche Sprache zur Beschreibung o<strong>de</strong>rDokumentation von HardwareEs wur<strong>de</strong> von Beginn an als oener Standard entwickelt<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>6 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>VHDL</strong>Initiiert durch das amerikanische Verteidigungsministerium(Department of Defense - DoD)Anlehnung an ADAStandardisierte, einheitliche Sprache zur Beschreibung o<strong>de</strong>rDokumentation von HardwareEs wur<strong>de</strong> von Beginn an als oener Standard entwickelt<strong>VHDL</strong>-Version 7.2 wur<strong>de</strong> 1987 als IEEE 1076-1987 standardisiert1993 Überarbeitung als IEEE 1076-1993 standardisiert<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>6 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>VHDL</strong>Verschie<strong>de</strong>ne Ansätze um beson<strong>de</strong>re Probleme zu lösenSimulation <strong>de</strong>s Zeitverhaltens auf Gatterebene durch <strong>de</strong>n VITALStandardMathematisches Package zur Simulation von Gleitpunktzahlen undkomplexe Zahlen<strong>VHDL</strong>-AMS zur analogen SchaltungssimulationUnd viele mehr<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>7 / 83

Einleitung Grundlagen Programbeispiele FazitAussichten von <strong>VHDL</strong>Umfangreichen Überarbeitung mit <strong>de</strong>r Bezeichnung <strong>VHDL</strong>-200X zuerwartenZiel dabei:synthesefähige Umsetzung von Gleitpunktzahlen<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>8 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>Verilog</strong><strong>Verilog</strong> -> Verifying Logic<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>9 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>Verilog</strong>Als proprietäre Sprache durch die Firma Gateway DesignAutomation Inc.Anlehnung an C<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>10 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>Verilog</strong>Als proprietäre Sprache durch die Firma Gateway DesignAutomation Inc.Anlehnung an C1987 schneller und ezienter <strong>Verilog</strong>-XL Simulator rausgekommenFür die Schaltungsbeschreibung auf GatterebeneBeschreibung auf <strong>de</strong>r Register-Transfer-Ebene möglich<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>10 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>Verilog</strong>Als proprietäre Sprache durch die Firma Gateway DesignAutomation Inc.Anlehnung an C1987 schneller und ezienter <strong>Verilog</strong>-XL Simulator rausgekommenFür die Schaltungsbeschreibung auf GatterebeneBeschreibung auf <strong>de</strong>r Register-Transfer-Ebene möglich1989 Gateway von Firma Ca<strong>de</strong>nce Design Systems aufgekauft1995 als IEEE 1364-1995 standardisiertLetzte Version IEEE 1364-2001 eine überarbeitete Version von '95<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>10 / 83

Einleitung Grundlagen Programbeispiele FazitAnfänge von <strong>Verilog</strong>Beson<strong>de</strong>rheiten1988 release <strong>de</strong>s ersten Logigsynthesewerkzeug durch FirmaSynopsys dadurch wur<strong>de</strong> die Beschreibung aufRegister-Transfer-Ebene in eine Gatterrealisierung überführbar<strong>Verilog</strong>-XL Simulator häug als Sign-O-Simulator verwen<strong>de</strong>t<strong>Verilog</strong>-AMS zur analogen SchaltungssimulationUnd viele mehr<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>11 / 83

Einleitung Grundlagen Programbeispiele FazitAussichten von <strong>Verilog</strong>2002 release von System<strong>Verilog</strong> 3.0 (HDVL)Hardware Beschreibungs-und VerikationsspracheZiel dabei:Ermöglicht nun erstmalig die Verizierung <strong>de</strong>r Hardware<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>12 / 83

Einleitung Grundlagen Programbeispiele FazitEntwicklungsablaufQuelle: Ott, Wil<strong>de</strong>rotter, A Designer's Gui<strong>de</strong> To <strong>VHDL</strong> Synthesis, Kluwer Aca<strong>de</strong>micPublishers, Dordrecht, 1994<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>13 / 83

Einleitung Grundlagen Programbeispiele FazitSimulationsumgebungQuelle: Kessel, Bartholomä, Entwurf von digitalen Schaltungen und Systemen mitHDLs und FPGAs, Ol<strong>de</strong>nbourg Verlag München Wien, 2006<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>14 / 83

Einleitung Grundlagen Programbeispiele FazitTür-ÖnerListing 1: <strong>VHDL</strong>1 −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− 1 −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−2 Co<strong>de</strong> aus ' V e r i l o g F o r D i g i t a l Design ' 2 Co<strong>de</strong> aus ' V e r i l o g For D i g i t a l Design '3 von Vahid und Lysecky ,3 von Vahid und Lysecky ,4 John Wiley & Sons , I n c . , 20074 John Wiley & Sons , I n c . , 20075 −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− 5 −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−67 l i b r a r y i e e e ;8 u s e i e e e . std_logic_1164 . a l l ;910 E n t i t y DoorOpener i s11 P o r t (C , H, P : i n s t d _ l o g i c ;12 F : o u t s t d _ l o g i c ) ;13 end DoorOpener ;1415 A r c h i t e c t u r e beh o f DoorOpener i s16 b e g i n17 P r o c e s s (C , H, P)18 b e g i n19 F

Einleitung Grundlagen Programbeispiele Fazit1 EinleitungAnfängeProgrammablaufKomplexität2 GrundlagenDatentypenFunktionenModularisierungZeitverhaltenOperatorenKonstrukte auf Gatterebene3 Programbeispiele<strong>VHDL</strong> Enco<strong>de</strong>r<strong>Verilog</strong> Deco<strong>de</strong>r4 FazitÜbersicht<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>16 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong> Entity1 e n t i t y entityName i s2 [ g e n e r i c ( L i s t e −<strong>de</strong>r−g e n e r i c s −und−<strong>de</strong>ren −Typen ) ; ]3 [ port ( L i s t e −<strong>de</strong>r−A n s c h l u s s p o r t s −und−<strong>de</strong>ren −Typen ; ]4 [ l o c a l d e c l a r a t i o n s ; ]56 [ begin7 p a s s i v e statements ]8 end [ e n t i t y ] [ entityName ] ;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>17 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>Verilog</strong> Module1 module moduleName ( p o r t L i s t ) ;2 port d e c l a r a t i o n ;3 [ o t h e r d e c l a r a t i o n ; ] // z . B . l o k a l e V a r i a b l e n45 statements ;6 endmodule<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>19 / 83

Einleitung Grundlagen Programbeispiele FazitDatentypen Bei<strong>de</strong>Gängige Datentypen gleich, z.B.booleanbitskalareiesskommacharactersinteger im Bereich (−(2 31 − 1) bis (2 31 − 1))<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>20 / 83

Einleitung Grundlagen Programbeispiele FazitDatentypen <strong>Verilog</strong>SchlüsselwortwireregBeschreibungEinfache Verbindung zwischen Schaltungselemeten,Leitung, VariableVerbindung mit Speicherverhalten, Ziel fürZuweisungen, VariableTabelle: Datentypen in <strong>Verilog</strong><strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>21 / 83

Einleitung Grundlagen Programbeispiele FazitDatentypen <strong>Verilog</strong>Typ Syntax BeispielLeitung o<strong>de</strong>r Variablemit einerBreite von einemnamereg enable;BitBus o<strong>de</strong>r Variablemit einer Breitevon n Bit[n-1:0] namewire [3:0] nibble;k Busse mit jeweilsn Bit [n-1:0] name [0:k-1] wire [2:0] activity [0:1];Speicher mitk Speicherzellen<strong>de</strong>r Breite n Bit[n-1:0] name [0:k-1]reg [7:0] memory [0:31];Zugri: memory[4][2]<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>22 / 83

Einleitung Grundlagen Programbeispiele Fazitstd_ulogic<strong>VHDL</strong> Datentypen1: Wert 1; stark0: Wert 0; starkW: unbekannt; schwachL: Wert 0; schwachH: Wert 1; schwach(-): don't careStd_logicZ: tristate/hochohmig; schwachX: unbekannt; stark; Ergebnis fehlerhaft entstan<strong>de</strong>nU: un<strong>de</strong>niert; uninitialisiert o<strong>de</strong>r unbekanntes Signal< datentyp > _vector; z.B. Bit_vector(3 downto 0)Records (aus bestehen<strong>de</strong>n Typen zusammengesetzter Datentyp)Eigene Typ<strong>de</strong>nitionen per type name is (liste, <strong>de</strong>r, werte)Typeinschränkung per subtype<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>23 / 83

Einleitung Grundlagen Programbeispiele FazitFunktionen <strong>VHDL</strong>functionprocedure<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>24 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong> function1 f u n c t i o n funcName ( p a r a m e t e r L i s t e ) r e t u r n type i s2 −− D e k l a r a t i o n ;34 begin5 −− S e q u e n z i e l l e Anweisungen6 r e t u r n var ;7 end funcName ;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>25 / 83

Einleitung Grundlagen Programbeispiele Fazitfunction <strong>VHDL</strong>Aufruf mit keinem bis mehreren ArgumentenArgumentenklasse: Signale o<strong>de</strong>r KonstantenArgumente wer<strong>de</strong>n nur gelesen, daher Modus 'in' nicht unbedingtanzugebenSchlüsselwort return unter Angabe <strong>de</strong>s Rückgabewertes zumverlassennur ein RückgabewertKann überall verwen<strong>de</strong>t wer<strong>de</strong>n, wenn return Typ erlaubt istAlle sequenziellen Anweisungen ausser wait erlaubt<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>26 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong> procedure1 procedure procName ( p a r a m e t e r l i s t e ) i s2 −− D e k l a r a t i o n ;34 begin5 −− s e q u e n z i e l l e Anweisungen6 end procName ;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>27 / 83

Einleitung Grundlagen Programbeispiele Fazitprocedure <strong>VHDL</strong>Aufruf mit mehreren ArgumentenArgumentenklasse: Signale, Konstanten o<strong>de</strong>r Variablenin, out, inout bei Argumenten möglichWer<strong>de</strong>n bis zu einem return o<strong>de</strong>r bis zum En<strong>de</strong> (entsprechen<strong>de</strong>inem Prozess mit sensitivity-list) abgearbeitetKein bis viele RückgabewerteKann überall verwen<strong>de</strong>t wer<strong>de</strong>n, wenn return Typ erlaubt ist<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>28 / 83

Einleitung Grundlagen Programbeispiele Fazitprocedure <strong>VHDL</strong>Ein wait darf enthalten sein, wenn nicht von einem Prozess mitSensitivity-Liste aufgerufenAlle sequenziellen Anweisungen können Genutz wer<strong>de</strong>nBei paralleler Verwendung wird sie immer ausgeführt, wennArgument 'in' o<strong>de</strong>r 'inout' sich än<strong>de</strong>rt<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>29 / 83

Einleitung Grundlagen Programbeispiele FazitFunktionen <strong>Verilog</strong>functiontask<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>30 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>Verilog</strong> task1 task taskName ;2 d e c l a r a t i o n ;34 statement ;5 endtask<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>31 / 83

Einleitung Grundlagen Programbeispiele Fazittask in <strong>Verilog</strong>Darf Zeitverzögerungen aufweiseninput und output erlaubtEigenständiger Aufruf z.B. mit tsk(out, in1);<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>32 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>Verilog</strong> function1 f u n c t i o n [ range ] functionName ;2 d e c l a r a t i o n ;34 statement ;5 endfunction<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>33 / 83

Einleitung Grundlagen Programbeispiele Fazitfunction in <strong>Verilog</strong>Darf keine Zeitverzögerung aufweisen, also Simulationszeit NullMin<strong>de</strong>stens ein input aber kein output, Returnwert ersetzt <strong>de</strong>nFunktionsnamenAufruf ist Teil einer Anweisung, z.B. i=func(a, b); dabei ist func<strong>de</strong>r Name<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>34 / 83

Einleitung Grundlagen Programbeispiele FazitGrundlagenFrank übernimmt nun und berichtet von <strong>de</strong>r wun<strong>de</strong>rschönenWelt <strong>de</strong>r OperatorenFliegen<strong>de</strong>r Wec<strong>hs</strong>el, please wait...<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>35 / 83

Einleitung Grundlagen Programbeispiele FazitModularisierungBei <strong>de</strong>r Mo<strong>de</strong>llierung eines Systems wird dieses in verschie<strong>de</strong>neModule zerlegt, und diese Module dann getrennt voneinan<strong>de</strong>rentwickelt.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>36 / 83

Einleitung Grundlagen Programbeispiele FazitModularisierungBei <strong>de</strong>r Mo<strong>de</strong>llierung eines Systems wird dieses in verschie<strong>de</strong>neModule zerlegt, und diese Module dann getrennt voneinan<strong>de</strong>rentwickelt.Modulweise kann das Mo<strong>de</strong>ll von <strong>de</strong>r Verhaltensebene hin zurGatter- und Transistorebene entwickelt wer<strong>de</strong>n, da die Module nurüber ihre Schnittstellen kommunizieren.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>36 / 83

Einleitung Grundlagen Programbeispiele FazitModularisierungBei <strong>de</strong>r Mo<strong>de</strong>llierung eines Systems wird dieses in verschie<strong>de</strong>neModule zerlegt, und diese Module dann getrennt voneinan<strong>de</strong>rentwickelt.Modulweise kann das Mo<strong>de</strong>ll von <strong>de</strong>r Verhaltensebene hin zurGatter- und Transistorebene entwickelt wer<strong>de</strong>n, da die Module nurüber ihre Schnittstellen kommunizieren.Es gibt dabei vier Abstraktionsebenen:Verhaltensebene: enthält Schleifen (for, while), Abfragen (if, case)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>36 / 83

Einleitung Grundlagen Programbeispiele FazitModularisierungBei <strong>de</strong>r Mo<strong>de</strong>llierung eines Systems wird dieses in verschie<strong>de</strong>neModule zerlegt, und diese Module dann getrennt voneinan<strong>de</strong>rentwickelt.Modulweise kann das Mo<strong>de</strong>ll von <strong>de</strong>r Verhaltensebene hin zurGatter- und Transistorebene entwickelt wer<strong>de</strong>n, da die Module nurüber ihre Schnittstellen kommunizieren.Es gibt dabei vier Abstraktionsebenen:Verhaltensebene: enthält Schleifen (for, while), Abfragen (if, case)Register-Transfer-Ebene: enthält Zuweisungen, Operatoren<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>36 / 83

Einleitung Grundlagen Programbeispiele FazitModularisierungBei <strong>de</strong>r Mo<strong>de</strong>llierung eines Systems wird dieses in verschie<strong>de</strong>neModule zerlegt, und diese Module dann getrennt voneinan<strong>de</strong>rentwickelt.Modulweise kann das Mo<strong>de</strong>ll von <strong>de</strong>r Verhaltensebene hin zurGatter- und Transistorebene entwickelt wer<strong>de</strong>n, da die Module nurüber ihre Schnittstellen kommunizieren.Es gibt dabei vier Abstraktionsebenen:Verhaltensebene: enthält Schleifen (for, while), Abfragen (if, case)Register-Transfer-Ebene: enthält Zuweisungen, OperatorenGatterebene: enthält logische Gatter (und UDP bei <strong>Verilog</strong>)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>36 / 83

Einleitung Grundlagen Programbeispiele FazitModularisierungBei <strong>de</strong>r Mo<strong>de</strong>llierung eines Systems wird dieses in verschie<strong>de</strong>neModule zerlegt, und diese Module dann getrennt voneinan<strong>de</strong>rentwickelt.Modulweise kann das Mo<strong>de</strong>ll von <strong>de</strong>r Verhaltensebene hin zurGatter- und Transistorebene entwickelt wer<strong>de</strong>n, da die Module nurüber ihre Schnittstellen kommunizieren.Es gibt dabei vier Abstraktionsebenen:Verhaltensebene: enthält Schleifen (for, while), Abfragen (if, case)Register-Transfer-Ebene: enthält Zuweisungen, OperatorenGatterebene: enthält logische Gatter (und UDP bei <strong>Verilog</strong>)Transistorebene: enthält Transistoren und Leitungen (nur <strong>Verilog</strong>)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>36 / 83

Einleitung Grundlagen Programbeispiele FazitModul bei <strong>Verilog</strong>Bei <strong>Verilog</strong> sind Module auch als Modul bezeichnet:module full_ad<strong>de</strong>r(a, b, c_in, sum, c_out);input a, b, c_in;output sum, c_out;reg tmp1, tmp2, tmp3;half_ad<strong>de</strong>r ha1(a, b, tmp1, tmp2); // calling modulehalf_ad<strong>de</strong>r ha2(tmp1, c_in, sum, tmp3); // half_ad<strong>de</strong>ror(c_out, tmp2, tmp3);endmodule<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>37 / 83

Einleitung Grundlagen Programbeispiele FazitKomponente bei <strong>VHDL</strong>Bei <strong>VHDL</strong> können an<strong>de</strong>re Entities aufgerufen wer<strong>de</strong>n, wenn sie in<strong>de</strong>r Architektur als Komponenten mit Portliste <strong>de</strong>klariert wer<strong>de</strong>n:−− Deklaration <strong>de</strong>r Komponente:component NAND2port (A, B: in STD_LOGIC; Z: out STD_LOGIC);end component;−− Instantiierung <strong>de</strong>r Komponente:N1: NAND2 port map (S1, S2, S3);Dadurch wird Signal S1 mit Port A assoziiert, S2 mit Port B undS3 mit Port Z.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>38 / 83

Einleitung Grundlagen Programbeispiele FazitPakete bei <strong>VHDL</strong>Bei <strong>VHDL</strong> können Deklarationen, die man benötigt, auch zuPaketen (package) zusammmengefasst wer<strong>de</strong>n, die man mit usein <strong>de</strong>n Co<strong>de</strong> einbin<strong>de</strong>n kann:use WORK.SYNTH_PACK.all; −− Alle Deklarationen aus <strong>de</strong>m−− Paket SYNTH_PACK einbin<strong>de</strong>npackage PROGRAM_PACK isconstant PROP_DELAY: TIME; −− zurückgehaltene Konstantefunction "and" (L, R: MVL) return MVL;end package PROGRAM_PACK;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>39 / 83

Einleitung Grundlagen Programbeispiele FazitPakete bei <strong>VHDL</strong>Bei <strong>VHDL</strong> können Deklarationen, die man benötigt, auch zuPaketen (package) zusammmengefasst wer<strong>de</strong>n, die man mit usein <strong>de</strong>n Co<strong>de</strong> einbin<strong>de</strong>n kann:use WORK.SYNTH_PACK.all; −− Alle Deklarationen aus <strong>de</strong>m−− Paket SYNTH_PACK einbin<strong>de</strong>npackage PROGRAM_PACK isconstant PROP_DELAY: TIME; −− zurückgehaltene Konstantefunction "and" (L, R: MVL) return MVL;end package PROGRAM_PACK;Ein Paketkörper ist nur nötig, wenn im Paket selbst Konstantenzurückgehalten wer<strong>de</strong>n o<strong>de</strong>r Unterprogramme <strong>de</strong>klariert wur<strong>de</strong>n, dienun Inhalte brauchen.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>39 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>Verilog</strong>-Zeitverhalten: CompilerdirektiveIn <strong>Verilog</strong> wird im Co<strong>de</strong> in Zeiteinheiten gerechnet, die mit <strong>de</strong>rCompilerdirektive 'timescale festgelegt wer<strong>de</strong>n:' timescale 1 ns / 100 psJe<strong>de</strong> Zeiteinheit dauert dann 1 ns, und Zeitbereiche kleiner als 100ps wer<strong>de</strong>n gerun<strong>de</strong>t.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>40 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>Verilog</strong>-Zeitverhalten: VerhaltensebeneEs kann mehrere always- und initial-Blöcke geben.always@(posedge Clk)beginend<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>41 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>Verilog</strong>-Zeitverhalten: VerhaltensebeneEs kann mehrere always- und initial-Blöcke geben.always@(posedge Clk)beginendalwayswait (Set == 1)beginwait (Set == 0)end<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>41 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>Verilog</strong>-Zeitverhalten: VerhaltensebeneEs kann mehrere always- und initial-Blöcke geben.always@(posedge Clk)beginendalwayswait (Set == 1)beginwait (Set == 0)endinitialbeginend<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>41 / 83

Einleitung Grundlagen Programbeispiele FazitVerzögerungenCo<strong>de</strong> wird normalerweise sofort ausgeführt, kann aber aufverschie<strong>de</strong>ne Arten verzögert wer<strong>de</strong>n:#5 rst = 1'b0;rst = #5 1'b0;Im ersten Fall wird die Ausführung um 5 Zeiteinheiten verzögert, imzweiten die Datenübernahme.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>42 / 83

Einleitung Grundlagen Programbeispiele FazitVerzögerungenCo<strong>de</strong> wird normalerweise sofort ausgeführt, kann aber aufverschie<strong>de</strong>ne Arten verzögert wer<strong>de</strong>n:#5 rst = 1'b0;rst = #5 1'b0;Im ersten Fall wird die Ausführung um 5 Zeiteinheiten verzögert, imzweiten die Datenübernahme.Q = @(posedge Clk) D;Erst bei steigen<strong>de</strong>r Taktanke von Clk wer<strong>de</strong>n die Datenübernommen.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>42 / 83

Einleitung Grundlagen Programbeispiele FazitZuweisungen und GabelungBlockieren<strong>de</strong> Zuweisungen mit = wer<strong>de</strong>n als Ganzes ausgeführt, beinichtblockieren<strong>de</strong>n mit

Einleitung Grundlagen Programbeispiele FazitZuweisungen und GabelungBlockieren<strong>de</strong> Zuweisungen mit = wer<strong>de</strong>n als Ganzes ausgeführt, beinichtblockieren<strong>de</strong>n mit

Einleitung Grundlagen Programbeispiele FazitKontinuierliche ZuordnungMit assign (und force) kann man Werte kontinuierlich zuordnen:assign Z=Aassign A=BBis zum <strong>de</strong>assign (o<strong>de</strong>r release) sind diese Werte dannkontinuierlich zugeordnet und können per einfacher Zuweisung mit= o<strong>de</strong>r

Einleitung Grundlagen Programbeispiele FazitKontinuierliche ZuordnungMit assign (und force) kann man Werte kontinuierlich zuordnen:assign Z=Aassign A=BBis zum <strong>de</strong>assign (o<strong>de</strong>r release) sind diese Werte dannkontinuierlich zugeordnet und können per einfacher Zuweisung mit= o<strong>de</strong>r

Einleitung Grundlagen Programbeispiele FazitGatterverzögerungenAuch Gattern kann man Verzögerungen zuordnen:and #4 (out1, a, b)xor #(3,5) (out2, a, b)Bei Angabe einer Verzögerung gilt diese für alle Schaltungen <strong>de</strong>sGatters, bei Angabe von zweien gilt die erste für steigen<strong>de</strong> und diezweite für fallen<strong>de</strong> Flanken.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>45 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong>-ZeitverhaltenBei <strong>VHDL</strong> entsprechen <strong>de</strong>n always-Statements die Prozesse. Je<strong>de</strong>rProzess hat seine Sensitivitätsliste von Signalen, bei <strong>de</strong>renÄn<strong>de</strong>rung er startet:process edge_di(q, d, clk , rst )beginend<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>46 / 83

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong>-ZeitverhaltenBei <strong>VHDL</strong> entsprechen <strong>de</strong>n always-Statements die Prozesse. Je<strong>de</strong>rProzess hat seine Sensitivitätsliste von Signalen, bei <strong>de</strong>renÄn<strong>de</strong>rung er startet:process edge_di(q, d, clk , rst )beginendEine Verzögerung wird hier durch eine explizite Zeitangabe erklärt:Z

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong>-ZeitverhaltenBei <strong>VHDL</strong> entsprechen <strong>de</strong>n always-Statements die Prozesse. Je<strong>de</strong>rProzess hat seine Sensitivitätsliste von Signalen, bei <strong>de</strong>renÄn<strong>de</strong>rung er startet:process edge_di(q, d, clk , rst )beginendEine Verzögerung wird hier durch eine explizite Zeitangabe erklärt:Z

Einleitung Grundlagen Programbeispiele Fazit<strong>VHDL</strong>: waitAusser<strong>de</strong>m gibt es mit wait eine Möglichkeit, auf verschie<strong>de</strong>neArten von Vorkommnissen zu warten:wait on A, B, C;wait until A = B;wait for 10 ns;wait on CLOCK for 20 ns;wait until SUM > 100 for 50 ns;wait on CLOCK until SUM > 100;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>47 / 83

Einleitung Grundlagen Programbeispiele FazitOperatorenArithmetische OperatorenLogische OperatorenVergleic<strong>hs</strong>operatorenSchiebeoperatorenZusammenfügungsoperatorenKonditionaler Operator (nur <strong>Verilog</strong>)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>48 / 83

Einleitung Grundlagen Programbeispiele FazitArithmetische OperatorenGrundrechenarten (+, -, *, /)Die Grundrechenarten können auch auf Bitvektoren angewen<strong>de</strong>twer<strong>de</strong>n, die dann als Binärzahlen interpretiert wer<strong>de</strong>n.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>49 / 83

Einleitung Grundlagen Programbeispiele FazitArithmetische OperatorenGrundrechenarten (+, -, *, /)Die Grundrechenarten können auch auf Bitvektoren angewen<strong>de</strong>twer<strong>de</strong>n, die dann als Binärzahlen interpretiert wer<strong>de</strong>n.Absolutwert (ABS) und Exponentiation (**) bei <strong>VHDL</strong><strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>49 / 83

Einleitung Grundlagen Programbeispiele FazitArithmetische OperatorenGrundrechenarten (+, -, *, /)Die Grundrechenarten können auch auf Bitvektoren angewen<strong>de</strong>twer<strong>de</strong>n, die dann als Binärzahlen interpretiert wer<strong>de</strong>n.Absolutwert (ABS) und Exponentiation (**) bei <strong>VHDL</strong>Modulo (% bei <strong>Verilog</strong>, MOD, REM bei <strong>VHDL</strong>)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>49 / 83

Einleitung Grundlagen Programbeispiele FazitArithmetische OperatorenGrundrechenarten (+, -, *, /)Die Grundrechenarten können auch auf Bitvektoren angewen<strong>de</strong>twer<strong>de</strong>n, die dann als Binärzahlen interpretiert wer<strong>de</strong>n.Absolutwert (ABS) und Exponentiation (**) bei <strong>VHDL</strong>Modulo (% bei <strong>Verilog</strong>, MOD, REM bei <strong>VHDL</strong>)REM (<strong>VHDL</strong>-Rest) übernimmt das Vorzeichen <strong>de</strong>s Divi<strong>de</strong>n<strong>de</strong>n,ebenso wie % (<strong>Verilog</strong>-Modulo):5 REM 3 = 2, 5 REM -3 = 2, -5 REM 3 = -2, -5 REM -3 = -2<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>49 / 83

Einleitung Grundlagen Programbeispiele FazitArithmetische OperatorenGrundrechenarten (+, -, *, /)Die Grundrechenarten können auch auf Bitvektoren angewen<strong>de</strong>twer<strong>de</strong>n, die dann als Binärzahlen interpretiert wer<strong>de</strong>n.Absolutwert (ABS) und Exponentiation (**) bei <strong>VHDL</strong>Modulo (% bei <strong>Verilog</strong>, MOD, REM bei <strong>VHDL</strong>)REM (<strong>VHDL</strong>-Rest) übernimmt das Vorzeichen <strong>de</strong>s Divi<strong>de</strong>n<strong>de</strong>n,ebenso wie % (<strong>Verilog</strong>-Modulo):5 REM 3 = 2, 5 REM -3 = 2, -5 REM 3 = -2, -5 REM -3 = -2MOD (<strong>VHDL</strong>-Modulo) übernimmt das Vorzeichen <strong>de</strong>s Divisors:5 MOD 3 = 2, 5 MOD -3 = -1, -5 MOD 3 = 1, -5 MOD -3 = -2<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>49 / 83

Einleitung Grundlagen Programbeispiele FazitLogische Operatoren<strong>VHDL</strong> kennt nur eine Gruppe logischer Operatoren, die jeweilssowohl auf Bits und Bitvektoren angewen<strong>de</strong>t wer<strong>de</strong>n können, un<strong>de</strong>in Resultat in diesen Datentypen zurückgeben:NOT, AND, OR, NAND, NOR, XOR und XNOR.Bei <strong>Verilog</strong> dagegen gibt es drei Arten:<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>50 / 83

Einleitung Grundlagen Programbeispiele FazitLogische Operatoren<strong>VHDL</strong> kennt nur eine Gruppe logischer Operatoren, die jeweilssowohl auf Bits und Bitvektoren angewen<strong>de</strong>t wer<strong>de</strong>n können, un<strong>de</strong>in Resultat in diesen Datentypen zurückgeben:NOT, AND, OR, NAND, NOR, XOR und XNOR.Bei <strong>Verilog</strong> dagegen gibt es drei Arten:Logische OperatorenDie Eingabewerte wer<strong>de</strong>n als Bits interpretiert, das Resultat ist einBit.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>50 / 83

Einleitung Grundlagen Programbeispiele FazitLogische Operatoren<strong>VHDL</strong> kennt nur eine Gruppe logischer Operatoren, die jeweilssowohl auf Bits und Bitvektoren angewen<strong>de</strong>t wer<strong>de</strong>n können, un<strong>de</strong>in Resultat in diesen Datentypen zurückgeben:NOT, AND, OR, NAND, NOR, XOR und XNOR.Bei <strong>Verilog</strong> dagegen gibt es drei Arten:Logische OperatorenDie Eingabewerte wer<strong>de</strong>n als Bits interpretiert, das Resultat ist einBit.Bitweise OperatorenEingabewerte sind hier Bitvektoren gleicher Länge, ebenso dasResultat.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>50 / 83

Einleitung Grundlagen Programbeispiele FazitLogische Operatoren<strong>VHDL</strong> kennt nur eine Gruppe logischer Operatoren, die jeweilssowohl auf Bits und Bitvektoren angewen<strong>de</strong>t wer<strong>de</strong>n können, un<strong>de</strong>in Resultat in diesen Datentypen zurückgeben:NOT, AND, OR, NAND, NOR, XOR und XNOR.Bei <strong>Verilog</strong> dagegen gibt es drei Arten:Logische OperatorenDie Eingabewerte wer<strong>de</strong>n als Bits interpretiert, das Resultat ist einBit.Bitweise OperatorenEingabewerte sind hier Bitvektoren gleicher Länge, ebenso dasResultat.ReduktionsoperatorenEingabewert ist hier ein Bitvektor, <strong>de</strong>ssen Bits mit <strong>de</strong>m Operatorverknüpft wer<strong>de</strong>n, das Resultat ist ein Bit.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>50 / 83

Einleitung Grundlagen Programbeispiele FazitVergleic<strong>hs</strong>operatorenBei <strong>VHDL</strong> gibt es nur eine Sorte Vergleic<strong>hs</strong>operatoren:>, >=,

Einleitung Grundlagen Programbeispiele FazitVergleic<strong>hs</strong>operatorenBei <strong>VHDL</strong> gibt es nur eine Sorte Vergleic<strong>hs</strong>operatoren:>, >=, =,

Einleitung Grundlagen Programbeispiele FazitVergleic<strong>hs</strong>operatorenBei <strong>VHDL</strong> gibt es nur eine Sorte Vergleic<strong>hs</strong>operatoren:>, >=, =,

Einleitung Grundlagen Programbeispiele FazitVergleic<strong>hs</strong>operatorenBei <strong>VHDL</strong> gibt es nur eine Sorte Vergleic<strong>hs</strong>operatoren:>, >=, =,

Einleitung Grundlagen Programbeispiele FazitSchiebeoperatoren<strong>Verilog</strong> kennt nur die logischen Schiebeoperatoren >.<strong>VHDL</strong> kennt drei Arten:Logische Schiebeoperatoren: SLL und SRLArithmetische Schiebeoperatoren: SLA und SRARotationsoperatoren: ROL und RORAlle verschieben einen Bitvektor um die angegebene Anzahl vonStellen nach links o<strong>de</strong>r rechts.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>52 / 83

Einleitung Grundlagen Programbeispiele FazitSchiebeoperatoren<strong>Verilog</strong> kennt nur die logischen Schiebeoperatoren >.<strong>VHDL</strong> kennt drei Arten:Logische Schiebeoperatoren: SLL und SRLArithmetische Schiebeoperatoren: SLA und SRARotationsoperatoren: ROL und RORAlle verschieben einen Bitvektor um die angegebene Anzahl vonStellen nach links o<strong>de</strong>r rechts.Bei <strong>de</strong>n logischen und arithmetischen Operatoren verschwin<strong>de</strong>n dieherausgeschobenen Bits, während Nullen (logisch) o<strong>de</strong>r <strong>de</strong>r Inhalt<strong>de</strong>r letzten Stelle (arithmetisch) nachgeschoben wer<strong>de</strong>n.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>52 / 83

Einleitung Grundlagen Programbeispiele FazitSchiebeoperatoren<strong>Verilog</strong> kennt nur die logischen Schiebeoperatoren >.<strong>VHDL</strong> kennt drei Arten:Logische Schiebeoperatoren: SLL und SRLArithmetische Schiebeoperatoren: SLA und SRARotationsoperatoren: ROL und RORAlle verschieben einen Bitvektor um die angegebene Anzahl vonStellen nach links o<strong>de</strong>r rechts.Bei <strong>de</strong>n logischen und arithmetischen Operatoren verschwin<strong>de</strong>n dieherausgeschobenen Bits, während Nullen (logisch) o<strong>de</strong>r <strong>de</strong>r Inhalt<strong>de</strong>r letzten Stelle (arithmetisch) nachgeschoben wer<strong>de</strong>n.Beim Rotieren wer<strong>de</strong>n die herausgeschobenen Bits auf <strong>de</strong>r an<strong>de</strong>renSeite hereingeschoben.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>52 / 83

Einleitung Grundlagen Programbeispiele FazitZusammenfügungsoperatorenBei <strong>VHDL</strong> wer<strong>de</strong>n Bitvektoren mit <strong>de</strong>m & Operatoraneinan<strong>de</strong>rgehängt.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>53 / 83

Einleitung Grundlagen Programbeispiele FazitZusammenfügungsoperatorenBei <strong>VHDL</strong> wer<strong>de</strong>n Bitvektoren mit <strong>de</strong>m & Operatoraneinan<strong>de</strong>rgehängt.Bei <strong>Verilog</strong> wer<strong>de</strong>n Bitvektoren mit <strong>de</strong>m Anhängeoperator { } und<strong>de</strong>m Replikationsoperator { { } } zusammengefügt:<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>53 / 83

Einleitung Grundlagen Programbeispiele FazitZusammenfügungsoperatorenBei <strong>VHDL</strong> wer<strong>de</strong>n Bitvektoren mit <strong>de</strong>m & Operatoraneinan<strong>de</strong>rgehängt.Bei <strong>Verilog</strong> wer<strong>de</strong>n Bitvektoren mit <strong>de</strong>m Anhängeoperator { } und<strong>de</strong>m Replikationsoperator { { } } zusammengefügt:A = 1'b1; B = 2'b00; C = 2'b11;X = { A, B } // X = 3'b100Y = { A, 2{B}, C } // Y = 7'b1000011<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>53 / 83

Einleitung Grundlagen Programbeispiele FazitKonditionaler OperatorDer konditionale Operator ? : hat drei Argumente, wovon das ersteein Bit ist und die bei<strong>de</strong>n an<strong>de</strong>ren Bitvektoren gleicher Länge sind,wie auch das Resultat. Ist das Bit 1, wird das zweite Argumentübernommen, bei 0 das dritte. Ist das Bit x, wer<strong>de</strong>nübereinstimmen<strong>de</strong> Stellen übernommen und die übrigen mit xbelegt.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>54 / 83

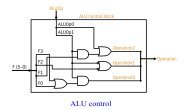

Einleitung Grundlagen Programbeispiele FazitKonstrukte auf GatterebeneIn <strong>Verilog</strong> können neue Gatter erstellt wer<strong>de</strong>n. Für diese UserDened Primitives (UDP) gilt:<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>55 / 83

Einleitung Grundlagen Programbeispiele FazitKonstrukte auf GatterebeneIn <strong>Verilog</strong> können neue Gatter erstellt wer<strong>de</strong>n. Für diese UserDened Primitives (UDP) gilt:Eingabewerte sind im UDP bestimmte BitsAusgabewert ist immer ein einziges Bit<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>55 / 83

Einleitung Grundlagen Programbeispiele FazitKonstrukte auf GatterebeneIn <strong>Verilog</strong> können neue Gatter erstellt wer<strong>de</strong>n. Für diese UserDened Primitives (UDP) gilt:Eingabewerte sind im UDP bestimmte BitsAusgabewert ist immer ein einziges BitMit Hilfe einer Wahrheitstabelle in <strong>de</strong>r Deklaration kann <strong>de</strong>rAusgabewert dann bestimmt wer<strong>de</strong>n. Dabei gibt es zwei Typen:<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>55 / 83

Einleitung Grundlagen Programbeispiele FazitKonstrukte auf GatterebeneIn <strong>Verilog</strong> können neue Gatter erstellt wer<strong>de</strong>n. Für diese UserDened Primitives (UDP) gilt:Eingabewerte sind im UDP bestimmte BitsAusgabewert ist immer ein einziges BitMit Hilfe einer Wahrheitstabelle in <strong>de</strong>r Deklaration kann <strong>de</strong>rAusgabewert dann bestimmt wer<strong>de</strong>n. Dabei gibt es zwei Typen:Kombinatorische UDPSequentielle UDP<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>55 / 83

Einleitung Grundlagen Programbeispiele FazitKombinatorische UDPBei kombinatorischen UDP ist <strong>de</strong>r Ausgabewert immer direkt von<strong>de</strong>n Eingabewerten und nichts an<strong>de</strong>rem abhängig.Der Ausgabewert wird dabei einer Wahrheitstabelle entnommen. Indieser Wahrheitstabelle sollten alle Kombinationen <strong>de</strong>rEingabewerte abge<strong>de</strong>ckt wer<strong>de</strong>n.Bei nicht abge<strong>de</strong>ckten Kombinationen <strong>de</strong>r Eingabewerte ergibt sichals Rückgabewert x.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>56 / 83

Einleitung Grundlagen Programbeispiele FazitKombinatorische UDP - Beispielprimitive udp_or(out, a, b);//Deklarationenoutput out;input a, b;table// a b : out;0 0 : 0;? 1 : 1;1 ? : 1;endtableendprimitiveDas Fragezeichen steht für '0, 1 o<strong>de</strong>r x'.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>57 / 83

Einleitung Grundlagen Programbeispiele FazitSequentielle UDPBei sequentiellen UDP gibt es wichtige Unterschie<strong>de</strong> zukombinatorischen UDP:Der neue Ausgabewert nicht nur von <strong>de</strong>n Eingabewerten, son<strong>de</strong>rnauch vom bisherigen Ausgabewert abhängig. Der Ausgabewert wirdhier als Zustand bezeichnet.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>58 / 83

Einleitung Grundlagen Programbeispiele FazitSequentielle UDPBei sequentiellen UDP gibt es wichtige Unterschie<strong>de</strong> zukombinatorischen UDP:Der neue Ausgabewert nicht nur von <strong>de</strong>n Eingabewerten, son<strong>de</strong>rnauch vom bisherigen Ausgabewert abhängig. Der Ausgabewert wirdhier als Zustand bezeichnet.Der Zustand wird in einem Register festgehalten; dieserRegisterwert kann auch initialisiert wer<strong>de</strong>n.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>58 / 83

Einleitung Grundlagen Programbeispiele FazitSequentielle UDPBei sequentiellen UDP gibt es wichtige Unterschie<strong>de</strong> zukombinatorischen UDP:Der neue Ausgabewert nicht nur von <strong>de</strong>n Eingabewerten, son<strong>de</strong>rnauch vom bisherigen Ausgabewert abhängig. Der Ausgabewert wirdhier als Zustand bezeichnet.Der Zustand wird in einem Register festgehalten; dieserRegisterwert kann auch initialisiert wer<strong>de</strong>n.Die Eingabewerte können als Werte o<strong>de</strong>r als Übergänge (Flanken) in<strong>de</strong>r Tabelle erscheinen.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>58 / 83

Einleitung Grundlagen Programbeispiele FazitSequentielle UDPBei sequentiellen UDP gibt es wichtige Unterschie<strong>de</strong> zukombinatorischen UDP:Der neue Ausgabewert nicht nur von <strong>de</strong>n Eingabewerten, son<strong>de</strong>rnauch vom bisherigen Ausgabewert abhängig. Der Ausgabewert wirdhier als Zustand bezeichnet.Der Zustand wird in einem Register festgehalten; dieserRegisterwert kann auch initialisiert wer<strong>de</strong>n.Die Eingabewerte können als Werte o<strong>de</strong>r als Übergänge (Flanken) in<strong>de</strong>r Tabelle erscheinen.Alle möglichen Kombinationen <strong>de</strong>r Eingabewerte müssen in <strong>de</strong>rWahrheitstabelle angegeben wer<strong>de</strong>n, um unbekannte Ausgabewerte(x) zu vermei<strong>de</strong>n.<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>58 / 83

Einleitung Grundlagen Programbeispiele FazitSequentielle UDP - Beispielprimitive edge_di(q, d, clock, clear );//Deklarationenoutput q;reg q;input d, clock, clear ;// Sequentielle Initialisierunginitialq = 0;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>59 / 83

Einleitung Grundlagen Programbeispiele FazitSequentielle UDP-Beispieltable// d clock clear : q : q+ ;? ? 1 : ? : 0 ; //wenn clear=1, output=0? ? (10) : ? : − ; //Zustand bei fallen<strong>de</strong>r Flanke von clear halten1 (10) 0 : ? : 1 ; //Übernehme d bei fallen<strong>de</strong>r0 (10) 0 : ? : 0 ; //Flanke von clock? (1x) 0 : ? : − ; //Zustand bei Übergang von clock zu x halten? (0?) 0 : ? : − ; //Zustand bei steigen<strong>de</strong>m Übergang von clock halten? (x1) 0 : ? : − ; //Zustand bei steigen<strong>de</strong>m Übergang von clock halten(??) ? 0 : ? : − ; //Solange clock gleich bleibt , Zustand haltenendtableendprimitive<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>60 / 83

Einleitung Grundlagen Programbeispiele Fazit1 EinleitungAnfängeProgrammablaufKomplexität2 GrundlagenDatentypenFunktionenModularisierungZeitverhaltenOperatorenKonstrukte auf Gatterebene3 Programbeispiele<strong>VHDL</strong> Enco<strong>de</strong>r<strong>Verilog</strong> Deco<strong>de</strong>r4 FazitÜbersicht<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>61 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Co<strong>de</strong>Non Return to Zero (NRZ)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>62 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Co<strong>de</strong>Non Return to Zero (NRZ)Manchester Daten =Clock XOR NRZ<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>62 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Co<strong>de</strong>Non Return to Zero (NRZ)Manchester Daten =Clock XOR NRZQuelle Wiki: http://<strong>de</strong>.wikipedia.org/wiki/Bild:Manchester_encoding_both_conventions.svg<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>62 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Co<strong>de</strong>Non Return to Zero (NRZ)Manchester Daten =Clock XOR NRZDC Anteil gleich NullQuelle Wiki: http://<strong>de</strong>.wikipedia.org/wiki/Bild:Manchester_encoding_both_conventions.svg<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>62 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Co<strong>de</strong>Non Return to Zero (NRZ)Manchester Daten =Clock XOR NRZDC Anteil gleich NullUART ähnliche ÜbertragungQuelle Wiki:http://<strong>de</strong>.wikipedia.org/wiki/Bild:RS-232_timing.png<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>62 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Aufbau <strong>de</strong>r Enco<strong>de</strong>r Entity me:e n t i t yme i sport (r s t , clk16x , wrn : i n s t d _ l o g i c ;din : i n std_logic_vector (7 downto 0) ;t b r e : out s t d _ l o g i c ;mdo : out s t d _ l o g i c) ;end me ;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>63 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Parameter in <strong>de</strong>r Entity port Liste:Name Typ Be<strong>de</strong>utungrst in Enco<strong>de</strong>r Resetwrn in Write Register Nextclk16x in 16-facher Taktdin in[7:0] NRZ Daten Vectortbre out Transceiver Buer Register Emptymdo out Manchester Data Out<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>64 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Struktur <strong>de</strong>r Architektur für die me Entity:a r c h i t e c t u r e v1 of me i ss i g n a l c l k 1 x : s t d _ l o g i c ;s i g n a l clk1x_enable : s t d _ l o g i c ;s i g n a l c l k d i v : std_logic_vector (3 downto 0 ) ;s i g n a l t s r : std_logic_vector (7 downto 0 ) ;s i g n a l t b r : std_logic_vector (7 downto 0 ) ;s i g n a l no_bits_sent : std_logic_vector (3 downto 0 ) ;begin−− S t ä n d i g e Zuweisungen und P r o z e s s eend ;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>66 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Interne Signale <strong>de</strong>r Architektur:Name Typ 1 Be<strong>de</strong>utungclk1x std_logic MC Clockclk1x_enable std_logic Freigabe Status für clk1xclkdiv stdlv[3:0] Clock Counter Registertsr stdlv[7:0] Ausgabe Vektortbr stdlv[7:0] Temporärer Vektorno_bits_sent stdlv[3:0] Bit Counter Register1 stdlv[n:0]=std_logic_vector (n downto 0)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>67 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Interne Signale <strong>de</strong>r Architektur:Name Typ 1 Be<strong>de</strong>utungclk1x std_logic MC Clockclk1x_enable std_logic Freigabe Status für clk1xclkdiv stdlv[3:0] Clock Counter Registertsr stdlv[7:0] Ausgabe Vektortbr stdlv[7:0] Temporärer Vektorno_bits_sent stdlv[3:0] Bit Counter Register1 stdlv[n:0]=std_logic_vector (n downto 0)<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>67 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Direkte Zuweisung in <strong>de</strong>r Architektur:−− s e t t i n g up the c l k 1 xc l k 1 x

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Prozessbeispiel: Takt einschaltenp r o c e s s ( r s t , clk16x , wrn , no_bits_sent )begini f r s t = '1 ' or std_logic_vector ( no_bits_sent ) ="1010" thenclk1x_enable

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Prozessbeispiel: Taktzähler inkrementierenp r o c e s s ( r s t , clk16x , c l k d i v , clk1x_enable )begini f r s t = '1 ' thenc l k d i v

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Prozessbeispiel: Source Register la<strong>de</strong>n und Rotierenp r o c e s s ( r s t , clk1x , no_bits_sent , t s r )begini f r s t = '1 ' thent s r

Einleitung Grundlagen Programbeispiele FazitDer Manchester Enco<strong>de</strong>r (<strong>VHDL</strong>)Starting Simulation of <strong>VHDL</strong> meLoading, please wait...<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>72 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Deco<strong>de</strong>r (<strong>Verilog</strong>)Aufbau <strong>de</strong>s Deco<strong>de</strong>r Modul md:module md ( r s t , clk16x , mdi , rdn , dout , data_ready ) ;i n p u t r s t ;i n p u t clk16x ;i n p u t mdi ;i n p u t rdn ;output [ 7 : 0 ] dout ;output data_ready ;// D e k l a r a t i o n i n t e r n e r V a r i a b l e n bzw . R e g i s t e r// D i r e k t e Zuweisungen a s s i g n// P r o z e s s e bzw . always Blöckeendmodule<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>73 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Deco<strong>de</strong>r (<strong>Verilog</strong>)Parameter <strong>de</strong>s md Moduls:Name Typ Be<strong>de</strong>utungrst input Deco<strong>de</strong>r Resetrdn input Lese Kontroll Signalclk16x input 16-facher Clockmdi input MC Daten Eingangdata_ready output Decoding fertig Status Signaldout output [7:0] Array mit <strong>de</strong>n Decodierten NRZ Daten<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>74 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Deco<strong>de</strong>r (<strong>Verilog</strong>)Interne Signale <strong>de</strong>s Moduls:Name Typ Be<strong>de</strong>utungclk1x_enable reg Freigabe Status für clk1xmdi1,mdi2 reg Letzter Zustand von mdinrz reg NRZ Wert <strong>de</strong>s letzten/aktuellen sampleno_bits_rcvd reg [3:0] Wort Zähler/ Operations Statusclkdiv reg [3:0] Clock Counter Registerrsr reg [7:0] Ergebniszwischenspeicher zum shiftenclk1x wire MC Taktsample wire Zeitgeber für 1/4 und 3/4 Takt Lesungen<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>75 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Deco<strong>de</strong>r (<strong>Verilog</strong>)Direkte Zuweisung im Modul:// Generate c e n t e r sample at p o i n t s 1/4 (0011) and3/4 (1100) through the data c e l la s s i g n sample = ( ! c l k d i v [ 3 ] && ! c l k d i v [ 2 ] && c l k d i v[ 1 ] && c l k d i v [ 0 ] ) | | ( c l k d i v [ 3 ] && c l k d i v [ 2 ] &&! c l k d i v [ 1 ] && ! c l k d i v [ 0 ] ) ;// Generate 1x c l o c ka s s i g n c l k 1 x = c l k d i v [ 3 ] ;<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>76 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Deco<strong>de</strong>r (<strong>Verilog</strong>)Prozessbeispiel: Manchester Co<strong>de</strong> Decodierenalways @( posedge clk16x or posedge r s t )i f ( r s t )nrz = 1 ' b0 ;e l s ei f ( no_bits_rcvd > 0 && sample == 1 ' b1 )nrz = mdi2 ^ c l k 1 x ; // ^ i s XOR<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>77 / 83

Einleitung Grundlagen Programbeispiele FazitDer Manchester Deco<strong>de</strong>r (<strong>Verilog</strong>)Prozessbeispiel: Decodiertes Datum in Array speichernalways @( posedge c l k 1 x or posedge r s t )i f ( r s t ) beginr s r

Einleitung Grundlagen Programbeispiele FazitDer Manchester Deco<strong>de</strong>r (<strong>Verilog</strong>)Prozessbeispiel: Bit-Zähl/Status Register erhöhenalways @( posedge c l k 1 x or posedge r s t or negedgeclk1x_enable )begini f ( r s t )no_bits_rcvd = 4 ' b0000 ;e l s e i f ( ! clk1x_enable ) beginno_bits_rcvd = 4 ' b0000 ;en<strong>de</strong> l s eno_bits_rcvd = no_bits_rcvd + 1 ;end<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>79 / 83

Einleitung Grundlagen Programbeispiele FazitSimulation Manchester Deco<strong>de</strong>rStarting Simulation of <strong>Verilog</strong> mdLoading, please wait...<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>80 / 83

Einleitung Grundlagen Programbeispiele Fazit1 EinleitungAnfängeProgrammablaufKomplexität2 GrundlagenDatentypenFunktionenModularisierungZeitverhaltenOperatorenKonstrukte auf Gatterebene3 Programbeispiele<strong>VHDL</strong> Enco<strong>de</strong>r<strong>Verilog</strong> Deco<strong>de</strong>r4 FazitÜbersicht<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>81 / 83

Einleitung Grundlagen Programbeispiele FazitDie Wahl <strong>de</strong>r Programmiersprache beinhaltet folgen<strong>de</strong> FaktorenDie Kompatibilität <strong>de</strong>r eingesetzten Entwicklungsumgebung (EDA)Vorkenntnisse <strong>de</strong>r Programmierer<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>82 / 83

Einleitung Grundlagen Programbeispiele FazitDie Wahl <strong>de</strong>r Programmiersprache beinhaltet folgen<strong>de</strong> FaktorenDie Kompatibilität <strong>de</strong>r eingesetzten Entwicklungsumgebung (EDA)Vorkenntnisse <strong>de</strong>r ProgrammiererPro <strong>VHDL</strong><strong>VHDL</strong> ist etwas weiter in Richtung Hoc<strong>hs</strong>prache angesie<strong>de</strong>ltWie<strong>de</strong>rverwendbarkeitStarke TypisierungMehr <strong>de</strong>klarativ als <strong>Verilog</strong><strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>82 / 83

Einleitung Grundlagen Programbeispiele FazitDie Wahl <strong>de</strong>r Programmiersprache beinhaltet folgen<strong>de</strong> FaktorenDie Kompatibilität <strong>de</strong>r eingesetzten Entwicklungsumgebung (EDA)Vorkenntnisse <strong>de</strong>r ProgrammiererPro <strong>VHDL</strong><strong>VHDL</strong> ist etwas weiter in Richtung Hoc<strong>hs</strong>prache angesie<strong>de</strong>ltWie<strong>de</strong>rverwendbarkeitStarke TypisierungMehr <strong>de</strong>klarativ als <strong>Verilog</strong>Pro <strong>Verilog</strong><strong>Verilog</strong> ist für eine schnelle simple Umsetzung gut geeignet<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>82 / 83

Einleitung Grundlagen Programbeispiele FazitEn<strong>de</strong>.So thank you for listening to us!Are there any questions?<strong>VHDL</strong> <strong>vs</strong>. <strong>Verilog</strong>83 / 83