Compal confidential - Data Sheet Gadget

Compal confidential - Data Sheet Gadget

Compal confidential - Data Sheet Gadget

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

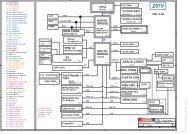

54321FSLCCLKSEL20FSLBCLKSEL1FSLACLKSEL0CPUMHz1 0 200SRCMHz100PCIMHz0 0 1 133 100 33.333.3+3VS_CK505R89+3VS 1 21FBMA-L11-201209-221LMA30T_0805 C20710U_0805_10V4Z21C2080.1U_0402_16V4Z2121C210C209680P_0402_50V7K 0.1U_0402_16V4Z2121C212C211680P_0402_50V7K 0.1U_0402_16V4Z21C2130.1U_0402_16V4Z2+3VSR902.2K_0402_5%R912.2K_0402_5%DCB0 1 1 166FSB Frequency Selet:55CPU Driven*(Default)667MHz800MHzCPU_BSEL0CPU_BSEL1StuffNo StuffStuffNo StuffStuffNo StuffR972.2K_0402_5%FSA 2 12FSB1CLRP2NO SHORT PADS1 2R1150_0402_5%121R1135100R1139R1086R110733.3R1107 R1135 R1083R1074 R1086 R1098 R1113 R1128 R1139R1086R1083R1113R1083R1074R1139R1107R1098R1135R1128R1098R111330 CLK_LPC_DEBUG1 2R981K_0402_5%+VCCPR1074R1128CLK_LPC_DEBUG20 CLKSATAREQ#@1K_0402_5%7 CLKREQ#_B2 1 CLK_DEBUG_PORT22,29 CLK_DEBUG_PORT_LPJP9+VCCP23 CLK_PCI_LANSHORT PAD21 2121 R93 256_0402_5%CLRP1NO SHORT PADSR102R111@1K_0402_5%1 2R1141K_0402_5%@ R1160_0402_5%MCH_CLKSEL1 7R1139R113530 CLK_PCI_EC18 CLK_PCI_ICH20 CLK_48M_ICH@ R4121 20_0402_5%PCI2_TME2Routing the trace atleast 10mil2C23018P_0402_50V8J 1+1.25VS_CK505CLRP4,CLRP5 for 667/800 FSB selectSHORT CLRP5, NO SHORT CLRP4 -- CPU optionSHORT CLRP4, NO SHORT CLRP5 -- FSB 667MCH_CLKSEL0 7475_0402_1%1 2 R103475_0402_1%1 2 R10439_0402_5% 1 2 R10539_0402_5% 1 2 R10639_0402_5% 1 2 R10739_0402_5% 1 2 R109Y139_0402_5% 1 2114.31818MHZ_16P21+3VS_CK505PCI_CLK1PCI2_TMEFSA27_SELITP_ENCLK_XTAL_INCLK_XTAL_OUTC23118P_0402_50V8JR117+1.25VSU4R92Place close to U4CLK_SMBCLKCLK_SMBDATAR_CPU_BCLKR_CPU_BCLK#R_MCH_BCLKR_MCH_BCLK#R_CLKREQ#_G+1.25VS_CK5051 20.1U_0402_16V4Z10U_0805_10V4Z 0.1U_0402_16V4Z111111FBMA-L11-201209-221LMA30T_0805C216 C217C219C215C218C21422222210U_0805_10V4Z680P_0402_50V7K680P_0402_50V7K2VDD_PCI9VDD4816VDDPLL361VDDREF39VDDSRC55VDDCPU12VDD96_IO20VDDPLL3_IO26VDDSRC_IO36VDDSRC_IO49VDDCPU_IOPCI_LANCLK 5PCI313467605910PCI0/CR#_APCI1/CR#_BPCI2/TMEPCI4/27_SelectPCIF5/ITP_ENX1X2USB_48MHZ/FSLANC 48SCLK 64SDATA63PCI_STOP#38CPU_STOP#37CPU054CPU0#53CPU1_F51CPU1#_F50SRC8/ITP47SRC8#/ITP#46SRC10#35SRC1034SRC11/CR#_H 33SRC11#/CR#_G 32SRC930SRC9#31SRC7/CR#_F44SRC7#/CR#_E43SRC641SRC6#40R941 21 2R95R961 21 2R99R112R_CLK_PCIE_MCard 1 2R_CLK_PCIE_MCard# 1 2R11320,22 ICH_SMBDATASB, MINI PCI20,22 ICH_SMBCLKCLK_SMBCLK 13,14CLK_SMBDATA 13,14H_STP_PCI# 20H_STP_CPU# 20+3VSCLK_CPU_BCLK 4CLK_CPU_BCLK# 4CLK_MCH_BCLK 7CLK_MCH_BCLK# 7For Layout request:1. Change MINI_CLKREQ# from pin 32 to pin 43.2. Change CLK_PCIE_MCARD from SRC9 to SRC6.R10820_0402_5%0_0402_5%0_0402_5%0_0402_5%475_0402_1%1MINI_CLKREQ# 22R110 10K_0402_5%1 2+3VS0_0402_5%0_0402_5%CLK_PCIE_MCARD 22CLK_PCIE_MCARD# 221 3DD2GS1 32GSQ32N7002_SOT23-3Q42N7002_SOT23-3C220C221C222C225C227C229222222CLK_SMBDATACLK_SMBCLK1 CLK_48M_ICH@5P_0402_50V8C1 CLK_14M_ICH@4.7P_0402_50V8C1 CLK_PCI_ICH@4.7P_0402_50V8C1 CLK_PCI_EC@4.7P_0402_50V8C1 CLK_PCI_LAN@4.7P_0402_50V8C1 CLK_DEBUG_PORT@5P_0402_50V8CDCBA5CPU_BSEL2FSC1 2R1260_0402_5%+VCCP+3VS +3VS +3VS1 2R13410K_0402_5%1 21 212R121R124@1K_0402_5%10K_0402_5%2 1 1 2R13510K_0402_5%@R1251K_0402_5%@ R1290_0402_5%1 2R13610K_0402_5%ITP_EN 27_SEL PCI2_TMEMCH_CLKSEL2 720 CLK_14M_ICH30 CLK_14M_DEBUG33_0402_1% 1 2CLK_DEBUG_PORTC44139P_0402_50V8JFor ITP_EN, 0 =SRC8/SRC8#; 1 = ITP/ITP#For 27_SEL, 0 = Enable DOT96 & SRC1,1= Enable SRC0 & 27MHzR120+1.25VS_CK505For PCI2_EN, 0 = Overclocking of CPU and SRC Allowed1 = Overclocking of CPU and SRC NOT allowed1233_0402_1% @R4001 2FSBFSC57624542811151952232958FSLB/TEST MODEREF0/FSLC/TEST_SELVDDSRC_IOGNDSRCGNDPCIGND48GNDGNDGNDCPUGNDSRCGNDSRCGNDREFICS9LPRS355_TSSOP64* Internal Pull-Up Resistor** Internal Pull-Down ResistorSRC427SRC4#28SRC3/CR#_C 24SRC3#/CR#_D 25SRC2/SATA21SRC2#/SATA#22SRC1/SE1/27MHz_NonSS17SRC1#/SE2/27MHz_SS18SRC0/DOT9613SRC0/DOT96#14CK_PWRGD/PD#56R_MCH_3GPLLR_MCH_3GPLL#R_PCIE_ICHR_PCIE_ICH#R_PCIE_SATAR_PCIE_SATA#SSCDREFCLKR130SSCDREFCLK# R131R1181 21 2R119R1221 21 2R123R1271 21 2R1281 21 2R132R_MCH_DREFCLKR_MCH_DREFCLK#1122R133@ R1371 2@ R3671 21 2R3440_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%0_0402_5%CLK_MCH_3GPLL 7CLK_MCH_3GPLL# 7CLK_PCIE_ICH 20CLK_PCIE_ICH# 20CLK_PCIE_SATA 19CLK_PCIE_SATA# 19MCH_SSCDREFCLK 7MCH_SSCDREFCLK# 7CLK_MCH_DREFCLK 7CLK_MCH_DREFCLK# 7VGATE 20,37CLK_ENABLE 30CK_PWRGD 20A1 2R13810K_0402_5%@1 251 2R13910K_0402_5%R14010K_0402_5%@http://hobi-elektronika.net4Security ClassificationIssued Date3<strong>Compal</strong> Secret <strong>Data</strong>2007/03/26 Deciphered Date2006/03/10THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIALAND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&DDEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINSMAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.2Title<strong>Compal</strong> Electronics, Inc.Clock generatorSize Document Number RevLA-3732P 1.0Date: Monday, July 09, 2007<strong>Sheet</strong> 15 of 421