VHDL CONCURRENTE

VHDL CONCURRENTE

VHDL CONCURRENTE

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

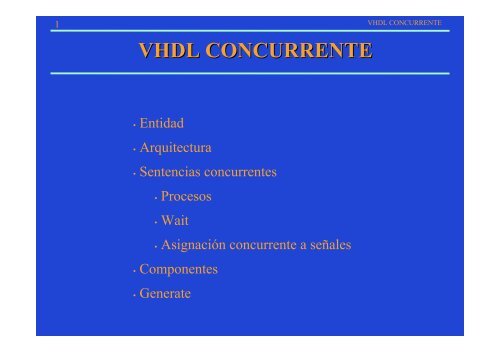

1 <strong>VHDL</strong> <strong>CONCURRENTE</strong><strong>VHDL</strong> <strong>CONCURRENTE</strong>• Entidad• Arquitectura• Sentencias concurrentes• Procesos• Wait• Asignación concurrente a señales• Componentes• Generate

2 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Declaración entidadentity_decl

3 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Entidad: Ejemploentity program_rom isport ( address : in bit_vector (14 downto 0) ;data : out bit_vector (7 downto 0) ;enable : in bit );subtype instruction_byte is bit_vector (7 downto 0);type program is array (0 to 2**14-1) of instruction_byte;end entity program_rom;Declaración de tipos, señales o constantes(no variables)

4 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Declaración arquitecturaNombre arquitecturaarch_body

5 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Arquitectura: Ejemploarchitecture primitive of and_or_inv issignal and_a, and_b, or_a_b : bit;beginand_a: process isbeginand_a

6 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Sentencias concurrentesSentencias que se ejecutan simultáneamente en lasimulación:•Procesos•Asignación concurrente a señales•Instanciación de componentes•Sentencias generate•When-else

7 <strong>VHDL</strong> <strong>CONCURRENTE</strong>ProcesosLista sensitiva (opcional)process_stmt

8 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Procesos• Lista sensitiva: variables que disparan el proceso.

9 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Lista sensitiva: Ejemplo

10 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Lista sensitiva: Ejemplo

11 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Lista sensitiva/Sentencia wait• Lista sensitiva es equivalente a una sentencia “wait”antes del “end process”.• <strong>VHDL</strong> requiere que el proceso tenga uno de los dos:• lista sensitiva• una o más sentencias wait.

12 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Procesos: EjemploProcesos equivalentes

13 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Sentencia wait.• Suspende la ejecución de un proceso.• Tres tipos de sentencia wait:• Combinaciones también posibles:

14 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Wait on• Proceso suspendido hasta que se produce unevento en A, B o C.

15 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Wait until• Proceso suspendido hasta que la condición severifica.

16 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Wait for• Suspensión del proceso durante 10ns.

17 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Wait for: Ejemplo aplicación• Generación de un relojpara simulaciones.Proceso sin listasensitiva

18 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Asignación concurrente a señales• La asignación concurrente se hace en el cuerpode la arquitectura (fuera de procesos).• Existe la versión equivalente mediante utilización deprocesos.

19 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Asignación concurrente a señalesconcurrent_signal

20 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Asignación concurrente a señales: Ejemploszmux: z

21 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Declaración de componentes• Declaración dentro de la arquitectura o del paquete.• Declaración casi idéntica a declaración de entidad.

22 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Instanciación de componentes• Instanciación dentro de la arquitectura: Sentenciaconcurrente.• Se incluye una etiqueta para identificar el elementoinstanciado.

23 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Instanciación de componentes

24 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Componentes: Ejemplo diseño• Sumador acarreo enlazado de 4 bits.

25 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Componentes: Ejemplo diseñohalf adder

26 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Componentes: Ejemplo diseñofull adder

27 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Componentes. Ejemplo diseño.(behav);(behav);full adder

28 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Componentes: Ejemplo diseñoSumador acarreoenlazado

29 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Componentes• Especificación de la componente a utilizar

30 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Sentencias generate• Para instanciar componentes idénticos bajo el control deun índice o de una condición.library IEEE; use IEEE.std_logic_1164.all;entity PARIDAD isgeneric(no_bits: integer:=32);port(IN_DAT: in std_logic_vector (no_bits-1 downto 0);PARITY: out std_logic);end PARIDAD;architecture ARBOL_XOR of PARIDAD issignal TMP: std_logic_vector (no_bits-1 downto 0);beginTMP (no_bits-1)

31 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Sentencias generate: Ejemplo

32 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Sentencias generate: Ejemplo

33 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Sentencias generate: Ejemplo

34 <strong>VHDL</strong> <strong>CONCURRENTE</strong>Sentencias generate: Ejemplo