M.Sc. (IT.) First Semester Examination,2011 Paper-III(MIT-102 ...

M.Sc. (IT.) First Semester Examination,2011 Paper-III(MIT-102 ...

M.Sc. (IT.) First Semester Examination,2011 Paper-III(MIT-102 ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

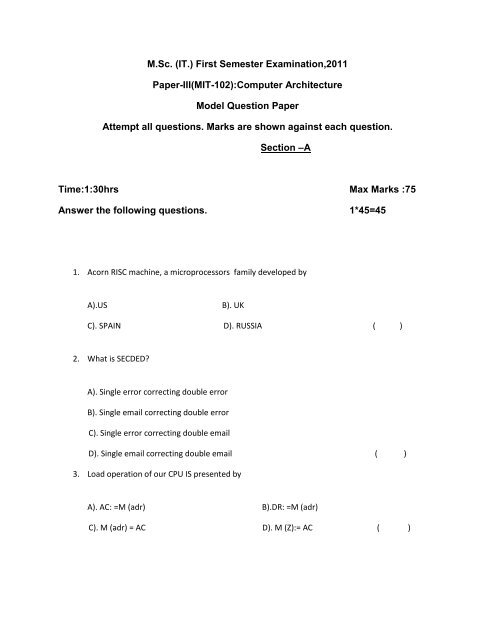

M.<strong>Sc</strong>. (<strong>IT</strong>.) <strong>First</strong> <strong>Semester</strong> <strong>Examination</strong>,<strong>2011</strong><br />

<strong>Paper</strong>-<strong>III</strong>(M<strong>IT</strong>-<strong>102</strong>):Computer Architecture<br />

Model Question <strong>Paper</strong><br />

Attempt all questions. Marks are shown against each question.<br />

Section –A<br />

Time:1:30hrs Max Marks :75<br />

Answer the following questions. 1*45=45<br />

1. Acorn RISC machine, a microprocessors family developed by<br />

A).US B). UK<br />

C). SPAIN D). RUSSIA ( )<br />

2. What is SECDED?<br />

A). Single error correcting double error<br />

B). Single email correcting double error<br />

C). Single error correcting double email<br />

D). Single email correcting double email ( )<br />

3. Load operation of our CPU IS presented by<br />

A). AC: =M (adr) B).DR: =M (adr)<br />

C). M (adr) = AC D). M (Z):= AC ( )

4. Who proposed CPU organization…………………:<br />

A). Von Neuman B).Denis richi<br />

C). Mick D). Bell and newels ( )<br />

5. A 32-bit floating point no. conforming to the IEEE 754 standard represents the real no. n is given<br />

by the formula.<br />

A). N= (-1) s 2- e+127 (1,M) B). N= (1) s 2- e+127 (1, M)<br />

C). N= (-1) s 2- e+127 (1, M-1) D). N= (-1) s 2- e-127 (1,M) ( )<br />

6. Which machine perform load and store architecture.<br />

A). Cisc machine B). Risc machine<br />

C). Intel D). CISC-Motorola ( )<br />

7. A handhelds” personal digital assistant “is introduced by?<br />

A). Apple corp. B). IBM<br />

C). Cruse D). ARM1 ( )<br />

8. Which processors family is primarily aimed to design low-power, low cost applications.<br />

A). Intel B). Cisc developer<br />

C). IBM D).arm ( )<br />

9. Implementation of ACXN is refers as:<br />

A). AC+AC +……..+AC B). AC+AC -……..+AC<br />

C). AC+AC +……..-AC D). AC*AC +……..+AC ( )

10. Floating point multiplication can be expressed in the term of :<br />

A).Pi+1:=Pi+xj2 i y B). Pi1:=Pi+xj2 i y<br />

C).Pi-1:=Pi+xj2 i y D). Pi+2:=Pi+xj2 i y ( )<br />

11. ALU expansion can be divided in which one of the following.<br />

A). Temporal expansion and spatial expansion<br />

B). Temporal expansion and integral expansion<br />

C). Local expansion and spatial expansion<br />

D). Temporal expansion and local expansion ( )<br />

12. Advanced micro devices 2901 bit sliced ALU developed by.<br />

A). Mick and brick B). Mux and brick<br />

C). Brick and deiv D).Mick and grill ( )<br />

13. In multiplication the shift multiplier is added to the multiplicand to form the …………………:<br />

A). Relation B).product<br />

C). Divisor D). Semiconductor DRAM ( )<br />

14. Array implementation of the booth multiplication algo. Developed as.<br />

A). Brick B). Koren<br />

C). Grill D). Moore ( )<br />

15. The owner of booth multiplication algorithms is.<br />

A). Andrew D. BOOTH B). SD BOOTH<br />

C). Brick Booth D). 4. Mick ( )

16. Combinational arithmetic logic unit design by?<br />

A). Cruse B). Robertson<br />

C). Hansen & Hayes D). Mick ( )<br />

17. Robertson describe multiplication algorithms for ………………… fraction.<br />

A). 1’s complement B). 2’s complement<br />

C). 0’s complement D). None ( )<br />

18. Booth multiplier algo which can be implemented with :<br />

A). Cisc machine B). Robert’s multiply instruction<br />

C). ARM’S multiply instruction D).Intel machine ( )<br />

19. Hardwired controller approaches design by<br />

A).Shanley and Anderson B). Shill<br />

C). Hayes and barnov D). Grill ( )<br />

20. Which one is used Finite – state machine theory for control design.<br />

A). Mealy & Moore B). Robertson<br />

C). Hayes D). Grill ( )<br />

21. In which year Euclid’s algorithm used for a calculating gcd(x,y):<br />

A). 1990 B). 1993<br />

C). 1992 D). 1999 ( )<br />

22. One-Hot method which can be used in the area of:

A). GCD processing B). Hardwired control<br />

C). Pipeline D). Error detection ( )<br />

23. In control designing One –Hot method always used.<br />

A). one flip-flop per state B). Two flip-flop per state<br />

C). Three flips-flop per state D). None ( )<br />

24. Pipeline used performance/cost ratio in PCR define as.<br />

A). PCR=F/K B). PCR=1/K<br />

C). PCR=F-1/K D). PCR=1/F ( )<br />

25. Pipeline organization of the MIPS R2/3000 is organized by.<br />

A). Kane& Heinrich B). Steve<br />

C). Robertson D). Grill ( )<br />

26. Euclid’s algorithm used for gcd (x, y) calculating is designed by.<br />

A). Cormov B). Grill<br />

C). Moore D). Mick ( )<br />

27. Every clock cycle logic circuit in microprogramming performs the operation, in the term of:<br />

A). Cout µPC:=Y+Cin B). Cin µPC:=Y+Cin<br />

C). Cout µPC:=µY+Cin D). Cout µPC:=Y+Cout ( )<br />

28. Define the cost c of memory as n follows as :<br />

A).c=C/S Dollar per bit B). c=C-1/S Dollar per bit<br />

C). c=S/S-1 Dollar per bit D). c=S/C Dollar per bit ( )

29. In memory system Cost/performance is designed by.<br />

A). Mealy & Moore B). Robertson<br />

C). Cooke & white D). Grill ( )<br />

30. Which type of semiconductor memory contain refreshing unit.<br />

A). DRAM B). DRO<br />

C). SRAM D).ROM ( )<br />

31. 64-MB dram chip was developed for semiconductor memory design:<br />

A). IBM B).micron technology<br />

C). Microsoft D). Semiconductor DRAM CMOS lab ( )<br />

32. Data line can be used in complex way which one is used.<br />

A). Robertson B). Weste and Eshraghian<br />

C). Grill D). Moore ( )<br />

33. Memory address depends upon the characterizes of computer program called ………………….. .<br />

A). ACCESS time B). Cost<br />

C). Locality of reference D). Virtual address ( )<br />

34. Which one is continuous increasing when we are used in memory hierarchical design?<br />

A). Cost B). Access time<br />

C). Capacity D). Time ( )<br />

35. Cost can be referring in the term of.<br />

A). C=S1c1+c2S2/S1+S2 B). c=S1c1-c2S2/S1-S2<br />

C). C=S1c1+c2S2/S1-S2 D). c=S1c1-c2S2/S1+S2 ( )

36. cache design for the power pc 620 designed by:<br />

A). Ewedemi, Todd B). Mick<br />

C). Robertson D). Grill ( )<br />

37. Peripheral component are interconnected with bus design describe by.<br />

A). Shanley and Anderson B). Shill<br />

C). Robertson D). Grill ( )<br />

38. Interrupt occurring during the execution of an instruction is precise condition follows by.<br />

A). Moudgill B). Robertson<br />

C). Shanley D). Grill ( )<br />

39. Degree of parallism is “n” in term of :<br />

A). Sn= T (1)/T (n) B). Sn= T (1)-1/T (n)<br />

C). Sn= T (n)/T (1) D). Sn= T (1)/T (n) -1 ( )<br />

40. Cache coherence protocol design in which year.<br />

A). 1996 B). 1920<br />

C). 1995 D). 1960 ( )<br />

41. MESI Cache coherence protocol design by.<br />

A). Shanley and Anderson B). Andrew<br />

C). Robertson D). Mick ( )<br />

42. Each ARPANET site had a computer called.

A). IMP B). ICP<br />

C). CMP D). GCC ( )<br />

43. ARPANET which provide packet switching in which year.<br />

A).1960 B). 1918<br />

C). 1971 D). 1970 ( )<br />

44. The K-masked interrupted signal is fed in to a priority encoder that produces.<br />

A). a [log2K-1 ]-bit B). a-1 [log2K-1 ]-bit<br />

C). a [log2K ]-bit D). a-1 [log2K]-bit ( )<br />

45. Acknowledge signal allow a long delay one or more bus cycles called.<br />

A). Read state B). Clock state<br />

C). Waite state D). Write state ( )