Calcolatori Elettronici - Politecnico di Torino

Calcolatori Elettronici - Politecnico di Torino

Calcolatori Elettronici - Politecnico di Torino

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

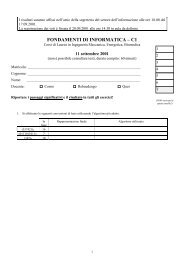

<strong>Politecnico</strong> <strong>di</strong> <strong>Torino</strong> – Sede <strong>di</strong> <strong>Torino</strong>Corso <strong>di</strong> laurea a <strong>di</strong>stanza in Ingegneria Informatica/Elettronica/Telecomunicazioni<strong>Calcolatori</strong> <strong>Elettronici</strong>Tema d’esame del 14 marzo 2008 (1h 30min)Cognome Nome MatricolaE-mail per GiustificaLavorativaDomande a risposta multipla (giusta +2 punti, sbagliata -1, non data 0)Riportare soltanto la lettera della risposta ritenuta corretta nell’apposito campo a destraSi consideri un <strong>di</strong>sco che adotti lastrategia CLV (Constant LinearVelocità). Quale delle seguentiaffermazioni è vera ?Quale delle seguenti affermazioni non ècorretta se riferita ad una procedura ?Si consideri un’unità <strong>di</strong> controllo ingrado <strong>di</strong> pilotare 65 segnali e compostada 418 microistruzioni: quale sarà ilparallelismo del µPC se si usa lamicroprogrammazione orizzontale ?Chi definisce il contenuto della memoria<strong>di</strong> microco<strong>di</strong>ce esistente all’interno <strong>di</strong>un processore microprogrammato ?In una memoria cache che adotta il setassociative mapping ogni bloccoproveniente dalla memoria principale:Si consideri una CPU con architetturaPipeline, quale delle seguentiaffermazioni è vera ?Si consideri un sistema che utilizza ilmeccanismo del memory mapped peraccedere alle periferiche: come èpossibile eseguire in tale caso leoperazioni <strong>di</strong> I/O ?In un meccanismo <strong>di</strong> arbitraggiocentralizzato <strong>di</strong> un bus basato supolling, quanti segnali <strong>di</strong> BusRequestentrano nell’arbitro posto che sia 5 ilnumero <strong>di</strong> <strong>di</strong>spositivi connesso al bus ?A. La densità <strong>di</strong> memorizzazione (bit/inch)varia a seconda della <strong>di</strong>stanza dal centroB. Il tempo <strong>di</strong> accesso viene minimizzatoC. Il <strong>di</strong>sco ruota a velocità angolare costante,in<strong>di</strong>pendentemente dalla posizione sullatestinaD. Il <strong>di</strong>sco ruota con velocità angolare <strong>di</strong>versaa seconda della posizione della testinaA. E’ un gruppo <strong>di</strong> istruzioni che eseguono uncompito specificoB. E’ eseguita un numero qualsiasi <strong>di</strong> volteC. Viene identificata alla fine <strong>di</strong> ogni instructioncycleD. E’ svantaggioso il tempo <strong>di</strong> elaborazionerichiesto per le operazioni <strong>di</strong> chiamata e ritornoA. 6B. 7C. 8D. 9A. Il programmatore assemblerB. Il sistema operativoC. Il progettista del processoreD. Il compilatoreA. Viene caricato in una linea <strong>di</strong> cache tra quellelibereB. Viene caricato nella linea <strong>di</strong> cache associata aquel bloccoC. Viene caricato in una delle linee <strong>di</strong> cacheassociate a quel bloccoD. Viene caricato in una linea <strong>di</strong> cache a casoA. Il tempo <strong>di</strong> esecuzione <strong>di</strong> una istruzione èinvariato rispetto ad una CPU senza pipelineB. Ogni operazione della pipeline avviene in più <strong>di</strong>un colpo <strong>di</strong> clockC. Le unità funzionali della CPU comunicano tra <strong>di</strong>loro solo attraverso registri della pipelineD. L’aumento del throughput, comporta la riduzionedel tempo <strong>di</strong> esecuzione <strong>di</strong> ogni singolaistruzione, e quin<strong>di</strong> un aumento della velocità.A. Attraverso il DMAB. Attraverso le istruzioni IN e OUTC. Attraverso l’uso dell’arbitro <strong>di</strong>stribuito tra leperifericheD. Attraverso una istruzione che faccia accesso allamemoriaA. 1B. log 5C. 6D. log 2 5

Domande a risposta aperta (5 punti ciascuna)1. Si rappresenti l’architettura interna del DMA controller in relazione alloschema <strong>di</strong> CPU riportato. Si descriva brevemente il significato dei registriinterni alla CPU e al DMA controller.ABUSMemoriaDBUSARIRDRUnità <strong>di</strong>ControlloCPU2. Si illustri l’organizzazione dei registri nota come “Register Window”nell’ambito <strong>di</strong> esecuzione <strong>di</strong> una procedura.Esercizio (8 punti):Progettare e implementare il circuito in grado <strong>di</strong> riconoscere la sequenza <strong>di</strong> dati iningresso “1011”.Riportare in modo dettagliato tutti passaggi relativi ai seguenti punti:a. macchina a statib. funzione <strong>di</strong> transizione degli static. funzione delle uscited. circuito con porte logiche e Flip-Flop.