VHDL íë¡ê·¸ëë° VHDL ëë°

VHDL íë¡ê·¸ëë° VHDL ëë°

VHDL íë¡ê·¸ëë° VHDL ëë°

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

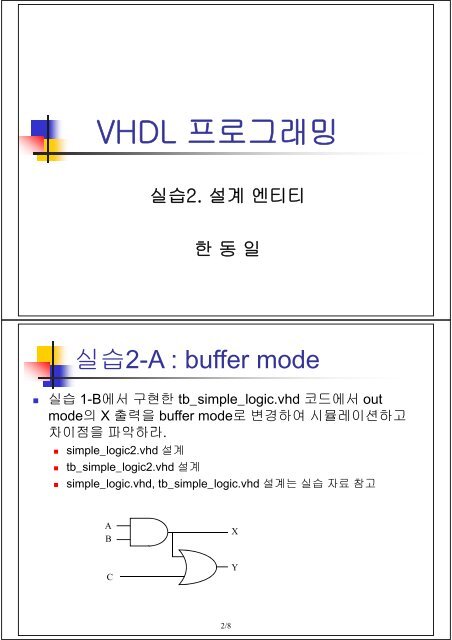

<strong>VHDL</strong> 프로그래밍실습2. 설계 엔티티한 동 일실습2-A A : buffer mode• 실습 1-B에서 구현한 tb_simple_logic.vhd 코드에서 outmode의 X 출력을 buffer mode로 변경하여 시뮬레이션하고차이점을 파악하라.• simple_logic2.vhd 설계• tb_simple_logic2.vhd 설계• simple_logic.vhd, tb_simple_logic.vhd 설계는 실습 자료 참고ABXCY2/8

실습2-A A : buffer modeABXCY3/8실습2-B B : component의 사용• 실습 1-B와 2-A에서 설계한 simple_logic 엔티티와simple_logic2 엔티티를 동시에 테스트하는tb_simple_logic4.vhd l i 를 설계하고 후 simulation을 을 통하여확인하라.4/8

실습2-C C : generic의 사용• 실습자료 2의 tb_concatenator.vhd 코드를 이해하고generic 절에서 사용된 N의 용도를 이해하라.• Simulation 을 통하여 결과를 확인하라.• 두입력신호A, B의 비트신호를3비트로 확장하되 다음의두 가지 방법을 이용하라.• Generic 절을 이용하여 입력 신호를 3비트로 확장하라.• Generic 절을 이용하지 않고 입력 신호를 3비트로 확장하라.• 각각의 설계 결과를 Simulation 을 통하여 확인하라.5/8실습2-C C : generic의 사용6/8

실습2-D D : architecture 구현기법• 교재 165페이지의 연습문제 18번을 풀고 세 가지 종류의설계 결과를 시뮬레이션을 통해서 비교 확인하라.ABXCY7/8실습2-D D : architecture 구현기법ABXCY8/8