trabalho sobre proce.. - Filosofar Sempre!!!!

trabalho sobre proce.. - Filosofar Sempre!!!!

trabalho sobre proce.. - Filosofar Sempre!!!!

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

eferenciar a memória.<br />

3.4 Pipelining<br />

É claro que proibir que as instruções comuns acessem a memória não resolve o<br />

problema de como fazer com que LOADs e STOREs operem em um ciclo. A solução<br />

está em um pouco de truque. Vamos agora relaxar nosso objetivos ligeiramente. Em<br />

vez de requerer que toda instrução deva ser executada em um ciclo, vamos meramente<br />

insistir que seremos capazes de começar uma instrução a cada ciclo, sem levar em<br />

consideração quando é que ela termina. Se, em n ciclos, conseguirmos iniciar n<br />

instruções, na média teremos atingido uma instrução por ciclo, o que é<br />

suficientemente bom.<br />

Para atingir este objetivo modificado, todas as máquinas RISC têm pipeline. A<br />

CPU contém diversas unidades independentes que trabalham em paralelo. Uma delas<br />

busca as instruções, e outras as decodificam e executam. A qualquer instante, diversas<br />

instruções estão em vários estágios de <strong>proce</strong>ssamento.<br />

Uma instrução comum utiliza duas unidades pipeline, uma para busca e outra<br />

para execução. Num instante de tempo uma instrução é iniciada. No outro instante, a<br />

instrução iniciada muda de unidade e é executada. Na unidade que ficou livre é iniciado<br />

uma nova instrução. Assim mantemos a média, que é iniciar uma instrução a cada ciclo.<br />

Porém instruções LOADs e STOREs requer uma terceira unidade, para referenciar a<br />

memória. Então, em vez de finalizar a execução em duas unidades, finalizam em três<br />

unidades. Na Tab. 3.3, exemplo de uma pipeline em execução.<br />

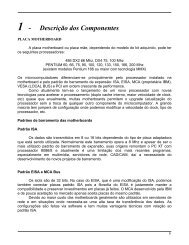

Ciclo<br />

1 2 3 4 5 6 7 8 9 10<br />

Busca de instrução 1 2 L 4 5 6 S 8 9 10<br />

Execução de instrução 1 2 L 4 5 6 S 8 9<br />

Referência à memória L S<br />

Tab. 3.3: Uma máquina RISC com pipeline contendo LOAD (L) e STORE (L) atrasados<br />

3.5 Uso de Registrador<br />

O objetivo de toda máquina RISC é executar uma instrução por ciclo, na média.<br />

Uma vez que LOAD e STORE tipicamente requerem dois ciclos, está média só pode<br />

ser atingida se o compilador tiver sucesso no preenchimento de 100 % dos buracos de<br />

atraso depois de cada um deles. Isto leva a raciocinar que, quanto menos LOADs e<br />

STOREs existirem, menos serão desperdiçados devido à inabilidade do compilador em<br />

preenchê-los com alguma coisa útil.<br />

Por está razão, compiladores para máquinas RISC fazem uso intenso de<br />

registradores, para reduzir o tráfego de memória (isto é, o número de LOADs e<br />

STOREs). As máquinas RISC possuem substancialmente mais registradores do que<br />

máquinas CISC.<br />

3.6 Por que <strong>proce</strong>ssadores RISC não decolaram?<br />

"Nos anos, alguns engenheiros de RISC ridicularizaram o CISC e predisseram o<br />

fim da família x86. Infelizmente para eles, a penalidade por menosprezar os<br />

fabricantes (principalmente a Intel) é até maior que a penalidade para não prever<br />

29