trabalho sobre proce.. - Filosofar Sempre!!!!

trabalho sobre proce.. - Filosofar Sempre!!!!

trabalho sobre proce.. - Filosofar Sempre!!!!

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

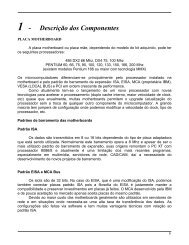

três filas (que esperam pelas ALUs de inteiros, as FPUs ou a unidade de<br />

carga/armazenagem). Essas filas são atendidas em qualquer ordem em que seus recurso<br />

fiquem livres.<br />

A ordem de programa é finalmente restaurada pela "graduação" (que é jargão da<br />

MIPS para a retirada) da instrução mais antiga. Isso assegura também um preciso relato<br />

de exceções. Esse reordenamento de instruções auxiliado por hardware oferece uma<br />

grande vantagem para os usuário finais porque o código escrito para as CPUs escalares<br />

mais antigas da MIPS ganharão o beneficio quase total de velocidade sem necessidade<br />

de recompilação.<br />

O MIPS tem potencial para emitir cinco instruções por ciclo, mas pode trazer e<br />

retirar somente quatro; uma quinta não pode ser completada no mesmo ciclo.<br />

Entretanto, esse excesso de largura de faixa de despacho oferece oportunidades mais<br />

flexíveis para o agendamento de instruções.<br />

3.7.3 Sun Microsystems<br />

Pioneira na adoção da tecnologia RISC, a Sun especificou o SPARC como uma<br />

arquitetura escalável. Contém nove unidades de execução: duas ALUs de inteiros,<br />

cinco FPUs (duas para adição em ponto flutuante, duas para multiplicação de ponto<br />

flutuante e uma para divisão/raiz quadrada em ponto flutuante), uma unidade de<br />

<strong>proce</strong>ssamento de ramificações e uma unidade de carga/armazenagem. Tem previsão<br />

dinâmica de ramificações previstas, mas não pode emitir instruções fora de ordem.<br />

Depende de compiladores otimizados para ordená-las bem.<br />

3.7.4 Hewlett – Packard (HP)<br />

A HP foi das primeiras a entrar no mercado RISC, lançando o seu primeiro<br />

<strong>proce</strong>ssador PA-RISC de 32 bits em 1986.<br />

Os chips da HP possuem 10 unidades funcionais: duas ALUs de inteiros, duas<br />

unidades de deslocamentos/mescla, duas unidades multiplicar/acumular (MAC) de<br />

ponto flutuante, duas unidades de divisão/raiz quadrada em ponto flutuante e duas<br />

unidades de carga/armazenagem. As unidades MAC têm latência de três ciclos e são<br />

totalmente canalizadas para <strong>proce</strong>ssamento em precisão simples para proporcionar até 4<br />

FLOPS por ciclo. As unidades de divisão tem latência de 17 e não são canalizadas,<br />

mas podem funcionar concorrentemente com as MACs.<br />

31