Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

3. Sensor Global<br />

3.3 Temporiza<strong>do</strong>r<br />

Devi<strong>do</strong> ao funcionamento periódico <strong>do</strong> Sensor Global, <strong>para</strong> implementar o bloco Temporiza<strong>do</strong>r<br />

são necessários <strong>do</strong>is subsistemas. O primeiro é um divisor <strong>de</strong> relógio <strong>para</strong> gerar a base <strong>de</strong> tempo<br />

<strong>para</strong> o accionamento <strong>do</strong> sensor. O segun<strong>do</strong> dispositivo é uma máquina <strong>de</strong> esta<strong>do</strong>s que é accionada<br />

pelo divisor <strong>de</strong> relógio e cujo objectivo é gerar os sinais <strong>de</strong> controlo necessários aos três submo<strong>do</strong>s<br />

presentes no Mo<strong>do</strong> <strong>de</strong> Teste <strong>do</strong> Sensor PVTA.<br />

3.3.1 Divisor <strong>de</strong> Relógio<br />

Existem alguns méto<strong>do</strong>s <strong>para</strong> implementar divisores <strong>do</strong> sinal <strong>de</strong> relógio. No caso específico<br />

<strong>de</strong>ste trabalho interessa uma solução simples e <strong>de</strong> consumo reduzi<strong>do</strong>, mas que permita alguma<br />

flexibilida<strong>de</strong> na alteração da base <strong>de</strong> tempo. A solução que mais se aproxima <strong>do</strong>s objectivos<br />

pretendi<strong>do</strong>s é o conta<strong>do</strong>r assíncrono. Esta topologia <strong>de</strong> conta<strong>do</strong>r tem a vantagem <strong>de</strong> usar apenas<br />

flip-flops na sua implementação, com o benefício <strong>de</strong> consumir menos energia <strong>do</strong> que o conta<strong>do</strong>r<br />

síncrono.<br />

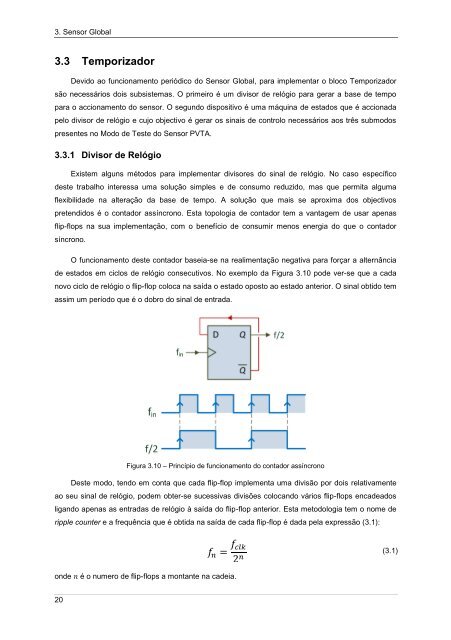

O funcionamento <strong>de</strong>ste conta<strong>do</strong>r baseia-se na realimentação negativa <strong>para</strong> forçar a alternância<br />

<strong>de</strong> esta<strong>do</strong>s em ciclos <strong>de</strong> relógio consecutivos. No exemplo da Figura 3.10 po<strong>de</strong> ver-se que a cada<br />

novo ciclo <strong>de</strong> relógio o flip-flop coloca na saída o esta<strong>do</strong> oposto ao esta<strong>do</strong> anterior. O sinal obti<strong>do</strong> tem<br />

assim um perío<strong>do</strong> que é o <strong>do</strong>bro <strong>do</strong> sinal <strong>de</strong> entrada.<br />

Figura 3.10 – Princípio <strong>de</strong> funcionamento <strong>do</strong> conta<strong>do</strong>r assíncrono<br />

Deste mo<strong>do</strong>, ten<strong>do</strong> em conta que cada flip-flop implementa uma divisão por <strong>do</strong>is relativamente<br />

ao seu sinal <strong>de</strong> relógio, po<strong>de</strong>m obter-se sucessivas divisões colocan<strong>do</strong> vários flip-flops enca<strong>de</strong>a<strong>do</strong>s<br />

ligan<strong>do</strong> apenas as entradas <strong>de</strong> relógio à saída <strong>do</strong> flip-flop anterior. Esta meto<strong>do</strong>logia tem o nome <strong>de</strong><br />

ripple counter e a frequência que é obtida na saída <strong>de</strong> cada flip-flop é dada pela expressão (3.1):<br />

f = f lk<br />

(3.1)<br />

on<strong>de</strong><br />

é o numero <strong>de</strong> flip-flops a montante na ca<strong>de</strong>ia.<br />

20