Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

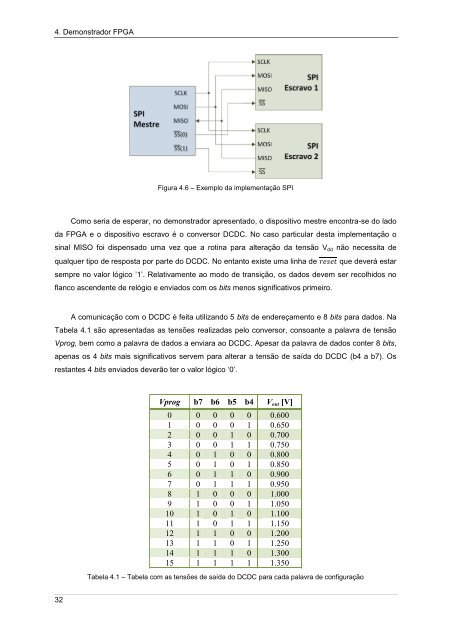

4. Demonstra<strong>do</strong>r FPGA<br />

Figura 4.6 – Exemplo da implementação SPI<br />

Como seria <strong>de</strong> esperar, no <strong>de</strong>monstra<strong>do</strong>r apresenta<strong>do</strong>, o dispositivo mestre encontra-se <strong>do</strong> la<strong>do</strong><br />

da FPGA e o dispositivo escravo é o conversor DCDC. No caso particular <strong>de</strong>sta implementação o<br />

sinal MISO foi dispensa<strong>do</strong> uma vez que a rotina <strong>para</strong> alteração da tensão V dd não necessita <strong>de</strong><br />

qualquer tipo <strong>de</strong> resposta por parte <strong>do</strong> DCDC. No entanto existe uma linha <strong>de</strong> que <strong>de</strong>verá estar<br />

sempre no valor lógico ’1’. Relativamente ao mo<strong>do</strong> <strong>de</strong> transição, os da<strong>do</strong>s <strong>de</strong>vem ser recolhi<strong>do</strong>s no<br />

flanco ascen<strong>de</strong>nte <strong>de</strong> relógio e envia<strong>do</strong>s com os bits menos significativos primeiro.<br />

A comunicação com o DCDC é feita utilizan<strong>do</strong> 5 bits <strong>de</strong> en<strong>de</strong>reçamento e 8 bits <strong>para</strong> da<strong>do</strong>s. Na<br />

Tabela 4.1 são apresentadas as tensões realizadas pelo conversor, consoante a palavra <strong>de</strong> tensão<br />

Vprog, bem como a palavra <strong>de</strong> da<strong>do</strong>s a enviara ao DCDC. Apesar da palavra <strong>de</strong> da<strong>do</strong>s conter 8 bits,<br />

apenas os 4 bits mais significativos servem <strong>para</strong> alterar a tensão <strong>de</strong> saída <strong>do</strong> DCDC (b4 a b7). Os<br />

restantes 4 bits envia<strong>do</strong>s <strong>de</strong>verão ter o valor lógico ‘0’.<br />

Vprog b7 b6 b5 b4 V out [V]<br />

0 0 0 0 0 0.600<br />

1 0 0 0 1 0.650<br />

2 0 0 1 0 0.700<br />

3 0 0 1 1 0.750<br />

4 0 1 0 0 0.800<br />

5 0 1 0 1 0.850<br />

6 0 1 1 0 0.900<br />

7 0 1 1 1 0.950<br />

8 1 0 0 0 1.000<br />

9 1 0 0 1 1.050<br />

10 1 0 1 0 1.100<br />

11 1 0 1 1 1.150<br />

12 1 1 0 0 1.200<br />

13 1 1 0 1 1.250<br />

14 1 1 1 0 1.300<br />

15 1 1 1 1 1.350<br />

Tabela 4.1 – Tabela com as tensões <strong>de</strong> saída <strong>do</strong> DCDC <strong>para</strong> cada palavra <strong>de</strong> configuração<br />

32