Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

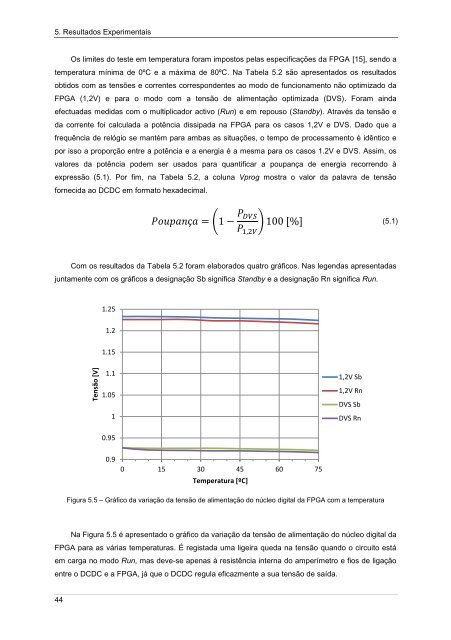

Tensão [V]<br />

5. Resulta<strong>do</strong>s Experimentais<br />

Os limites <strong>do</strong> teste em temperatura foram impostos pelas especificações da FPGA [15], sen<strong>do</strong> a<br />

temperatura mínima <strong>de</strong> 0ºC e a máxima <strong>de</strong> 80ºC. Na Tabela 5.2 são apresenta<strong>do</strong>s os resulta<strong>do</strong>s<br />

obti<strong>do</strong>s com as tensões e correntes correspon<strong>de</strong>ntes ao mo<strong>do</strong> <strong>de</strong> funcionamento não optimiza<strong>do</strong> da<br />

FPGA (1,2V) e <strong>para</strong> o mo<strong>do</strong> com a tensão <strong>de</strong> alimentação optimizada (DVS). Foram ainda<br />

efectuadas medidas com o multiplica<strong>do</strong>r activo (Run) e em repouso (Standby). Através da tensão e<br />

da corrente foi calculada a potência dissipada na FPGA <strong>para</strong> os casos 1,2V e DVS. Da<strong>do</strong> que a<br />

frequência <strong>de</strong> relógio se mantém <strong>para</strong> ambas as situações, o tempo <strong>de</strong> processamento é idêntico e<br />

por isso a proporção entre a potência e a energia é a mesma <strong>para</strong> os casos 1.2V e DVS. Assim, os<br />

valores da potência po<strong>de</strong>m ser usa<strong>do</strong>s <strong>para</strong> quantificar a poupança <strong>de</strong> energia recorren<strong>do</strong> à<br />

expressão (5.1). Por fim, na Tabela 5.2, a coluna Vprog mostra o valor da palavra <strong>de</strong> tensão<br />

fornecida ao DCDC em formato hexa<strong>de</strong>cimal.<br />

P = (<br />

P<br />

P 2<br />

) (5.1)<br />

Com os resulta<strong>do</strong>s da Tabela 5.2 foram elabora<strong>do</strong>s quatro gráficos. Nas legendas apresentadas<br />

juntamente com os gráficos a <strong>de</strong>signação Sb significa Standby e a <strong>de</strong>signação Rn significa Run.<br />

1.25<br />

1.2<br />

1.15<br />

1.1<br />

1,2V Sb<br />

1.05<br />

1<br />

1,2V Rn<br />

DVS Sb<br />

DVS Rn<br />

0.95<br />

0.9<br />

0 15 30 45 60 75<br />

Temperatura [ºC]<br />

Figura 5.5 – Gráfico da variação da tensão <strong>de</strong> alimentação <strong>do</strong> núcleo digital da FPGA com a temperatura<br />

Na Figura 5.5 é apresenta<strong>do</strong> o gráfico da variação da tensão <strong>de</strong> alimentação <strong>do</strong> núcleo digital da<br />

FPGA <strong>para</strong> as várias temperaturas. É registada uma ligeira queda na tensão quan<strong>do</strong> o circuito está<br />

em carga no mo<strong>do</strong> Run, mas <strong>de</strong>ve-se apenas à resistência interna <strong>do</strong> amperímetro e fios <strong>de</strong> ligação<br />

entre o DCDC e a FPGA, já que o DCDC regula eficazmente a sua tensão <strong>de</strong> saída.<br />

44