Simulação de Circuitos e Dispositivos Programáveis - PCS - USP

Simulação de Circuitos e Dispositivos Programáveis - PCS - USP

Simulação de Circuitos e Dispositivos Programáveis - PCS - USP

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

<br />

FPGA (Field Programmable Gate Array) – contém um gran<strong>de</strong> número <strong>de</strong> blocos lógicos que<br />

po<strong>de</strong>m ser programados in<strong>de</strong>pen<strong>de</strong>ntemente. Esses blocos contêm lógica combinatória e<br />

registradores para circuitos sequenciais;<br />

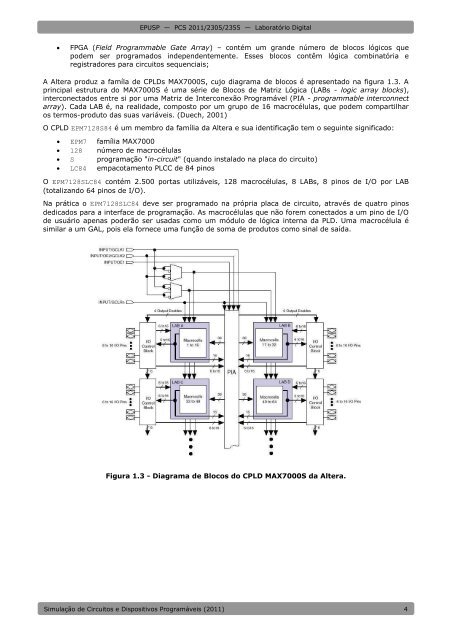

A Altera produz a famíla <strong>de</strong> CPLDs MAX7000S, cujo diagrama <strong>de</strong> blocos é apresentado na figura 1.3. A<br />

principal estrutura do MAX7000S é uma série <strong>de</strong> Blocos <strong>de</strong> Matriz Lógica (LABs - logic array blocks),<br />

interconectados entre si por uma Matriz <strong>de</strong> Interconexão Programável (PIA - programmable interconnect<br />

array). Cada LAB é, na realida<strong>de</strong>, composto por um grupo <strong>de</strong> 16 macrocélulas, que po<strong>de</strong>m compartilhar<br />

os termos-produto das suas variáveis. (Duech, 2001)<br />

O CPLD EPM7128S84 é um membro da família da Altera e sua i<strong>de</strong>ntificação tem o seguinte significado:<br />

EPM7 família MAX7000<br />

128 número <strong>de</strong> macrocélulas<br />

S programação "in-circuit" (quando instalado na placa do circuito)<br />

LC84 empacotamento PLCC <strong>de</strong> 84 pinos<br />

O EPM7128SLC84 contém 2.500 portas utilizáveis, 128 macrocélulas, 8 LABs, 8 pinos <strong>de</strong> I/O por LAB<br />

(totalizando 64 pinos <strong>de</strong> I/O).<br />

Na prática o EPM7128SLC84 <strong>de</strong>ve ser programado na própria placa <strong>de</strong> circuito, através <strong>de</strong> quatro pinos<br />

<strong>de</strong>dicados para a interface <strong>de</strong> programação. As macrocélulas que não forem conectados a um pino <strong>de</strong> I/O<br />

<strong>de</strong> usuário apenas po<strong>de</strong>rão ser usadas como um módulo <strong>de</strong> lógica interna da PLD. Uma macrocélula é<br />

similar a um GAL, pois ela fornece uma função <strong>de</strong> soma <strong>de</strong> produtos como sinal <strong>de</strong> saída.<br />

Figura 1.3 - Diagrama <strong>de</strong> Blocos do CPLD MAX7000S da Altera.<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 4