Beskrivning av Censor 932. Bilaga 1 till Rrgc/F del 2. - Försvarets ...

Beskrivning av Censor 932. Bilaga 1 till Rrgc/F del 2. - Försvarets ...

Beskrivning av Censor 932. Bilaga 1 till Rrgc/F del 2. - Försvarets ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

34<br />

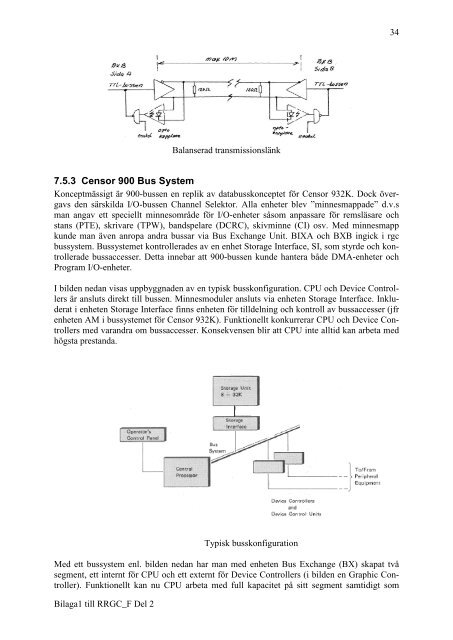

Balanserad transmissionslänk<br />

7.5.3 <strong>Censor</strong> 900 Bus System<br />

Konceptmässigt är 900-bussen en replik <strong>av</strong> databusskonceptet för <strong>Censor</strong> 932K. Dock överg<strong>av</strong>s<br />

den särskilda I/O-bussen Channel Selektor. Alla enheter blev ”minnesmappade” d.v.s<br />

man ang<strong>av</strong> ett speciellt minnesområde för I/O-enheter såsom anpassare för remsläsare och<br />

stans (PTE), skrivare (TPW), bandspelare (DCRC), skivminne (CI) osv. Med minnesmapp<br />

kunde man även anropa andra bussar via Bus Exchange Unit. BIXA och BXB ingick i rgc<br />

bussystem. Bussystemet kontrollerades <strong>av</strong> en enhet Storage Interface, SI, som styrde och kontrollerade<br />

bussaccesser. Detta innebar att 900-bussen kunde hantera både DMA-enheter och<br />

Program I/O-enheter.<br />

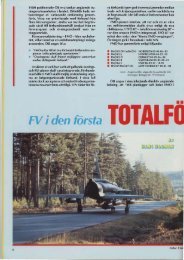

I bilden nedan visas uppbyggnaden <strong>av</strong> en typisk busskonfiguration. CPU och Device Controllers<br />

är ansluts direkt <strong>till</strong> bussen. Minnesmoduler ansluts via enheten Storage Interface. Inkluderat<br />

i enheten Storage Interface finns enheten för <strong>till</strong><strong>del</strong>ning och kontroll <strong>av</strong> bussaccesser (jfr<br />

enheten AM i bussystemet för <strong>Censor</strong> 932K). Funktionellt konkurrerar CPU och Device Controllers<br />

med varandra om bussaccesser. Konsekvensen blir att CPU inte alltid kan arbeta med<br />

högsta prestanda.<br />

Typisk busskonfiguration<br />

Med ett bussystem enl. bilden nedan har man med enheten Bus Exchange (BX) skapat två<br />

segment, ett internt för CPU och ett externt för Device Controllers (i bilden en Graphic Controller).<br />

Funktionellt kan nu CPU arbeta med full kapacitet på sitt segment samtidigt som<br />

<strong>Bilaga</strong>1 <strong>till</strong> RRGC_F Del 2