Beskrivning av Censor 932. Bilaga 1 till Rrgc/F del 2. - Försvarets ...

Beskrivning av Censor 932. Bilaga 1 till Rrgc/F del 2. - Försvarets ...

Beskrivning av Censor 932. Bilaga 1 till Rrgc/F del 2. - Försvarets ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

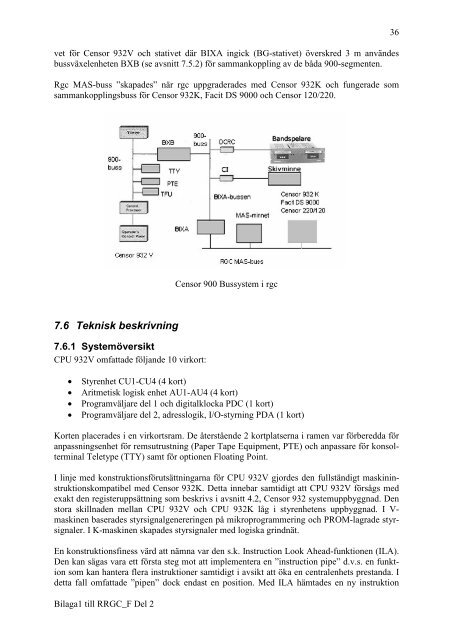

vet för <strong>Censor</strong> 932V och stativet där BIXA ingick (BG-stativet) överskred 3 m användes<br />

bussväxelenheten BXB (se <strong>av</strong>snitt 7.5.2) för sammankoppling <strong>av</strong> de båda 900-segmenten.<br />

Rgc MAS-buss ”skapades” när rgc uppgraderades med <strong>Censor</strong> 932K och fungerade som<br />

sammankopplingsbuss för <strong>Censor</strong> 932K, Facit DS 9000 och <strong>Censor</strong> 120/220.<br />

36<br />

<strong>Censor</strong> 900 Bussystem i rgc<br />

7.6 Teknisk beskrivning<br />

7.6.1 Systemöversikt<br />

CPU 932V omfattade följande 10 virkort:<br />

• Styrenhet CU1-CU4 (4 kort)<br />

• Aritmetisk logisk enhet AU1-AU4 (4 kort)<br />

• Programväljare <strong>del</strong> 1 och digitalklocka PDC (1 kort)<br />

• Programväljare <strong>del</strong> 2, adresslogik, I/O-styrning PDA (1 kort)<br />

Korten placerades i en virkortsram. De återstående 2 kortplatserna i ramen var förberedda för<br />

anpassningsenhet för remsutrustning (Paper Tape Equipment, PTE) och anpassare för konsolterminal<br />

Teletype (TTY) samt för optionen Floating Point.<br />

I linje med konstruktionsförutsättningarna för CPU 932V gjordes den fullständigt maskininstruktionskompatibel<br />

med <strong>Censor</strong> 932K. Detta innebar samtidigt att CPU 932V försågs med<br />

exakt den registeruppsättning som beskrivs i <strong>av</strong>snitt 4.2, <strong>Censor</strong> 932 systemuppbyggnad. Den<br />

stora skillnaden mellan CPU 932V och CPU 932K låg i styrenhetens uppbyggnad. I V-<br />

maskinen baserades styrsignalgenereringen på mikroprogrammering och PROM-lagrade styrsignaler.<br />

I K-maskinen skapades styrsignaler med logiska grindnät.<br />

En konstruktionsfiness värd att nämna var den s.k. Instruction Look Ahead-funktionen (ILA).<br />

Den kan sägas vara ett första steg mot att implementera en ”instruction pipe” d.v.s. en funktion<br />

som kan hantera flera instruktioner samtidigt i <strong>av</strong>sikt att öka en centralenhets prestanda. I<br />

detta fall omfattade ”pipen” dock endast en position. Med ILA hämtades en ny instruktion<br />

<strong>Bilaga</strong>1 <strong>till</strong> RRGC_F Del 2