Opis procesora

Opis procesora

Opis procesora

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

upravljačka linija magistrale FCBUS prelaze u stanje visoke impedanse. Po detektovanju<br />

vrednosti 0 signala FCBUS gazda na signal takta t j upisuje sadržaj sa linija podataka<br />

magistrale DBUS 7...0 u svoj prihvatni registar i zatvara svoje bafere sa tri stanja, pa adresne<br />

linije magistrale ABUS 15...0 i upravljačka linija magistrale RDBUS prelaze u stanje visoke<br />

impedanse. Time je ciklus čitanja na magistrali završen.<br />

Vremenski oblici signala na slici 15 levo odgovaraju ciklusu čitanja iz memorijskih<br />

lokacija za koje je uzeto da vreme pristupa traje odreĎen broj perioda signala takta. U slučaju<br />

ciklusa čitanja iz registara kontrolera ulazno/izlaznih ureĎaja uzeto je da vreme pristupa traje<br />

samo jednu perioda signala takta, pa se vremenski oblici signala sa slike15 levo redukuju na<br />

vremenske oblike signala sa slike 15 desno.<br />

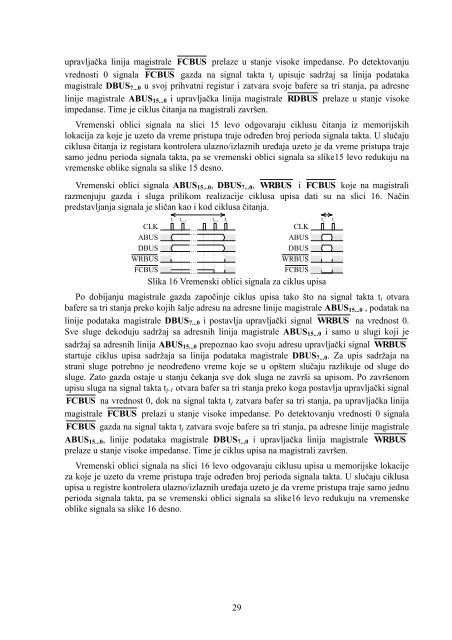

Vremenski oblici signala ABUS 15...0 , DBUS 7...0 , WRBUS i FCBUS koje na magistrali<br />

razmenjuju gazda i sluga prilikom realizacije ciklusa upisa dati su na slici 16. Način<br />

predstavljanja signala je sličan kao i kod ciklusa čitanja.<br />

CLK<br />

ABUS<br />

DBUS<br />

WRBUS<br />

FCBUS<br />

t i<br />

t i+1<br />

t j-1<br />

t j<br />

L<br />

L<br />

L<br />

L<br />

L<br />

CLK<br />

ABUS<br />

DBUS<br />

WRBUS<br />

FCBUS<br />

Slika 16 Vremenski oblici signala za ciklus upisa<br />

Po dobijanju magistrale gazda započinje ciklus upisa tako što na signal takta t i otvara<br />

bafere sa tri stanja preko kojih šalje adresu na adresne linije magistrale ABUS 15...0 , podatak na<br />

linije podataka magistrale DBUS 7...0 i postavlja upravljački signal WRBUS na vrednost 0.<br />

Sve sluge dekoduju sadržaj sa adresnih linija magistrale ABUS 15...0 i samo u slugi koji je<br />

sadržaj sa adresnih linija ABUS 15...0 prepoznao kao svoju adresu upravljački signal WRBUS<br />

startuje ciklus upisa sadržaja sa linija podataka magistrale DBUS 7...0 . Za upis sadržaja na<br />

strani sluge potrebno je neodreĎeno vreme koje se u opštem slučaju razlikuje od sluge do<br />

sluge. Zato gazda ostaje u stanju čekanja sve dok sluga ne završi sa upisom. Po završenom<br />

upisu sluga na signal takta t j-1 otvara bafer sa tri stanja preko koga postavlja upravljački signal<br />

FCBUS na vrednost 0, dok na signal takta t j zatvara bafer sa tri stanja, pa upravljačka linija<br />

magistrale FCBUS prelazi u stanje visoke impedanse. Po detektovanju vrednosti 0 signala<br />

FCBUS gazda na signal takta t j zatvara svoje bafere sa tri stanja, pa adresne linije magistrale<br />

ABUS 15...0 , linije podataka magistrale DBUS 7...0 i upravljačka linija magistrale WRBUS<br />

prelaze u stanje visoke impedanse. Time je ciklus upisa na magistrali završen.<br />

Vremenski oblici signala na slici 16 levo odgovaraju ciklusu upisa u memorijske lokacije<br />

za koje je uzeto da vreme pristupa traje odreĎen broj perioda signala takta. U slučaju ciklusa<br />

upisa u registre kontrolera ulazno/izlaznih ureĎaja uzeto je da vreme pristupa traje samo jednu<br />

perioda signala takta, pa se vremenski oblici signala sa slike16 levo redukuju na vremenske<br />

oblike signala sa slike 16 desno.<br />

t i<br />

t j<br />

29