Opis procesora

Opis procesora

Opis procesora

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

uprav<br />

uprav<br />

uprav<br />

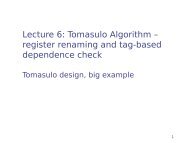

Ovi blokovi su meĎusobno povezani direktnim vezama.<br />

Blok bus (slika 18) služi za arbitraciju <strong>procesora</strong> i ulazno/izlaznog ureĎaja U/I2 sa<br />

kontrolerom za direktan pristup memoriji pri korišćenju magistrale BUS i realizaciju ciklusa<br />

na magistrali BUS. Blok fetch (slike 19, 20, 21) služi za čitanje instrukcije i smeštanje u<br />

prihvatni registar instrukcije. Blok addr (slika 22) služi za formiranje adrese operanda i<br />

čitanje operanda. Blok exec (slike 23, 24, 25 i 26) služi za izvršavanje operacija. Blok intr<br />

(slike 27, 28 i 29) služi za prihvatanje prekida i generisanje broja ulaza u tabelu sa adresama<br />

prekidnih rutina<br />

Struktura i opis blokova operacione jedinice oper se daju u daljem tekstu.<br />

4.1.1 Blok bus<br />

Blok bus (slika 18) sadrži registre MAR 15...0 i MDR 7...0 sa multiplekserima MX1 i MX2,<br />

respektivno, prihvatni registar DW 15...0 i kombinacione mreže za realizaciju ciklusa na<br />

magistrali BUS kada je procesor gazda i za arbitraciju sa kontrolerom sa direktnim pristupom<br />

memoriji pri korišćenju magistrale BUS.<br />

mxMAR 0<br />

mxMAR 1<br />

123<br />

mxMDR 0<br />

mxMDR 1<br />

123<br />

addr<br />

addr<br />

fetch<br />

addr<br />

fetch<br />

mxMAR 2<br />

16 2 1 0<br />

7<br />

16<br />

6<br />

16<br />

SP 15...0<br />

5<br />

16<br />

ADD 15...0<br />

4<br />

16 MX1<br />

DW 15...0<br />

3<br />

16<br />

IR 15...0<br />

2<br />

16<br />

GPR 15...0<br />

16 1<br />

PC 15...0<br />

0<br />

ldMAR<br />

incMAR<br />

123<br />

LD<br />

INC<br />

16<br />

16<br />

16<br />

uprav<br />

eMAR<br />

MAR<br />

16<br />

MAR 15...0<br />

mr<br />

MR<br />

CLK<br />

ABUS 15...0<br />

BUS<br />

mxMDR 2<br />

3<br />

8 2 1 0<br />

exec PSW 7...0<br />

7<br />

8<br />

execPSW 15...8<br />

6<br />

8<br />

fetch PC 7...0<br />

5<br />

8<br />

fetch PC 15...8<br />

4<br />

8 MX2<br />

exec AW 7...0<br />

8<br />

exec AW 15...8<br />

2 8<br />

8<br />

exec AB 7...0<br />

8 1<br />

BUS DBUS 7...0<br />

0<br />

uprav<br />

rdCPU ldMDR<br />

16 mr<br />

MR<br />

LD MDR CLK<br />

MDRin<br />

8 MDR fetch<br />

7...0<br />

uprav<br />

addr<br />

FCBUS<br />

eMDR<br />

fcCPU<br />

BUS<br />

uprav 8 DBUS 7...0<br />

BUS<br />

144424443<br />

1<br />

rdCPU<br />

uprav<br />

BUS<br />

RDBUS<br />

1<br />

wrCPU<br />

uprav<br />

BUS<br />

WRBUS<br />

U/I<br />

hreq<br />

eMAR<br />

uprav<br />

hack<br />

U/I<br />

uprav<br />

ldDWH<br />

uprav<br />

CLK<br />

LD<br />

MDR 7...0<br />

MDR 7...0<br />

8 mr<br />

8<br />

MR<br />

CLK<br />

DW<br />

ldDWL LD<br />

8 DW uprav<br />

15...8<br />

fetch<br />

8<br />

exec<br />

Slika 18 Blok bus<br />

DW<br />

MR<br />

DW 7...0<br />

mr<br />

fetch<br />

exec<br />

32