Synteza ukÅadów sekwencyjnych w strukturach FPGA z ...

Synteza ukÅadów sekwencyjnych w strukturach FPGA z ...

Synteza ukÅadów sekwencyjnych w strukturach FPGA z ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

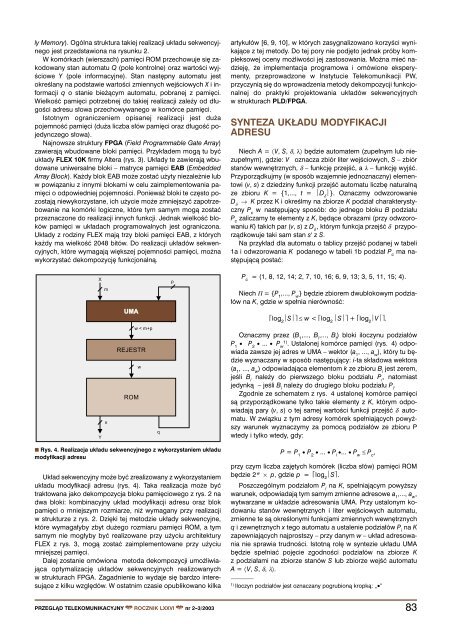

ly Memory). Ogólna struktura takiej realizacji układu sekwencyjnegojest przedstawiona na rysunku 2.W komórkach (wierszach) pamięci ROM przechowuje się zakodowanystan automatu Q (pole kontrolne) oraz wartości wyjścioweY (pole informacyjne). Stan następny automatu jestokreślany na podstawie wartości zmiennych wejściowych X iinformacjiq o stanie bieżącym automatu, pobranej z pamięci.Wielkość pamięci potrzebnej do takiej realizacji zależy od długościadresu słowa przechowywanego w komórce pamięci.Istotnym ograniczeniem opisanej realizacji jest dużapojemność pamięci (duża liczba słów pamięci oraz długość pojedynczegosłowa).Najnowsze struktury <strong>FPGA</strong> (Field Programmable Gate Array)zawierają wbudowane bloki pamięci. Przykładem mogą tu byćukłady FLEX 10K firmy Altera (rys. 3). Układy te zawierają wbudowaneuniwersalne bloki – matryce pamięci EAB (EmbeddedArray Block). Każdy blok EAB może zostać użyty niezależnie lubw powiązaniu z innymi blokami w celu zaimplementowania pamięcio odpowiedniej pojemności. Ponieważ bloki te często pozostająniewykorzystane, ich użycie może zmniejszyć zapotrzebowaniena komórki logiczne, które tym samym mogą zostaćprzeznaczone do realizacji innych funkcji. Jednak wielkość blokówpamięci w układach programowalnych jest ograniczona.Układy z rodziny FLEX mają trzy bloki pamięci EAB, z którychkażdy ma wielkość 2048 bitów. Do realizacji układów <strong>sekwencyjnych</strong>,które wymagają większej pojemności pamięci, możnawykorzystać dekompozycję funkcjonalną.artykułów [6, 9, 10], w których zasygnalizowano korzyści wynikającez tej metody. Do tej pory nie podjęto jednak próby kompleksowejoceny możliwości jej zastosowania. Można mieć nadzieję,że implementacja programowa i omówione eksperymenty,przeprowadzone w Instytucie Telekomunikacji PW,przyczynią się do wprowadzenia metody dekompozycji funkcjonalnejdo praktyki projektowania układów <strong>sekwencyjnych</strong>w <strong>strukturach</strong> PLD/<strong>FPGA</strong>.SYNTEZA UKŁADU MODYFIKACJIADRESUNiech A = 〈V, S, δ, λ〉 będzie automatem (zupełnym lub niezupełnym),gdzie: V oznacza zbiór liter wejściowych, S – zbiórstanów wewnętrznych, δ – funkcję przejść, a λ – funkcję wyjść.Przyporządkujmy (w sposób wzajemnie jednoznaczny) elementowi(v, s) z dziedziny funkcji przejść automatu liczbę naturalnąze zbioru K = {1,..., t = ⏐D δ⏐}. Oznaczmy odwzorowanieD δ→ K przez K i określmy na zbiorze K podział charakterystycznyP cw następujący sposób: do jednego bloku B podziałuP czaliczamy te elementy z K, będące obrazami (przy odwzorowaniuK) takich par (v, s) z D δ, którym funkcja przejść δ przyporządkowujetaki sam stan s' z S.Na przykład dla automatu o tablicy przejść podanej w tabeli1a i odwzorowania K podanego w tabeli 1b podział P cma następującąpostać:P c= (1, 8, 12, 14; 2, 7, 10, 16; 6, 9, 13; 3, 5, 11, 15; 4).Niech Π = {P 1,..., P w} będzie zbiorem dwublokowym podziałówna K, gdzie w spełnia nierówność:⎡log 2⏐S⏐⎤ ≤ w < ⎡log 2⏐S⏐⎤ + ⎡log 2⏐V⏐⎤.Oznaczmy przez (B 1,..., B i,..., B t) bloki iloczynu podziałówP 1• P 2• ... • P 1) w. Ustalonej komórce pamięci (rys. 4) odpowiadazawsze jej adres w UMA – wektor (a 1, ..., a w), który tu będziewyznaczany w sposób następujący: i-ta składowa wektora(a 1, ..., a w) odpowiadająca elementom k ze zbioru B ijest zerem,jeśli B inależy do pierwszego bloku podziału P i, natomiastjedynką – jeśli B inależy do drugiego bloku podziału P i.Zgodnie ze schematem z rys.4 ustalonej komórce pamięcisą przyporządkowane tylko takie elementy z K, którym odpowiadająpary (v, s) o tej samej wartości funkcji przejść δ automatu.W związku z tym adresy komórek spełniających powyższywarunek wyznaczymy za pomocą podziałów ze zbioru Pwtedy i tylko wtedy, gdy:O Rys. 4. Realizacja układu sekwencyjnego z wykorzystaniem układumodyfikacji adresuUkład sekwencyjny może być zrealizowany z wykorzystaniemukładu modyfikacji adresu (rys. 4). Taka realizacja może byćtraktowana jako dekompozycja bloku pamięciowego z rys. 2 nadwa bloki: kombinacyjny układ modyfikacji adresu oraz blokpamięci o mniejszym rozmiarze, niż wymagany przy realizacjiw strukturze z rys. 2. Dzięki tej metodzie układy sekwencyjne,które wymagałyby zbyt dużego rozmiaru pamięci ROM, a tymsamym nie mogłyby być realizowane przy użyciu architekturyFLEX z rys. 3, mogą zostać zaimplementowane przy użyciumniejszej pamięci.Dalej zostanie omówiona metoda dekompozycji umożliwiającaoptymalizację układów <strong>sekwencyjnych</strong> realizowanychw <strong>strukturach</strong> <strong>FPGA</strong>. Zagadnienie to wydaje się bardzo interesującez kilku względów. W ostatnim czasie opublikowano kilkaP = P 1• P 2• ... • P i•... • P w≤ P c,przy czym liczba zajętych komórek (liczba słów) pamięci ROMbędzie 2 w × p, gdzie p = ⎡log 2⏐S⎤ .Poszczególnym podziałom P ina K, spełniającym powyższywarunek, odpowiadają tym samym zmienne adresowe a 1,..., a w,wytwarzane w układzie adresowania UMA. Przy ustalonym kodowaniustanów wewnętrznych i liter wejściowych automatu,zmienne te są określonymi funkcjami zmiennych wewnętrznychq i zewnętrznych x tego automatu a ustalenie podziałów P ina Kzapewniających najprostszy – przy danym w – układ adresowanianie sprawia trudności. Istotną rolę w syntezie układu UMAbędzie spełniać pojęcie zgodności podziałów na zbiorze Kz podziałami na zbiorze stanów S lub zbiorze wejść automatuA = 〈V, S, δ, λ〉.––––––––1)Iloczyn podziałów jest oznaczany pogrubioną kropką: „•”PRZEGLĄD TELEKOMUNIKACYJNY ROCZNIK LXXVI nr 2--3/200383