Synteza ukÅadów sekwencyjnych w strukturach FPGA z ...

Synteza ukÅadów sekwencyjnych w strukturach FPGA z ...

Synteza ukÅadów sekwencyjnych w strukturach FPGA z ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

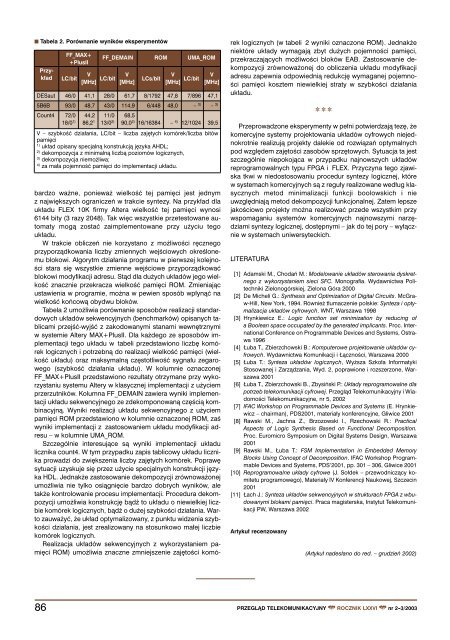

O Tabela 2. Porównanie wyników eksperymentówPrzykładFF_MAX++PlusIILC/bitV[MHz] LC/bitFF_DEMAIN ROM UMA_ROMV[MHz]LCs/bitV[MHz] LC/bitV[MHz]DESaut 46/0 41,1 28/0 61,7 8/1792 47,8 7/896 47,15B6B 93/0 48,7 43/0 114,9 6/448 48,0 – 3) – 3)Count4 72/0 44,2 11/0 68,518/0 1) 86,2 1 13/0 2) 90,0 2) 16/16384 – 4) 12/1024 39,5V – szybkość działania, LC/bit – liczba zajętych komórek/liczba bitówpamięci1) układ opisany specjalną konstrukcją języka AHDL;2) dekompozycja z minimalną liczbą poziomów logicznych,3) dekompozycja niemożliwa;4) za mała pojemność pamięci do implementacji układu.bardzo ważne, ponieważ wielkość tej pamięci jest jednymz największych ograniczeń w trakcie syntezy. Na przykład dlaukładu FLEX 10K firmy Altera wielkość tej pamięci wynosi6144 bity (3 razy 2048). Tak więc wszystkie przetestowane automatymogą zostać zaimplementowane przy użyciu tegoukładu.W trakcie obliczeń nie korzystano z możliwości ręcznegoprzyporządkowania liczby zmiennych wejściowych określonemublokowi. Algorytm działania programu w pierwszej kolejnościstara się wszystkie zmienne wejściowe przyporządkowaćblokowi modyfikacji adresu. Stąd dla dużych układów jego wielkośćznacznie przekracza wielkość pamięci ROM. Zmieniającustawienia w programie, można w pewien sposób wpłynąć nawielkość końcową obydwu bloków.Tabela 2 umożliwia porównanie sposobów realizacji standardowychukładów <strong>sekwencyjnych</strong> (benchmarków) opisanych tablicamiprzejść-wyjść z zakodowanymi stanami wewnętrznymiw systemie Altery MAX+PlusII. Dla każdego ze sposobów implementacjitego układu w tabeli przedstawiono liczbę komóreklogicznych i potrzebną do realizacji wielkość pamięci (wielkośćukładu) oraz maksymalną częstotliwość sygnału zegarowego(szybkość działania układu). W kolumnie oznaczonejFF_MAX+PlusII przedstawiono rezultaty otrzymane przy wykorzystaniusystemu Altery w klasycznej implementacji z użyciemprzerzutników. Kolumna FF_DEMAIN zawiera wyniki implementacjiukładu sekwencyjnego ze zdekomponowaną częścią kombinacyjną.Wyniki realizacji układu sekwencyjnego z użyciempamięci ROM przedstawiono w kolumnie oznaczonej ROM, zaśwyniki implementacji z zastosowaniem układu modyfikacji adresu– w kolumnie UMA_ROM.Szczególnie interesujące są wyniki implementacji układulicznika count4. W tym przypadku zapis tablicowy układu licznikaprowadzi do zwiększenia liczby zajętych komórek. Poprawęsytuacji uzyskuje się przez użycie specjalnych konstrukcji językaHDL. Jednakże zastosowanie dekompozycji zrównoważonejumożliwia nie tylko osiągnięcie bardzo dobrych wyników, aletakże kontrolowanie procesu implementacji. Procedura dekompozycjiumożliwia konstrukcję bądź to układu o niewielkiej liczbiekomórek logicznych, bądź o dużej szybkości działania. Wartozauważyć, że układ optymalizowany, z punktu widzenia szybkościdziałania, jest zrealizowany na stosunkowo małej liczbiekomórek logicznych.Realizacja układów <strong>sekwencyjnych</strong> z wykorzystaniem pamięciROM) umożliwia znaczne zmniejszenie zajętości komóreklogicznych (w tabeli 2 wyniki oznaczone ROM). Jednakżeniektóre układy wymagają zbyt dużych pojemności pamięci,przekraczających możliwości bloków EAB. Zastosowanie dekompozycjizrównoważonej do obliczenia układu modyfikacjiadresu zapewnia odpowiednią redukcję wymaganej pojemnościpamięci kosztem niewielkiej straty w szybkości działaniaukładu.✽ ✽ ✽Przeprowadzone eksperymenty w pełni potwierdzają tezę, żekomercyjne systemy projektowania układów cyfrowych niejednokrotnierealizują projekty dalekie od rozwiązań optymalnychpod względem zajętości zasobów sprzętowych. Sytuacja ta jestszczególnie niepokojąca w przypadku najnowszych układówreprogramowalnych typu <strong>FPGA</strong> i FLEX. Przyczyna tego zjawiskatkwi w niedostosowaniu procedur syntezy logicznej, którew systemach komercyjnych są z reguły realizowane według klasycznychmetod minimalizacji funkcji boolowskich i nieuwzględniają metod dekompozycji funkcjonalnej. Zatem lepszejakościowo projekty można realizować przede wszystkim przywspomaganiu systemów komercyjnych najnowszymi narzędziamisyntezy logicznej, dostępnymi – jak do tej pory – wyłączniew systemach uniwersyteckich.LITERATURA[1] Adamski M., Chodań M.: Modelowanie układów sterowania dyskretnegoz wykorzystaniem sieci SFC. Monografia. Wydawnictwa PolitechnikiZielonogórskiej, Zielona Góra 2000[2] De Micheli G.: Synthesis and Optimization of Digital Circuits. McGraw-Hill,New York, 1994. Również tłumaczenie polskie: <strong>Synteza</strong> i optymalizacjaukładów cyfrowych. WNT, Warszawa 1998[3] Hrynkiewicz E.: Logic function set minimization by reducing ofa Boolean space occupated by the generated implicants. Proc. InternationalConference on Programmable Devices and Systems, Ostrawa1996[4] Łuba T., Zbierzchowski B.: Komputerowe projektowanie układów cyfrowych.Wydawnictwa Komunikacji i Łączności, Warszawa 2000[5] Łuba T.: <strong>Synteza</strong> układów logicznych, Wyższa Szkoła InformatykiStosowanej i Zarządzania, Wyd. 2, poprawione i rozszerzone, Warszawa2001[6] Łuba T., Zbierzchowski B., Zbysiński P.: Układy reprogramowalne dlapotrzeb telekomunikacji cyfrowej. Przegląd Telekomunikacyjny i WiadomościTelekomunikacyjne, nr 5, 2002[7] IFAC Workshop on Programmable Devices and Systems (E. Hrynkiewicz– chairman), PDS2001, materiały konferencyjne, Gliwice 2001[8] Rawski M., Jachna Z., Brzozowski I., Rzechowski R.: PracticalAspects of Logic Synthesis Based on Functional Decomposition.Proc. Euromicro Symposium on Digital Systems Design, Warszawa2001[9] Rawski M., Łuba T.: FSM Implementation in Embedded MemoryBlocks Using Concept of Decomposition. IFAC Workshop ProgrammableDevices and Systems, PDS’2001, pp. 301 – 306, Gliwice 2001[10] Reprogramowalne układy cyfrowe (J. Sołdek – przewodniczący komitetuprogramowego), Materiały IV Konferencji Naukowej, Szczecin2001[11] Łach J.: <strong>Synteza</strong> układów <strong>sekwencyjnych</strong> w <strong>strukturach</strong> <strong>FPGA</strong> z wbudowanymiblokami pamięci. Praca magisterska, Instytut TelekomunikacjiPW, Warszawa 2002Artykuł recenzowany(Artykuł nadesłano do red. – grudzień 2002)86 PRZEGLĄD TELEKOMUNIKACYJNY ROCZNIK LXXVI nr 2--3/2003