Infos zu Inkrementalgeber

Infos zu Inkrementalgeber

Infos zu Inkrementalgeber

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

ENCOD, J. Best, WS2000/01 Seite 6<br />

sich das Eingangssignal nicht ändern darf. Wird diese Bedingung verletzt, so kann das<br />

Flipflop in einen metastabilen Zustand geraten: Der Ausgang des Flipflops nimmt nicht nach<br />

der spezifizierten Zeit den Pegel des Eingangs an, sondern kann sich für eine gewisse Zeit<br />

nicht entscheiden, ob es nun 0 oder 1 werden will. In Bild 9 ist für das Signal A1 ein solcher<br />

Zustand dargestellt. Die Dauer dieses metastabilen Zustands lässt sich nicht genau angeben,<br />

sondern ist eine statistische Größe. So gibt es nur eine (hoffentlich sehr große) Wahrscheinlichkeit<br />

dafür, dass dieser Zustand bis <strong>zu</strong>r nächsten Taktflanke, wenn das nachgeschaltete<br />

Flipflop übernimmt, abgeklungen ist. Damit ist es dann sehr unwahrscheinlich, dass auch A2<br />

metastabil wird. Die Wahrscheinlichkeit, dass der metastabile Zustand bis <strong>zu</strong>r nächsten positiven<br />

Taktflanke abgeklungen ist, ist natürlich um so größer, je niedriger die Taktfrequenz<br />

fCLK ist. Man wird deshalb fCLK nicht unnötig groß wählen.<br />

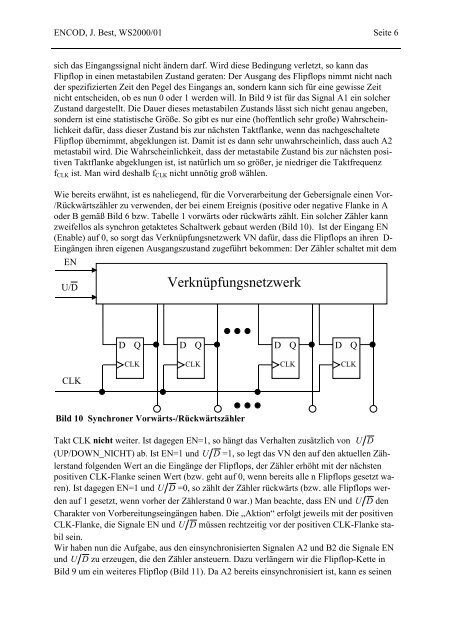

Wie bereits erwähnt, ist es naheliegend, für die Vorverarbeitung der Gebersignale einen Vor-<br />

/Rückwärtszähler <strong>zu</strong> verwenden, der bei einem Ereignis (positive oder negative Flanke in A<br />

oder B gemäß Bild 6 bzw. Tabelle 1 vorwärts oder rückwärts zählt. Ein solcher Zähler kann<br />

zweifellos als synchron getaktetes Schaltwerk gebaut werden (Bild 10). Ist der Eingang EN<br />

(Enable) auf 0, so sorgt das Verknüpfungsnetzwerk VN dafür, dass die Flipflops an ihren D-<br />

Eingängen ihren eigenen Ausgangs<strong>zu</strong>stand <strong>zu</strong>geführt bekommen: Der Zähler schaltet mit dem<br />

EN<br />

U/D<br />

CLK<br />

D Q<br />

CLK<br />

Verknüpfungsnetzwerk<br />

D Q<br />

CLK<br />

Bild 10 Synchroner Vorwärts-/Rückwärtszähler<br />

D Q<br />

D Q<br />

Takt CLK nicht weiter. Ist dagegen EN=1, so hängt das Verhalten <strong>zu</strong>sätzlich von U D<br />

(UP/DOWN_NICHT) ab. Ist EN=1 und U D =1, so legt das VN den auf den aktuellen Zählerstand<br />

folgenden Wert an die Eingänge der Flipflops, der Zähler erhöht mit der nächsten<br />

positiven CLK-Flanke seinen Wert (bzw. geht auf 0, wenn bereits alle n Flipflops gesetzt waren).<br />

Ist dagegen EN=1 und U D =0, so zählt der Zähler rückwärts (bzw. alle Flipflops werden<br />

auf 1 gesetzt, wenn vorher der Zählerstand 0 war.) Man beachte, dass EN und U D den<br />

Charakter von Vorbereitungseingängen haben. Die „Aktion“ erfolgt jeweils mit der positiven<br />

CLK-Flanke, die Signale EN und U D müssen rechtzeitig vor der positiven CLK-Flanke stabil<br />

sein.<br />

Wir haben nun die Aufgabe, aus den einsynchronisierten Signalen A2 und B2 die Signale EN<br />

und U D <strong>zu</strong> erzeugen, die den Zähler ansteuern. Da<strong>zu</strong> verlängern wir die Flipflop-Kette in<br />

Bild 9 um ein weiteres Flipflop (Bild 11). Da A2 bereits einsynchronisiert ist, kann es seinen<br />

CLK<br />

CLK