Teil 16 - LRR

Teil 16 - LRR

Teil 16 - LRR

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

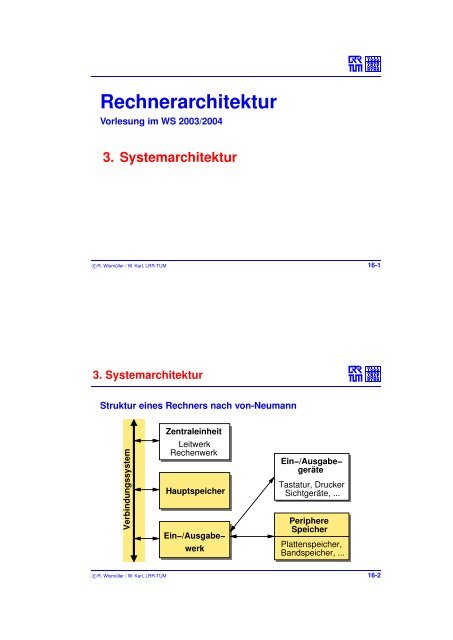

Rechnerarchitektur<br />

Vorlesung im WS 2003/2004<br />

3. Systemarchitektur<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-1<br />

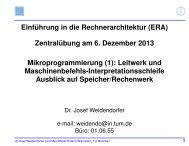

3. Systemarchitektur<br />

Struktur eines Rechners nach von-Neumann<br />

Verbindungssystem<br />

Zentraleinheit<br />

Leitwerk<br />

Rechenwerk<br />

Hauptspeicher<br />

Ein−/Ausgabe−<br />

werk<br />

Ein−/Ausgabe−<br />

geräte<br />

Tastatur, Drucker<br />

Sichtgeräte, ...<br />

Periphere<br />

Speicher<br />

Plattenspeicher,<br />

Bandspeicher, ...<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-2<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

Inhalt<br />

3. Systemarchitektur<br />

1. Speicher und Busse<br />

➥ Halbleiterspeicher<br />

➥ Bussysteme<br />

➥ Leistungssteigerung<br />

➥ Bushierarchie<br />

2. Ein-/Ausgabe<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-3<br />

Rechnerarchitektur<br />

Vorlesung im WS 2003/2004<br />

3. Systemarchitektur<br />

3.1. Speicher und Busse<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-4<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.1. Halbleiterspeicher<br />

Arten von Halbleiterspeichern, Speichertechnik<br />

➥ statisches RAM (SRAM): Flip-Flops<br />

➥ schnell und teuer, aufwendig, für Caches<br />

➥ dynamisches RAM (DRAM): Ladung in Kondensatoren<br />

➥ Leckströme: periodisches Auffrischen nötig, langsamer<br />

➥ hohe Speicherdichte, billig, für Hauptspeicher<br />

➥ EPROM, EEPROM: Ladung in isoliertem Gate<br />

➥ Einbringen der Ladung durch hohe Spannung<br />

➥ Löschen: durch UV-Licht (EPROM), oder elektrisch<br />

(EEPROM, Flash ROM)<br />

➥ Informationserhaltung auch ohne Betriebsspannung<br />

➥ PROM: zerstörbare Sicherungen<br />

➥ ROM: elektrische Verbindungen bei der Chip-Herstellung<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-5<br />

3.1.1. Halbleiterspeicher ...<br />

Aufbau einer DRAM-Zelle<br />

Transistor<br />

Kondensator<br />

Auswahlleitung<br />

Bitleitung<br />

➥ Lesen ist zerstörend, daher Rückschreiben notwendig<br />

➥ Zykluszeit (Zeit zwischen aufeinanderfolgenden Zugriffen) ist<br />

größer als die Zugriffszeit<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-6<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.1. Halbleiterspeicher ...<br />

RAS<br />

CAS<br />

Aufbau eines DRAM-Bausteins<br />

Adresse<br />

n<br />

Register für<br />

Zeilenadresse<br />

Register für<br />

Spaltenadresse<br />

Adreßdekoder<br />

...<br />

Matrix<br />

aus<br />

DRAM<br />

Zellen<br />

...<br />

Leseverstärker<br />

Schreiblogik<br />

Spalten−MUX/<br />

DEMUX<br />

Daten<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

Adresse aufgeteilt in<br />

Zeilen− und Spalten−<br />

adresse, im Multiplex−<br />

betrieb über dieselben<br />

Leitungen übertragen<br />

RAS = Row address<br />

strobe<br />

WE<br />

CAS = Column address<br />

strobe<br />

WE = Write enable<br />

Intern wird immer eine<br />

ganze Zeile gelesen!<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-7<br />

3.1.1. Halbleiterspeicher ...<br />

Zugriffsprotokoll bei DRAMs<br />

➥ Ablauf eines Lesezugriffs:<br />

➥ Anlegen der Zeilenadresse, RAS aktivieren<br />

➥ Anlegen der Spaltenadresse, CAS aktivieren<br />

➥ Ausgabe der Daten<br />

➥ Rückschreiben der gelesenen Zeile<br />

➥ Nachfolgende Zugriffe auf Zellen in derselben Zeile (page)<br />

können schneller erfolgen<br />

➥ nibble mode, page mode, static column mode, ...<br />

➥ ausgenutzt z.B. durch längere Cache-Zeilen<br />

➥ beim Laden: Zugriffe auf aufeinanderfolgende Adressen<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-8<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.2. Bussysteme<br />

Definition und Eigenschaften<br />

➥ Ein Bus ist ein gemeinsamer Datenpfad (Leitungsbündel), der<br />

mehrere (≥ 2) Einheiten eines Rechers verbindet<br />

➥ Die Einheiten heißen Busteilnehmer<br />

➥ aktive Busteilnehmer (Bus Master) können Datentransfers<br />

einleiten<br />

➥ passive Busteilnehmer (Slaves) reagieren nur auf Anfragen<br />

➥ Ein Bus ist ein exklusives Betriebsmittel<br />

➥ zu jedem Zeitpunkt kann nur ein Busteilnehmer den Bus<br />

aktiv steuern<br />

➥ Ein Bus ist ein Broadcast-Medium<br />

➥ Daten auf dem Bus können von allen Busteilnehmern<br />

gleichzeitig gelesen werden<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-9<br />

3.1.2. Bussysteme ...<br />

Arten von Bussen<br />

➥ Serielle Busse: Datenübertragung erfolgt bitweise seriell<br />

➥ zur Anbindung externer Peripherie (z.B. USB, Firewire)<br />

➥ im Netzwerkbereich (z.B. Ethernet)<br />

➥ Parallele Busse: Datenübertragung erfolgt wortweise über<br />

mehrere Leitungen<br />

➥ Cache- und Speicherbusse: Speicheranbindung<br />

➥ i.a. stark prozessorabhängig<br />

➥ Peripheriebusse<br />

➥ z.B. PCI, SBus, ...<br />

➥ Rückwandbusse<br />

➥ standardisierte Busse für modulare Rechnersysteme<br />

➥ z.B. CompactPCI, Futurebus, ...<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-10<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.2. Bussysteme ...<br />

Typischer Aufbau eines parallelen Busses<br />

Adreßbus<br />

Steuerbus<br />

Datenbus<br />

Arbitrierung<br />

Interrupts<br />

Versorgung<br />

Busteil− Busteil− Busteil−<br />

nehmer nehmer nehmer<br />

1 2<br />

3<br />

(aktiv) (aktiv) (passiv)<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

Busteil−<br />

nehmer<br />

4<br />

(passiv)<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-11<br />

Rechnerarchitektur<br />

Vorlesung im WS 2003/2004<br />

29.01.04<br />

Roland Wismüller, <strong>LRR</strong>-TUM<br />

wismuell@in.tum.de, Tel.: 289-17676, Büro: 01.04.061<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-12<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

Wo waren wir?<br />

➥ Virtuelle Speicherverwaltung<br />

➥ Segmentierung, seitenbasierte Speicherverwaltung<br />

➥ mehrstufige Seiten-/Kacheltabellen<br />

➥ Einsatz von Caches: TLBs<br />

➥ Spezialisierte Mikroprozessoren<br />

➥ Mobile Prozessoren, Mikrocontroller, Signalprozessoren<br />

➥ Systemarchitektur<br />

➥ DRAMs: intern immer ganze Zeile gelesen<br />

➥ Bus:<br />

➥ gemeinsame Verbindung mehrerer Busteilnehmer<br />

➥ exklusives Betriebsmittel, Broadcast-Medium<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-13<br />

3.1.2. Bussysteme ...<br />

Architekturmerkmale von Bussen<br />

➥ Breite des Datenbusses<br />

➥ breiterer Datenbus ⇒ höherer Durchsatz, aber auch<br />

höherer Hardwareaufwand<br />

➥ bei Cache- und Speicherbussen heute meist: ≥ 64 Bits,<br />

bis zu 512 Bits bei Hochleistungs-Servern<br />

➥ Betriebsart von Adreß- und Datenbus<br />

➥ getrennte Leitungen<br />

➥ gemeinsame Leitungen im Zeitmultiplex<br />

➥ weniger Aufwand, langsamer<br />

➥ z.B. bei Peripheriebussen<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-14<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.2. Bussysteme ...<br />

Architekturmerkmale von Bussen ...<br />

➥ Transfergröße<br />

➥ wird mit einer Bustransaktion nur ein Wort übertragen oder<br />

mehrere?<br />

➥ Übertragung mehrerer Worte (Blocktransfer) ist effizienter,<br />

aber aufwendiger<br />

➥ Multimaster-Fähigkeit<br />

➥ kann es mehrere aktive Busteilnehmer geben, die<br />

Bustransaktionen initiieren können?<br />

➥ erfordert Mechanismen zur Buszuteilung (Arbitrierung)<br />

➥ zentrale oder dezentrale Verfahren<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-15<br />

3.1.2. Bussysteme ...<br />

Beispiel für zentrale Busarbitrierung<br />

Bus−<br />

Arbiter<br />

1<br />

aktive Busteilnehmer<br />

2<br />

3<br />

BRQ1<br />

BRQ2<br />

BRQ3<br />

BGT1<br />

BGT2<br />

BGT3<br />

BUSY<br />

Bus Request<br />

Anfrage<br />

Bus Grant<br />

Zuteilung<br />

Bus belegt<br />

Adreß−/Datenbus<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-<strong>16</strong><br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.2. Bussysteme ...<br />

Architekturmerkmale von Bussen ...<br />

➥ Zeitliche Steuerung<br />

➥ synchrone Busse<br />

➥ alle Bustransaktionen durch zentralen Takt gesteuert<br />

➥ einfachere Abläufe<br />

➥ nur Busteilnehmer mit ausreichender Geschwindigkeit<br />

➥ begrenzte Ausdehnung und Skalierbarkeit<br />

➥ i.a. bei Cache- und Speicher-Bussen<br />

➥ asynchrone Busse<br />

➥ explizite zeitliche Steuerung (Handshaking)<br />

➥ komplexere Bustransaktionen<br />

➥ auch langsame Busteilnehmer möglich<br />

➥ bei einigen Peripherie- und Rückwandbussen<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-17<br />

3.1.2. Bussysteme ...<br />

Beispiel für synchrones Busprotokoll<br />

Takt<br />

Adresse<br />

MREQ<br />

RD<br />

WAIT<br />

Daten<br />

T1<br />

T2<br />

Signal innerhalb vorgeschriebener Zeit nach der Taktflanke gültig sein<br />

Signal muß eine bestimmte Zeit vor der Taktflanke gültig sein<br />

T3<br />

Speicher−<br />

Adreßraum<br />

Lesen<br />

vom Slave<br />

bitte warten<br />

Daten vom<br />

Slave<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

Adresse vom<br />

Master<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-18

3.1.2. Bussysteme ...<br />

Beispiel für asynchrones Busprotokoll<br />

Adresse<br />

MREQ<br />

RD<br />

MSYN<br />

Daten<br />

SSYN<br />

Kausalitätsbeziehungen<br />

Speicher−<br />

adreßraum<br />

Lesen<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

Adresse vom<br />

Master<br />

Master: alle<br />

Signale gültig<br />

Daten vom<br />

Slave<br />

Slave: alle<br />

Signale gültig<br />

Ablauf des "Handshaking"<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-19<br />

3.1.2. Bussysteme ...<br />

Architekturmerkmale von Bussen ...<br />

➥ Geteilte Transaktionen / Pipelining<br />

➥ ein ” normaler“ Bus ist während der gesamten Transaktion<br />

belegt<br />

➥ schlechte Auslastung, v.a. bei Lese-Transaktionen<br />

➥ bei geteilten Transaktionen:<br />

➥ die Bustransaktion werden in Phasen aufgeteilt<br />

➥ jede der Phasen verwendet unterschiedliche Signale<br />

auf dem Bus<br />

➥ somit ist eine Überlappung dieser Phasen möglich<br />

➥ z.B. kann bereits die Adresse des nächsten Zugriffs auf<br />

den Bus gelegt werden, bevor der vorangegangene<br />

beendet ist<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-20<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.2. Bussysteme ...<br />

Beispiel für Buspipelining: Intel P6-Prozessorbus<br />

Takt<br />

Arbitrierung<br />

Adresse<br />

Request<br />

Fehler<br />

Snoop<br />

Response<br />

Daten<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

0 1 2 3 4 5 6 7 8 9 10 11 12 13<br />

max. 8 Transaktionen gleichzeitig<br />

Datenbus: 64 Bit + 8 Prüfbits<br />

Blocktransfer!<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-21<br />

3.1.2. Bussysteme ...<br />

Architekturmerkmale von Bussen ...<br />

➥ Geteilte Transaktionen / Pipelining ...<br />

➥ Pipelining muß von allen Busteilnehmern unterstützt<br />

werden<br />

➥ z.B. Pipelining im Prozessor, Interleaving im<br />

Speichersystem (☞ 3.1.3)<br />

➥ Leistungsgewinn, aber höherer Aufwand<br />

➥ Varianten:<br />

➥ in-order Abarbeitung der Anfragen<br />

➥ out-of-order Abarbeitung der Anfragen<br />

➥ höherer Gewinn möglich, aufwendiger<br />

➥ höhere Latenz, da Adreß- und Datenbus getrennt<br />

arbitriert werden müssen<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-22<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.3. Leistungssteigerung<br />

➥ Synchrones Busprotokoll<br />

➥ senkt i.a. die Latenz<br />

➥ Höhere Taktrate<br />

➥ senkt die Latenz, erhöht die Bandbreite<br />

➥ elektrische Realisierung sehr aufwendig (Leitungstheorie!)<br />

➥ beschränkt Länge des Busses und Anzahl der <strong>Teil</strong>nehmer<br />

➥ Breiter Datenbus und Speicher<br />

➥ erhöht die Bandbreite<br />

➥ technisch einfach, aber teuer<br />

➥ ermöglicht durch große Länge der Cache-Zeilen<br />

➥ z.B. bei Sun Enterprise 6000 Server: 256 Bit breiter<br />

Datenbus, 512 Bit breiter Speicher<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-23<br />

3.1.3. Leistungssteigerung ...<br />

➥ Blocktransfer<br />

➥ erhöht die Bandbreite<br />

➥ Einsparung von Adreßübertragungen, Nutzung spezieller<br />

DRAM-Modi (nibble mode, page mode, ...)<br />

➥ Optimierte Arbitrierungsverfahren<br />

➥ senken die Latenz<br />

➥ bus parking<br />

➥ letzter Master behält Bus, falls keine andere Anforderung<br />

➥ verteilte Arbitrierung<br />

➥ kann schneller sein, da Kommunikation mit zentralem<br />

Arbiter entfällt<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-24<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.3. Leistungssteigerung ...<br />

➥ Speicherverschränkung (Interleaving) und Buspipelining<br />

➥ erhöht die Bandbreite<br />

➥ Idee: aufeinanderfolgende Speicherworte werden auf<br />

verschiedene Speicherbänke verteilt<br />

➥ überlappte Zugriffe auf die Speicherbänke möglich<br />

➥ insbesondere Zugriffe auf aufeinanderfolgende Worte<br />

➥ Beispiel (2-fache Verschränkung, Prinzip):<br />

Datenbus (64 Bit)<br />

Bank 1:<br />

Worte 1,3,5, ...<br />

Speicher<br />

(64 Bit breit)<br />

Speicher<br />

(64 Bit breit)<br />

Bank 0:<br />

Worte<br />

0,2,4,...<br />

Adreßbus (Bits 4...n)<br />

Freigabe<br />

Adreßbit 3<br />

Freigabe<br />

&<br />

1<br />

&<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-25<br />

3.1.3. Leistungssteigerung ...<br />

➥ Speicherverschränkung ...<br />

➥ bei passender Prozessorarchitektur hohe Anzahl von<br />

Speicherbänken möglich<br />

➥ z.B. 256 Speicherbänke beim Vektorrechner NEC SX/4,<br />

Durchsatz 512 GB/s<br />

➥ wird auch innerhalb von Speicherbausteinen verwendet:<br />

SDRAMs (Synchronous DRAM)<br />

➥ SDRAM besteht intern aus 2-4 verschränkten<br />

Speicherbänken<br />

➥ synchrones Zugriffsprotokoll mit Pipelining<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-26<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.1.4. Bushierarchie<br />

➥ Heutige Recher: Hierarchische Busorganisation<br />

➥ schnelle, breite Busse zu Caches / Speicher<br />

➥ langsamere Busse für Anbindung von E/A-Geräten<br />

➥ Verbindung der Busse über Busbrücken<br />

➥ Insbesodere bei PC-Architekturen: prozessorspezifische<br />

Chipsätze realisieren<br />

➥ Speicheranbindung (DRAM-Controller)<br />

➥ Brücken zu Peripheriebussen<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-27<br />

3.1.4. Bushierarchie ...<br />

Beispiel:Bushierarchie in einem PC<br />

L2<br />

Cache<br />

Lokaler<br />

Speicher<br />

E/A<br />

USB<br />

L2 Cache<br />

Interface<br />

E/A−Bus<br />

L1 Befehls−<br />

Cache<br />

Graphik−<br />

beschleu−<br />

niger<br />

PCI<br />

AGP<br />

CPU Kern<br />

Systembus−Interface<br />

Chip−<br />

satz<br />

E/A−Bus<br />

L1 Daten−<br />

Cache<br />

CPU<br />

Haupt−<br />

speicher<br />

ISA / EISA<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

E/A E/A<br />

Bus−<br />

Brücke<br />

E/A E/A<br />

IDE Ethernet<br />

Parallel RS232<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-28

3.2. Ein-/Ausgabe<br />

Arten von Ein-/Ausgabegeräten<br />

➥ Zeichenorientierte Geräte<br />

➥ Ein-/Ausgabe erfolgt zeichenweise (byteweise)<br />

➥ typisch für Dialoggeräte<br />

➥ z.B.: Tastatur, Bildschirm, Maus, Drucker<br />

➥ Blockorientierte Geräte<br />

➥ Ein-/Ausgabe größerer Datenblöcke<br />

➥ Blockgröße typisch 256 Byte - einige KByte<br />

➥ typisch für Netzwerk-Anbindung und Externspeicher<br />

➥ z.B.: Festplatte, Magnetband, CD-ROM, Diskette, ...<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-29<br />

3.2 Ein-/Ausgabe ...<br />

Anbindung von Ein-/Ausgabegeräten an den Rechner<br />

➥ In der Regel über Controller<br />

➥ spezielle Hardware, oft mit eigenen Mikroprozessoren<br />

➥ erhält Kommando und Daten vom Hauptprozessor (CPU)<br />

➥ führt Kommando autonom aus, steuert Gerät<br />

➥ meldet Ende d. Ausführung durch Unterbrechung der CPU<br />

➥ Zweck der Controller<br />

➥ Entlastung der CPU<br />

➥ Realisierung zeitkritischer Steueraufgaben<br />

➥ Beispiel: Ethernet-Controller<br />

➥ Serien/Parallel-Wandlung der Daten, Sicherung der<br />

Übertragung durch Prüfbits, Kollisionserkennung, ...<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-30<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.2 Ein-/Ausgabe ...<br />

DMA (Direct Memory Access)<br />

➥ Idee:<br />

➥ Für blockorientierte Geräte: Datenblock wird nicht von der<br />

CPU vom Speicher zum Geräte-Controller kopiert, sondern<br />

durch speziellen DMA-Controller<br />

➥ CPU sendet an DMA-Controller nur die Anfangsadresse<br />

und die Länge des Datenblocks<br />

➥ Vorteil: weitere Entlastung der CPU<br />

➥ CPU und DMA-Controller arbeiten parallel<br />

➥ Realisierungsvarianten:<br />

➥ DMA-Controller als eigenständige Einheit<br />

➥ Geräte-Controller mit DMA-Fähigkeit<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-31<br />

3.2 Ein-/Ausgabe ...<br />

DMA (Direct Memory Access) ...<br />

➥ Sowohl DMA-Controller als auch CPU greifen über den Bus<br />

auf den Speicher zu<br />

➥ erfordert Bus mit Multimaster-Fähigkeit<br />

➥ mögliche Inkonsistenzen durch Caches<br />

➥ DMA-Controller schreibt Daten direkt in den<br />

Hauptspeicher, Cache enthält evtl. noch alte Kopie<br />

➥ Bei rückschreibenden Caches: DMA-Controller liest<br />

evtl. noch alte Daten aus Hauptspeicher<br />

➥ einfache Lösungen:<br />

➥ Löschen der Caches bzw. einzelner Einträge<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

➥ über MMU Caching für betroffene Seiten abschalten<br />

➥ heute übliche Lösung: Cachekohärenzprotokolle (☞ 4.2.)<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-32

3.2 Ein-/Ausgabe ...<br />

Hintergrundspeicher<br />

➥ Einsatz:<br />

➥ Erweiterung des Hauptspeichers (virtueller Speicher,<br />

☞ 2.5.4.)<br />

➥ dauerhafte Speicherung größerer Datenmengen<br />

➥ Archivierung von Daten<br />

➥ Häufigste Verfahren:<br />

➥ magnetische Aufzeichnung<br />

➥ Festplatte, Magnetband, Diskette, ...<br />

➥ optische Aufzeichnung<br />

➥ CD-ROM, DVD, CD-R, CD-RW, ...<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-33<br />

3.2 Ein-/Ausgabe ...<br />

Magnetische Aufzeichnung<br />

➥ Daten werden in dünner magnetisierbarer Schicht gespeichert<br />

➥ Schicht sitzt auf Trägermaterial (Kunststofffolie, Alu-Platte)<br />

➥ zwei verschiedene Magnetisierungsrichtungen für 0 und 1<br />

➥ Schreiben/Lesen durch Magnetkopf (Elektromagnet)<br />

1 1 0<br />

Magnetschicht<br />

(mit Richtung der<br />

Magnetisierung)<br />

Trägermaterial<br />

Schreibstrom<br />

Lesestrom<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-34<br />

1<br />

0<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.2 Ein-/Ausgabe ...<br />

Magnetische Aufzeichnung ...<br />

➥ Beim Lesen: nur Wechsel der Magnetisierungsrichtung ergibt<br />

ein Signal<br />

➥ Problem: zeitliche Synchronisation bei langer Folge<br />

identischer Bits<br />

➥ ” wann hört ein Bit auf und wann fängt das nächste an?“<br />

➥ Daher Verwendung spezieller Codierungen bei der<br />

Aufzeichnung<br />

➥ stellen sicher, daß unabhängig von den aufgezeichneten<br />

Daten genügend Wechsel der Magnetisierungsrichtung<br />

vorliegen<br />

➥ Zusätzlich: Einfügen von Prüfbits zur Fehlererkennung<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-35<br />

3.2 Ein-/Ausgabe ...<br />

Festplatten: Aufbau<br />

Sektor<br />

Plattenstapel<br />

Spur<br />

Schreib−/Leseköpfe<br />

Arm<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-36<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.2 Ein-/Ausgabe ...<br />

Festplatten: Aufbau ...<br />

➥ Schreib-/Leseköpfe fliegen über der Plattenoberfläche<br />

➥ Pro Platte des Plattenstapels zwei Köpfe: oben und unten<br />

➥ Spurwechesel durch Verschieben des Arms (d.h. aller Köpfe)<br />

➥ Menge der jeweils übereinanderliegenden Spuren: Zylinder<br />

➥ Einteilung der Festplatte (Adressierung):<br />

➥ Oberfläche (Kopf), Zylinder, Sektor<br />

➥ jeder Sektor nimmt einen Datenblock auf<br />

➥ typisches Beispiel (80 GByte Laptop-Festplatte):<br />

➥ 4 Oberflächen, ∼ 47000 Zylinder, ∼ 800 Sektoren<br />

➥ 512 Byte pro Sektor<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-37<br />

3.2 Ein-/Ausgabe ...<br />

Festplatten: weitere Eigenschaften<br />

➥ Zugriffszeit abhängig von<br />

➥ Spurwechselzeit (typisch 0.5 ... 5 ms)<br />

➥ Umdrehungszahl (typisch 5400 ... 15000 U/min)<br />

➥ typische Zugriffszeit: ∼ 10 ms<br />

➥ Leistungssteigerung<br />

➥ Caches (typisch einige MByte, in Festplatten-Elektronik)<br />

➥ RAID (Redundant Array of Inexpensive Disks)<br />

➥ Datenblöcke werden über mehrere Festplatten verteilt<br />

➥ paralleler Zugriff möglich (wie beim Hauptspeicher)<br />

➥ durch redundante Speicherung: kein Datenverlust bei<br />

Ausfall einer Festplatte<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-38<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛

3.2 Ein-/Ausgabe ...<br />

Optische Speichermedien: CD-ROM / CD-R / CD-RW<br />

➥ Datenspeicherung durch ca. 1 µm große Vertiefungen (Pits)<br />

➥ Optische Abtastung durch Laserlicht<br />

Pit Pit Pit<br />

➥ Erzeugung der Pits:<br />

Laserstrahl Laserstrahl<br />

❛<br />

❛<br />

❛ ❛ ❛ ❛<br />

Aluminiumschicht<br />

CD (Kunststoff)<br />

➥ CD-ROM: mechanisch durch Presse (Massenherstellung!)<br />

➥ CD-R: Metallisierung und Farbstoff, der durch starkes<br />

Laserlicht (Hitze) sein Absorptionsverhalten ändert<br />

➥ CD-RW: kristalline Schicht, ändert Reflexionsverhalten<br />

c○R. Wismüller / W. Karl, <strong>LRR</strong>-TUM <strong>16</strong>-39