Hilfsblätter zur Übung (PDF, 176KB)

Hilfsblätter zur Übung (PDF, 176KB)

Hilfsblätter zur Übung (PDF, 176KB)

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

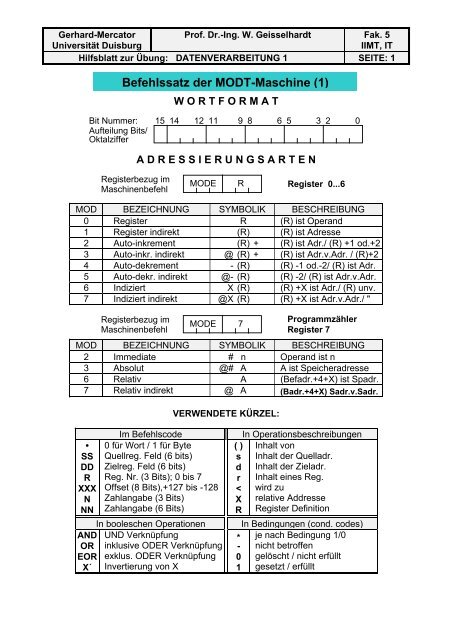

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 1<br />

Bit Nummer:<br />

Aufteilung Bits/<br />

Oktalziffer<br />

Registerbezug im<br />

Maschinenbefehl<br />

W O R T F O R M A T<br />

15 14 12 11 9 8 6 5 3 2 0<br />

A D R E S S I E R U N G S A R T E N<br />

MODE R Register 0...6<br />

MOD BEZEICHNUNG SYMBOLIK BESCHREIBUNG<br />

0 Register R (R) ist Operand<br />

1 Register indirekt (R) (R) ist Adresse<br />

2 Auto-inkrement (R) + (R) ist Adr./ (R) +1 od.+2<br />

3 Auto-inkr. indirekt @ (R) + (R) ist Adr.v.Adr. / (R)+2<br />

4 Auto-dekrement - (R) (R) -1 od.-2/ (R) ist Adr.<br />

5 Auto-dekr. indirekt @- (R) (R) -2/ (R) ist Adr.v.Adr.<br />

6 Indiziert X (R) (R) +X ist Adr./ (R) unv.<br />

7 Indiziert indirekt @X (R) (R) +X ist Adr.v.Adr./ "<br />

Registerbezug im<br />

Maschinenbefehl<br />

MODE 7<br />

Programmzähler<br />

Register 7<br />

MOD BEZEICHNUNG SYMBOLIK BESCHREIBUNG<br />

2 Immediate # n Operand ist n<br />

3 Absolut @# A A ist Speicheradresse<br />

6 Relativ A (Befadr.+4+X) ist Spadr.<br />

7 Relativ indirekt @ A (Badr.+4+X) Sadr.v.Sadr.<br />

•<br />

SS<br />

DD<br />

R<br />

XXX<br />

N<br />

NN<br />

AND<br />

OR<br />

EOR<br />

X´<br />

Befehlssatz der MODT-Maschine (1)<br />

VERWENDETE KÜRZEL:<br />

Im Befehlscode In Operationsbeschreibungen<br />

0 für Wort / 1 für Byte<br />

Quellreg. Feld (6 bits)<br />

Zielreg. Feld (6 bits)<br />

Reg. Nr. (3 Bits); 0 bis 7<br />

Offset (8 Bits),+127 bis -128<br />

Zahlangabe (3 Bits)<br />

Zahlangabe (6 Bits)<br />

( )<br />

s<br />

d<br />

r<br />

<<br />

X<br />

R<br />

Inhalt von<br />

Inhalt der Quelladr.<br />

Inhalt der Zieladr.<br />

Inhalt eines Reg.<br />

wird zu<br />

relative Addresse<br />

Register Definition<br />

In booleschen Operationen In Bedingungen (cond. codes)<br />

UND Verknüpfung<br />

inklusive ODER Verknüpfung<br />

exklus. ODER Verknüpfung<br />

Invertierung von X<br />

*<br />

-<br />

0<br />

1<br />

je nach Bedingung 1/0<br />

nicht betroffen<br />

gelöscht / nicht erfüllt<br />

gesetzt / erfüllt

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 2<br />

Befehlssatz der MODT-Maschine (2)<br />

EINOPERANDENBEFEHLE / MONADISCHE BEFEHLE:<br />

OPCODE dst<br />

15 6 5 0<br />

OP CODE DD<br />

Mnemonik Bef.Code Befehlsbeschreibung<br />

A l l g e m e i n<br />

Ergebnis N Z V C<br />

CLR(B) •050DD clear (clear byte) 0<br />

0 1 0 0<br />

COM(B) •051DD complement (1's) NOT (d) * * 0 1<br />

INC(B) •052DD increment<br />

d + 1 * * * -<br />

DEC(B) •053DD decrement<br />

d - 1 * * * -<br />

NEG(B) •054DD negate (2's complemt.) - d<br />

* * * *<br />

TST(B) •057DD test<br />

d<br />

* * 0 0<br />

R O T I E R E N & S C H I E B E N<br />

ROR(B) •060DD rotate right<br />

> C, d * * * *<br />

ROL(B) •061DD rotate left<br />

C, d < * * * *<br />

ASR(B) •062DD arithmetic shift right d / 2 * * * *<br />

ASL(B) •063DD arithmetic shift left 2 * d * * * *<br />

SWAP 0003DD swap bytes<br />

dHB dLB * * * 0<br />

M E H R W O R T G E N A U I G K E I T<br />

ADC(B) •055DD add carry<br />

d + C * * * *<br />

SBC(B) •056DD subtract carry<br />

d - C * * * *<br />

SXT 0067DD sign extend<br />

0 or -1 - * 0 -<br />

ZWEIOPERANDENBEFEHLE / DYADISCHE BEFEHLE:<br />

OPCODE src,dst OPCODE src,R / OPCODE R,dst<br />

15 12 11<br />

6 5 0 15 9 8 6 5 0<br />

OP CODE SS<br />

DD<br />

OP CODE R SS or DD<br />

Mnemonik Bef.Code Befehlsbeschreibung<br />

A l l g e m e i n<br />

Ergebnis N Z V C<br />

MOV(B) •1SSDD move<br />

d < s * * 0 -<br />

CMP(B) •2SSDD compare<br />

s - d * * * *<br />

ADD 06SSDD add<br />

d < s + d * * * *<br />

SUB 16SSDD subtract<br />

L O G I S C H<br />

d < d - s * * * *<br />

BIT(B) •3SSDD bit test (AND)<br />

s AND d * * 0 -<br />

BIC(B) •4SSDD bit clear<br />

d < s' AND d * * 0 -<br />

BIS(B) •5SSDD bit set (OR)<br />

R E G I S T E R<br />

d < s OR d * * 0 -<br />

MUL 070RSS multiply<br />

r < r · s * * 0 *<br />

DIV 071RSS divide<br />

r < r / s * * * *<br />

ASH 072RSS shift arithmetically r < s shifts (r) * * * *<br />

ASHC 073RSS arithm. shift combined r < s shifts(rr) * * * *<br />

XOR 074RDD exclusive OR<br />

d < r EOR d * * 0 -

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 3<br />

Befehlssatz der MODT-Maschine (3)<br />

VERZWEIGUNGEN: B--- Adresse<br />

Die Berechnung der Zieladresse erfolgt in folgenden Schritten:<br />

- Nehme Adresse des PC nach Einlesen des Befehls;<br />

dies ist die Befehlsadresse + 2<br />

- Addiere darauf im Zweierkomplement den doppelten Offset<br />

- XXX ist der Offset<br />

15 8 7<br />

0<br />

BASE CODE X X X<br />

Befehlscode = Base Code + X X X<br />

Mnemonik BaseCode Befehlsbeschreibung<br />

V E R Z W E I G U N G E N<br />

Bemerkung<br />

BR<br />

000400 branch (unconditional) (always)<br />

BNE<br />

001000 br if not equal (to 0) NOT 0 Z=0<br />

BEQ 001400 br if equal (to 0) = 0<br />

Z=1<br />

BPL<br />

100000 branch if plus<br />

+<br />

N=0<br />

BMI<br />

100400 branch if minus<br />

-<br />

N=1<br />

BVC<br />

102000 br if overflow is clear<br />

V=0<br />

BVS<br />

102400 br if overflow is set<br />

V=1<br />

BCC 103000 br if carry is clear<br />

C=0<br />

BCS<br />

103400 br if carry is set<br />

C=1<br />

ZAHLENBEZOGENE BEDINGTE VERZWEIGUNGEN<br />

BGE 002000 br if greater/eq (to 0) N EOR V = 0<br />

BLT<br />

002400 br if less than (0) N EOR V = 1<br />

BGT<br />

003000 br if greater than (0) Z OR (N EOR V)=0<br />

BLE<br />

003400 br if less or equal (0) Z OR (N EOR V)=1<br />

WERTBEZOGENE BEDINGTE VERZWEIGUNGEN<br />

BHI<br />

101000 branch if higher<br />

C OR Z = 0<br />

BLOS 101400 branch if lower or same C OR Z = 1<br />

BHIS 103000 branch if higher or same C = 0<br />

BLO<br />

103400 branch if lower<br />

C = 1<br />

JUMP & SUBROUTINE:<br />

Mnemonik BaseCode Befehlsbeschreibung Bemerkung<br />

JMP 0001DD jump (PC) < dst<br />

JSR 004RDD jump to subroutine use same R<br />

RTS 00020R return from subroutine use same R<br />

SOB 077RNN subtr. 1 & br (if NOT 0) (R) - 1<br />

(PC) := (PC) - (2 * NN) if (R) NOT 0

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 4<br />

Befehlssatz der MODT-Maschine (4)<br />

BEFEHLE DIE AUF DIE BEDINGUNGSFLAGS WIRKEN:<br />

15 5 4 3 2 1 0<br />

OP CODE BASE = 00240 N<br />

SETZE SELEKTIERTES BIT ZURÜCK<br />

SETZE SELEKTIERTES BIT<br />

= 0<br />

= 1<br />

Z V C<br />

SELEKT.<br />

BIT<br />

Mnemonik Bef.Code Befehlsbeschreibung N Z V C<br />

CLC 00241 clear C - - - 0<br />

CLV 00242 clear V - - 0 -<br />

CLZ 00244 clear Z - 0 - -<br />

CLN 00250 clear N 0 - - -<br />

CCC 00257 clear all cc bits 0 0 0 0<br />

SEC 000261 set C - - - 1<br />

SEV 000262 set V - - 1 -<br />

SEZ 000264 set Z - 1 - -<br />

SEN 000270 set N 1 - - -<br />

SCC 000277 set all cc bits 1 1 1 1<br />

ASCII Code Tabelle (oktal codiert)<br />

000 nul 001 soh 002 stx 003 etx 004 eot 005 enq 006 ack 007 bel<br />

010 bs 011 ht 012 nl 013 vt 014 np 015 cr 016 so 017 si<br />

020 dle 021 dc1 022 dc2 023 dc3 024 dc4 025 nak 026 syn 027 etb<br />

030 can 031 em 032 sub 033 esc 034 fs 035 gs 036 rs 037 us<br />

040 sp 041 ! 042 " 043 # 044 $ 045 % 046 & 047 '<br />

050 ( 051 ) 052 * 053 + 054 , 055 - 056 . 057 /<br />

060 0 061 1 062 2 063 3 064 4 065 5 066 6 067 7<br />

070 8 071 9 072 : 073 ; 074 < 075 = 076 > 077 ?<br />

100 @ 101 A 102 B 103 C 104 D 105 E 106 F 107 G<br />

110 H 111 I 112 J 113 K 114 L 115 M 116 N 117 O<br />

120 P 121 Q 122 R 123 S 124 T 125 U 126 V 127 W<br />

130 X 131 Y 132 Z 133 [ 134 \ 135 ] 136 ^ 137 _<br />

140 ` 141 a 142 b 143 c 144 d 145 e 146 f 147 g<br />

150 h 151 i 152 j 153 k 154 l 155 m 156 n 157 o<br />

160 p 161 q 162 r 163 s 164 t 165 u 166 v 167 w<br />

170 x 171 y 172 z 173 { 174 | 175 } 176 ~ 177 del

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 5<br />

Datenpfad: mikroprogrammierte Nulladreßmaschine<br />

PC<br />

19<br />

20<br />

Speicher der Maschinenebene<br />

MAR<br />

IR<br />

MBR<br />

SP A B C D<br />

15<br />

X<br />

18<br />

27<br />

2<br />

21<br />

3<br />

Linksverschub<br />

23<br />

22<br />

38<br />

4 5 6 15 16 17<br />

+1<br />

1<br />

7<br />

0<br />

14<br />

8<br />

13<br />

Einerkomplement<br />

9<br />

-1<br />

12<br />

Einerkomplement<br />

28 10 SIGN 11<br />

29<br />

16-bit Dualaddierer<br />

1-bit Verschub<br />

30 31<br />

39<br />

24 25<br />

32 33 34 35 36 37<br />

26<br />

Rechtsverschub

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 6<br />

Kontrollpfad: mikroprogrammierte Nulladreßmaschine<br />

vom<br />

Datenpfad<br />

zum<br />

Datenpfad<br />

Register & Bit Auswahl<br />

:<br />

:<br />

R<br />

B<br />

A<br />

=<br />

:<br />

:<br />

:<br />

:<br />

>1<br />

:<br />

:<br />

M<br />

U<br />

X<br />

0<br />

1<br />

:<br />

:<br />

24<br />

25<br />

26<br />

:<br />

33<br />

:<br />

39<br />

MIR<br />

:<br />

:<br />

:<br />

:<br />

+1<br />

M<br />

P<br />

C<br />

Adreßdecoder<br />

Mikroprogramm<br />

Speicher<br />

256 X 40 Bit

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 7<br />

Mikrobefehlsformat der Beispielmaschine<br />

Gate/Bit Nummer:<br />

GATE Bef.<br />

33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br />

34<br />

35<br />

36<br />

37<br />

38<br />

39<br />

1<br />

Nummer der Gates im Datenpfad<br />

Bit Nummer:<br />

JUMP Bef.<br />

33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br />

34<br />

35<br />

36<br />

37<br />

38<br />

39<br />

n o u s e<br />

0 I X M D C B A 0<br />

Bit Wert<br />

IR MBR<br />

Zieladresse Bitnummer<br />

Register<br />

Maschinenbefehle der emulierten Nulladreßmaschine<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

Bit Nummer:<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

Bit Nummer:<br />

A d r e s s e<br />

0<br />

1<br />

1<br />

CALL<br />

A d r e s s e<br />

0<br />

0<br />

0<br />

PUSH<br />

0 0 0 0 0 0 0 0 0 0 0 0 0<br />

1<br />

1<br />

1<br />

ADD<br />

A d r e s s e<br />

1<br />

0<br />

0<br />

POP<br />

0 0 0 0 0 0 0 0 0 0 0 0 1<br />

1<br />

1<br />

1<br />

SUB<br />

A d r e s s e<br />

0<br />

1<br />

0<br />

JMP<br />

0 0 0 0 0 0 0 0 0 0 0 1 0<br />

1<br />

1<br />

1<br />

MUL<br />

A d r e s s e<br />

1<br />

1<br />

0<br />

JNEG<br />

0 0 0 0 0 0 0 0 0 0 0 1 1<br />

1<br />

1<br />

1<br />

DIV<br />

A d r e s s e<br />

0<br />

0<br />

1<br />

JZER<br />

0 0 0 0 0 0 0 0 0 0 1 0 0<br />

1<br />

1<br />

1<br />

RETURN<br />

A d r e s s e<br />

1<br />

0<br />

1<br />

JPOS

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 8<br />

Adr. Label Statements<br />

Adr. Label Statements<br />

40 MULDIV: IF BIT(0,IR) = 1 THEN GO TO DIV;<br />

41 MUL: MAR = SP; SP = SP + (-1); MBR= MEMORY (MAR);<br />

42 C = MBR; MAR = SP; MBR = MEMORY(MAR);<br />

43 X = 15; A = 0 + 0; D = 0 + 0;<br />

44 IF BIT(15,MBR) = 0 THEN GO TO MULLOOP;<br />

45 MBR = COM(MBR) + 1;<br />

46 B = MBR; MBR = 1 + COM(C);<br />

47 C = MBR; MBR = 0 + B;<br />

48 MULLOOP: IF BIT(0,MBR) = 0 THEN GO TO NOADD;<br />

49 A = A + C;<br />

50 NOADD: MBR = RIGHT_SHIFT(MBR + 0);<br />

51 D = RIGHT_SHIFT(0 + D);<br />

52 IF BIT(0,A) = 0 THEN GO TO NOCARRY;<br />

53 D = SIGN + D;<br />

54 NOCARRY: A = RIGHT_SHIFT(A + 0);<br />

55 IF BIT(15,C) = 0 THEN GO TO MULEND;<br />

56 IF BIT(14,A) = 0 THEN GO TO MULEND;<br />

57 A = A + SIGN;<br />

58 MULEND: X = X + (-1)<br />

59 IF BIT(15,X) = 0 THEN GO TO MULLOOP;<br />

60 MBR = 0 + D; MEMORY(MAR) = MBR;<br />

61 GO TO MAINLOOP;<br />

62 DIV: MAR=SP; SP= SP + (-1); MBR= MEMORY (MAR);<br />

63 C = MBR; B = MBR; MAR = SP; A = 0 + 0; MBR = MEMORY(MAR);<br />

64 D = MBR; MBR = COM(MBR) + 1; X = 15;<br />

65 IF BIT(15,MBR) = 1 THEN GO TO DVPOS;<br />

66 D = MBR; MBR = COM(B) + 1<br />

67 B = MBR;<br />

68 DVPOS: MBR = 1 + COM(C);<br />

69 IF BIT(15,C) = 0 THEN GO TO DIVLOOP;<br />

70 C = MBR; MBR = COM(MBR) + 1;<br />

71 DIVLOOP: A = LEFT_SHIFT(A + 0);<br />

72 IF BIT(15,D) = 0 THEN GO TO NOCARRY2;<br />

73 A = A + 1;<br />

74 NOCARRY2 D = LEFT_SHIFT(0 + D);<br />

75 A = A + MBR;<br />

76 IF BIT(15,A) = 1 THEN GO TO DIVNEG;<br />

77 D = D + 1;<br />

78 DIVNEG: IF BIT(15,A) = 0 THEN GO TO DIVPOS;<br />

79 A = A + C;<br />

80 DIVPOS: X = X + (-1)<br />

81 IF BIT(15,X) = 0 THEN GO TO DIVLOOP;<br />

82 F BIT(15,B) = 0 THEN GO TO DIVEND;<br />

83 D = 1 + COM(D);<br />

84 DIVEND: MBR = 0 + D, MEMORY(MAR) = MBR;<br />

85 GO TO MAINLOOP;<br />

86 RETURN: MAR=SP; SP= SP + (-1); MBR= MEMORY (MAR);<br />

87 IR = MBR;<br />

88 GO TO JUMP;<br />

0 MAINLOOP: MAR= PC; MBR= MEMORY (MAR); /* FETCH NEXT TARGET INSTR */<br />

1 IR= MBR; PC= PC + 1; /* MOVE INSTR TO IR AND ADVANCE PC */<br />

2 IF BIT(15,IR)= 1 THEN GO TO OP4567; /* DETERMINE TYPE */<br />

3 IF BIT(14,IR)= 1 THEN GO TO OP23;<br />

4 IF BIT(13,IR)= 1 THEN GO TO POP;<br />

5 PUSH: MAR=IR; SP= SP + 1; MBR= MEMORY (MAR);<br />

6 MAR=SP; MEMORY (MAR) = MBR;<br />

7 GO TO MAINLOOP;<br />

8 POP: MAR=SP; SP= SP + (-1); MBR= MEMORY (MAR);<br />

9 MAR=IR; MEMORY(MAR) = MBR; /* MAR=IR IS 13 BITS WIDE */<br />

10 GO TO MAINLOOP;<br />

11 OP23: IF BIT(13,IR) = 1 THEN GO TO JNEG;<br />

12 JUMP: PC=IR; /* THIS DATA PATH IS 13 BITS WIDE */<br />

13 GO TO MAINLOOP;<br />

14 JNEG: MAR=SP; SP= SP + (-1); MBR= MEMORY (MAR);<br />

15 IF BIT (15,MBR) = 1 THEN GO TO JUMP;<br />

16 GO TO MAINLOOP;<br />

17 OP4567: IF BIT(14,IR)= 1 THEN GO TO OP67;<br />

18 IF BIT(13,IR)= 1 THEN GO TO JPOS;<br />

19 JZER: X=15; MAR = SP; SP = SP + (-1); MBR= MEMORY(MAR);<br />

20 JLOOP: IF BIT (15,MBR) = 1 THEN GO TO MAINLOOP;<br />

21 MBR = LEFT_SHIFT(MBR+0);<br />

22 X = X + (-1)<br />

23 IF BIT (15,X) = 0 THEN GO TO JLOOP;<br />

24 GO TO JUMP;<br />

25 JPOS: MAR=SP; SP= SP + (-1); MBR= MEMORY (MAR);<br />

26 IF BIT (15,MBR) = 0 THEN GO TO JUMP;<br />

27 GO TO MAINLOOP;<br />

28 OP67: IF BIT (13,IR) = 1 THEN GO TO OP7;<br />

29 CALL: SP= SP + 1;<br />

30 MAR = SP; MBR = PC + 0; MEMORY(MAR) = MBR;<br />

31 GO TO JUMP;<br />

32 OP7: IF BIT(2,IR)= 1 THEN GO TO RETURN;<br />

33 IF BIT(1,IR)= 1 THEN GO TO MULDIV;<br />

34 ADDSUB: MAR=SP; SP= SP + (-1); MBR= MEMORY (MAR);<br />

35 IF BIT(0,IR)= 0 THEN GO TO SUM;<br />

36 MBR = COM(MBR) + 1; /* FOR SUBSTRACTION ONLY */<br />

37 SUM: MAR = SP; A = MBR; MBR = MEMORY(MAR);<br />

38 MBR = A + MBR; MEMORY(MAR) = MBR;<br />

39 GO TO MAINLOOP;

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 9<br />

Multiplikationsalgorithmus (Shift & Add)<br />

(4) => C MBR A D<br />

0100 * 1011 | |<br />

0000 => 0000 0000<br />

0100 +<br />

0100 => 0010 0000<br />

0100 +<br />

0110 => 0011 0000<br />

0000 +<br />

0011 => 0001 1000<br />

0100 +<br />

0101 => 0010 1100 (2 * 16 + 12)10 = 4410 !<br />

Divisionsalgorithmus (Subtract & Shift)<br />

Duale Division: 0110 : 0011 = 0010<br />

A: 0000 Startwert<br />

- 1101 über Add. ZK 0011<br />

= 1101 Erg. neg., A rückgängig, Quotientstelle in D = 0<br />

A: 0001 hole nächste Stelle v. Dividenden<br />

1101 subtrahiere<br />

1110 Erg. neg., A rückgängig, Quotientstelle in D = 0<br />

A: 0011 hole nächste Stelle v. Dividenden<br />

1101 subtrahiere<br />

10000 Erg. pos., Wert in A halten, Quotientstelle in D = 1<br />

A: 0000 nächste Stelle<br />

1101 subtrahiere<br />

1101 Erg. neg., A rückgängig, Quotientstelle in D = 0<br />

=> Quotient von oben ablesen (D Reg.): 0010

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 10<br />

Vorgehen bei der Umsetzung RA zum DEA:<br />

1. Schritt: Aufzeichnen des NEA mit ε Übergängen mit den<br />

Standardkonstrukten.<br />

2. Schritt: Überführung der NEA- in eine DEA-Automatentafel<br />

Hierzu gibt es einige Regeln zu beachten:<br />

2.1 Aufstellen der wichtigen Zustände; wichtig sind alle Zustände,<br />

die durch Auftreten eines Zeichens ungleich ε angelaufen werden<br />

und der Startzustand.<br />

2.2 Zusammenfassen der mit ε nach vorn verbundenen, wichtigen<br />

Zustände zu einem Zustand.<br />

2.3 Aufstellen der Tabelle (Automatentafel) mit allen wichtigen Zuständen.<br />

2.4 Sukzessive Weiterentwicklung der Tabelle. Es können sich weitere<br />

Zustandskombinationen als Zusammenfassung zu einem neuen<br />

Zustand ergeben. Diese sind in die Tabelle aufzunehmen bis<br />

keine neuen Kombinationen mehr entstehen.<br />

Beim NEA können Zustände „absterben“ (Nachfolger durch „-“<br />

gekennzeichnet). Diese sind in Zustandskombinationen bei den<br />

Nachfolgern zu vernachlässigen.<br />

2.5 In der vollständig aufgestellten Tabelle können zunächst alle Zustände<br />

gestrichen werden, die nicht allein als Folgezustände auftreten<br />

(Regel: nicht erreichbare Zustände können gestrichen werden).<br />

Auch dies kann ein sukzessiver Prozess sein, d.h. tritt einer<br />

nur allein als Folgezustand eines gestrichenen auf, so ist er ebenfalls<br />

zu streichen.<br />

2.6 Da beim NEA Zustände „absterben“ können (Nachfolger durch „-“<br />

gekennzeichnet), beim DEA aber nicht, gilt die Regel, dass ein<br />

„absorbierender“ Zustand nur entsteht, wenn „-“ isoliert als Folgezustand<br />

auftritt.<br />

3. Schritt: Minimierung des DEA

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 11<br />

LZW Kompressionsverfahren für binäre Daten<br />

verbleibende s K Verzeichnis Verz. Ausgabe<br />

Eingabe<br />

suchen folg. Z. = s K Nr. = Code(s)<br />

0 1<br />

1 2<br />

010101110010100101 0 1 01 3 1<br />

10101110010100101 1 0 10 4 2<br />

0101110010100101 0|1 0 010 5 3<br />

01110010100101 0|1 1 011 6 3<br />

110010100101 1 1 11 7 2<br />

10010100101 1|0 0 100 8 4<br />

010100101 0|1|0 1 0101 9 5<br />

100101 1|0|0 1 1001 10 8<br />

101 1|0 1 101 11 4<br />

1 1 ∼ 2<br />

1. Lese Eingabefolge und suche längste, eingetragene Folge s<br />

2. Setze K auf nächstfolgendes Zeichen<br />

3. Trage Folge sK als neu in das Verzeichnis ein<br />

4. Gebe Code(s) [Verzeichnisnummer] aus<br />

5. Gehe zu 1.<br />

Eingabe<br />

Code(K)<br />

LZW Dekompressionsverfahren für binäre Daten<br />

K s Verzeichnis<br />

= s-1 Kleft<br />

V. Nr. Ausgabe<br />

= K<br />

0 1<br />

∼ 1 2<br />

1 0| 0 0<br />

2 1| 1 01 3 0 1<br />

3 0|1 01 10 4 01 01<br />

3 0|1 01 010 5 0101 01<br />

2 1| 1 011 6 010101 1<br />

4 1|0 10 11 7 0101011 10<br />

5 0|10 010 100 8 010101110 010<br />

8 1|00 100 0101 9 010101110010 100<br />

4 1|0 10 1001 10 010101110010100 10<br />

2 1| ∼ 101 11 01010111001010010 1<br />

1. Suche K aus Eingabe Code(K) im Verzeichnis<br />

2. Trage (s-1 Kleft) als neu in das Verzeichnis ein<br />

3. Gebe Folge K aus<br />

4. Setze s = K<br />

5. Gehe zu 1.<br />

Man beachte, dass bei den Verzeichniseinträgen der neu „gelernte“ Eintrag mit dem<br />

gleichen Zeichen beginnt, mit dem der vorherige endet! Tritt bei Dekomprimierung<br />

eine Eingabe auf, die noch nicht eingetragen ist, kann dieser neue Eintrag nur der<br />

vorher gefundene, eingeleitet von dem letzten Zeichen der gefundenen Folge sein!

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 12<br />

Schaltungen <strong>zur</strong> Erzeugung von Codeworten eines Hammingcodes<br />

Codewort:<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

c6 c5 c4 c3 c2 c1 c0<br />

=1<br />

=1 =1 =1 =1 =1 =1<br />

=1 =1 =1 =1 =1 =1 =1<br />

=1 =1 =1 =1 =1 =1 =1<br />

=1<br />

Grundschaltung <strong>zur</strong> Gernerierung und Prüfung<br />

Den Schaltungen unten liegt<br />

⎛1110<br />

100⎞<br />

⎜ ⎟<br />

diese H-Matrix zugrunde H = ⎜1101<br />

010⎟<br />

⎜ ⎟<br />

⎝1011<br />

001⎠<br />

Nachricht Kontrollstellen<br />

codiert 1 0 1 0<br />

0 1 0<br />

codieren 1 0 1 0 0 0 0<br />

=1 =1 =1<br />

=1 =1 =1 =1<br />

=1 =1 =1 =1<br />

Generierungsschaltung nach obiger H-Matrix<br />

Nachricht Kontrollstellen<br />

codiert 1 0 1 0 0 1 0<br />

0<br />

0<br />

0<br />

=1<br />

=1 =1 =1<br />

=1 =1 =1 =1<br />

=1 =1 =1 =1<br />

Prüfschaltung nach obiger H-Matrix<br />

0<br />

0<br />

0<br />

s2<br />

s1<br />

s0<br />

S<br />

y<br />

n<br />

d<br />

r<br />

o<br />

m<br />

S<br />

y<br />

n<br />

d<br />

r<br />

o<br />

m

Gerhard-Mercator Prof. Dr.-Ing. W. Geisselhardt Fak. 5<br />

Universität Duisburg IIMT, IT<br />

Hilfsblatt <strong>zur</strong> <strong>Übung</strong>: DATENVERARBEITUNG 1 SEITE: 13<br />

Schaltungen <strong>zur</strong> Erzeugung von Codeworten eines zyklischen Codes<br />

Multiplikator-<br />

polynom<br />

x<br />

Multiplikandenpolynom<br />

0 x 1 .... x n-1 x n<br />

1 + x 1 + x 4<br />

1<br />

1<br />

x 0<br />

0<br />

D Q<br />

1<br />

x 1 x 2<br />

0<br />

=1 D Q<br />

1<br />

0<br />

.........<br />

=1 D Q<br />

.........<br />

x k-1<br />

1<br />

0<br />

=1 D Q<br />

Grundschaltung <strong>zur</strong> Polynom-Multiplikation<br />

1 0 0<br />

1<br />

Beispielschaltung <strong>zur</strong> Polynom-Multiplikation<br />

1<br />

x k<br />

=1<br />

0<br />

Produkt<br />

polynom<br />

x 1 + x 2 + x 4<br />

D Q =1 D Q<br />

=1 D Q =1 D Q =1<br />

x 1 + x 3 + x 4 + x 6 + x 8<br />

0 1 1 0 1 0 1 0 1 1 0 1 0 1<br />

Divisor-<br />

polynom<br />

x 0 x 1 .... x n-1 x n<br />

Dividenden-<br />

polynom<br />

1 + x 1 + x 4<br />

1<br />

x 0 x 1<br />

=1<br />

0<br />

D Q<br />

1<br />

0<br />

=1 D Q<br />

x 0 x 1<br />

Grundschaltung <strong>zur</strong> Polynom-Division<br />

1 1 0<br />

0<br />

x 5 + x 6 + x 8<br />

=1<br />

D Q =1 D Q<br />

=1 D Q =1 D Q<br />

1 + x 2 + x 4<br />

0 0 0 0 0 1 1 0 1 1 0 1 0 1<br />

x 0 x 1<br />

x 2<br />

x 3<br />

1 1 1 1<br />

Beispielschaltung <strong>zur</strong> Polynom-Division<br />

1<br />

x 2<br />

0<br />

.........<br />

=1 D Q<br />

x 2<br />

R e s t p o l y n o m<br />

.........<br />

x k-1<br />

1<br />

0<br />

1<br />

=1 D Q<br />

x k-1<br />

x k<br />

1<br />

0<br />

Quotienten<br />

polynom