10. Programmierbare Logikbausteine - Fachgebiet Rechnersysteme ...

10. Programmierbare Logikbausteine - Fachgebiet Rechnersysteme ...

10. Programmierbare Logikbausteine - Fachgebiet Rechnersysteme ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

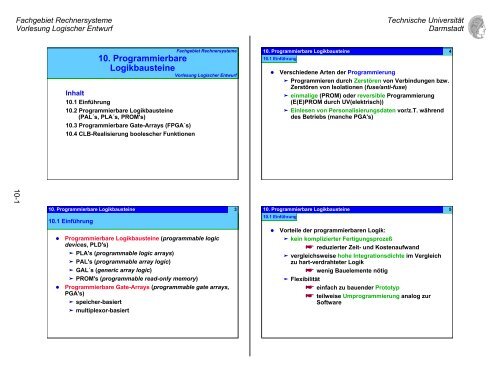

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong> <strong>Programmierbare</strong><br />

<strong>Logikbausteine</strong><br />

Inhalt<br />

<strong>10.</strong>1 Einführung<br />

<strong>10.</strong>2 <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

(PAL´s, PLA´s, PROM's)<br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays (FPGA´s)<br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong>1<br />

Vorlesung Logischer Entwurf<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>1 Einführung<br />

• Verschiedene Arten der Programmierung<br />

Programmieren durch Zerstören von Verbindungen bzw.<br />

Zerstören von Isolationen (fuse/anti-fuse)<br />

einmalige (PROM) oder reversible Programmierung<br />

(E(E)PROM durch UV(elektrisch))<br />

Einlesen von Personalisierungsdaten vor/z.T. während<br />

des Betriebs (manche PGA's)<br />

4<br />

10-1<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>1 Einführung<br />

• <strong>Programmierbare</strong> <strong>Logikbausteine</strong> (programmable logic<br />

devices, PLD's)<br />

PLA's (programmable logic arrays)<br />

PAL's (programmable array logic)<br />

GAL´s (generic array logic)<br />

PROM's (programmable read-only memory)<br />

• <strong>Programmierbare</strong> Gate-Arrays (programmable gate arrays,<br />

PGA's)<br />

speicher-basiert<br />

multiplexor-basiert<br />

3<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>1 Einführung<br />

• Vorteile der programmierbaren Logik:<br />

kein komplizierter Fertigungsprozeß<br />

reduzierter Zeit- und Kostenaufwand<br />

vergleichsweise hohe Integrationsdichte im Vergleich<br />

zu hart-verdrahteter Logik<br />

wenig Bauelemente nötig<br />

Flexibilität<br />

einfach zu bauender Prototyp<br />

teilweise Umprogrammierung analog zur<br />

Software<br />

5

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

6<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

8<br />

• Prinzipaufbau eines PLA´s (programmable logic array)<br />

durch Programmieren kann ein PLA personalisiert<br />

werden<br />

Eingangsvariable<br />

a b c<br />

...<br />

Array von<br />

Und-Gattern<br />

...<br />

Array von<br />

Oder-Gattern<br />

&<br />

&<br />

&<br />

abc<br />

ab<br />

bc<br />

f = abc + 1<br />

ab + ac<br />

f 2<br />

= b c + ac + ac<br />

= b c + a<br />

Produktterme<br />

...<br />

Ausgangsfunktionen<br />

&<br />

&<br />

≥ 1 ≥ 1 ≥ 1 ≥ 1<br />

ac<br />

ac<br />

f = 3<br />

ab + bc<br />

f 4<br />

= abc + ab + ac<br />

f 1<br />

f 2<br />

f 3<br />

f 4<br />

10-2<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

7<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

9<br />

&<br />

&<br />

&<br />

PLA-Schema vor der Programmierung<br />

Array von<br />

Oder-Gattern<br />

• Personalisierung von PLA's<br />

die zweistufige Minimierung von Funktionsbündeln<br />

ist die angemessene Optimierungsmethode<br />

die Restriktionen durch die Größe der Und-Ebene<br />

(maximale Gesamtzahl der Primimplikanten) sowie<br />

der Oder-Ebene (Anzahl der realisierbaren<br />

Funktionen) müssen berücksichtigt werden<br />

&<br />

&<br />

Array von<br />

Und-Gattern<br />

≥ 1 ≥ 1 ≥ 1 ≥ 1

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

10<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

12<br />

• Oft wird folgende einfachere Darstellung benutzt:<br />

• Auf den folgenden Folien ein Beispiel für die Realisierung<br />

eines PLA's:<br />

&<br />

&<br />

&<br />

&<br />

&<br />

≥ 1<br />

≥ 1 ≥ 1 ≥ 1<br />

10-3<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

11<br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

die Personalisierung wird durch Ankreuzen symbolisiert:<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

13<br />

6.2 PLA's, PAL's, PROM's<br />

Eingangs-/Ausgangstreiber, zugleich Inverter:<br />

a b c<br />

a b c<br />

X<br />

&<br />

XX X X<br />

X X &<br />

X X X<br />

X &<br />

X X X<br />

&<br />

X X X X<br />

X X<br />

& X<br />

X<br />

abc<br />

ab<br />

bc<br />

ac<br />

ac<br />

f = abc + 1<br />

ab + ac<br />

f 2<br />

= b c + ac + ac<br />

= b c + a<br />

f = 3<br />

ab + bc<br />

f 4<br />

= abc + ab + ac<br />

≥ 1<br />

≥ 1 ≥ 1 ≥ 1<br />

f 1<br />

f 2<br />

f 3<br />

f 4

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.2 PLA's, PAL's, PROM's<br />

pMOS-Transistoren<br />

für Pseudo-nMOS a<br />

~Widerständen<br />

b<br />

nMOS-Transistor<br />

c<br />

14<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.2 PLA's, PAL's, PROM's<br />

NOR/NOR-Realisierung<br />

a b c<br />

a + b + c = abc<br />

ab<br />

16<br />

10-4<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.2 PLA's, PAL's, PROM's<br />

NOR/NOR-Realisierung<br />

a b c<br />

NOR-Funktion:<br />

a + b + c = abc<br />

15<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.2 PLA's, PAL's, PROM's<br />

NOR/NOR-Realisierung<br />

a b c<br />

abc<br />

ab<br />

f 4<br />

= abc + ab<br />

17<br />

NOR mit Negation<br />

= Oder:<br />

f 4

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

18<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

20<br />

• Prinzipaufbau eines PAL´s (programmable array logic)<br />

Eingangsvariable<br />

fest<br />

...<br />

Array von<br />

Und-Gattern<br />

...<br />

Array von<br />

Oder-Gattern<br />

programmierbar<br />

Produktterme<br />

...<br />

Ausgangsfunktionen<br />

Quelle:<br />

10-5<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.2 PLA's, PAL's, PROM's<br />

19<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

21<br />

Beispiel "kleines" PAL<br />

— 10 Eingangsvariable,<br />

8 Ausgänge,<br />

je zwei Produktterme<br />

x 1<br />

x 2 ... x 10<br />

...<br />

&<br />

&<br />

...<br />

&<br />

...<br />

Beispiel "mittleres" PAL TIBPAL20R8:<br />

— je acht Produktterme in 20 Variablen, davon 12<br />

Eingänge, 8 rückgekoppelte interne Speicherelemente<br />

(Flipflops)<br />

— weitere Funktionsvielfalt z.B. durch Flipflops an den<br />

Ausgängen, Rückkopplung der Ausgänge auf die<br />

Eingänge, Ausgänge, die auch als<br />

Eingänge benutzt werden können,<br />

usw.<br />

&<br />

...<br />

≥ 1 ≥ 1<br />

o 1 o 8

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

22<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

24<br />

• PAL Personalisierung:<br />

Optimierung geschieht durch zweistufige Minimierung<br />

der Einzelfunktionen<br />

die Restriktionen bzgl. Anzahl der Primimplikanten pro<br />

Funktion und Anzahl der realisierbaren Funktionen<br />

müssen berücksichtigt werden<br />

Quelle:<br />

10-6<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

23<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.2 PLA's, PAL's, PROM's<br />

25<br />

Schematische Darstellung:<br />

...<br />

• Personalisieren durch Zerstören von Verbindungen<br />

"durchschmelzen" durch kurzfristig erhöhte<br />

Spannung<br />

8 Produktterme<br />

&<br />

...<br />

&<br />

≥ 1<br />

12 Eingänge<br />

Takt<br />

8 Flipflops

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.2 PLA's, PAL's, PROM's<br />

26<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

28<br />

Personalisierungsdaten adressieren die zu zerstörenden<br />

Verbindungen<br />

Adresse besteht aus<br />

Zeilen- und Spaltenadresse<br />

x 1<br />

x 2 ... x 10<br />

Anlegen der Adresse<br />

&<br />

&<br />

über Pins des Bausteins<br />

...<br />

...<br />

...<br />

• GAL‘s (Generic Array Logic)<br />

Handelsmarke von Lattice<br />

~ PAL‘s, aber die OLMC‘s<br />

(Output Logic Macro<br />

Cells) sind konfigurierbar:<br />

&<br />

Zeilenadresse<br />

&<br />

...<br />

≥ 1 ≥ 1<br />

Spaltenadresse<br />

o 1 o 8<br />

10-7<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

27<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

29<br />

Anlegen von kurzfristig (z.B. 10µs) erhöhten<br />

Spannungsimpulsen (z.B. 10,75V statt 5V)<br />

Modi<br />

— Registered<br />

10µs<br />

10V<br />

5V<br />

0<br />

Vielfalt an Varianten, z.B. Programmieren des bereits<br />

plazierten Bausteins über Anschlüsse, die für das<br />

Testen benutzt werden

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

30<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

32<br />

Registered (Forts.):<br />

Simple (Forts.):<br />

10-8<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

31<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

33<br />

Modi<br />

— Simple<br />

• PROM (programmable read-only memory):<br />

Eingangsvariable<br />

programmierbar<br />

...<br />

Array von<br />

Und-Gattern<br />

...<br />

Array von<br />

Oder-Gattern<br />

Adressen<br />

fest, komplette<br />

Dekodierung aller<br />

Eingangskombinationen<br />

(=Adressen)<br />

...<br />

Ausgangsfunktionen

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

34<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

36<br />

Realisierung von m Funktionen in n Variablen<br />

entspricht der Umsetzung einer Funktionstabelle<br />

n Eingangsvariable<br />

...<br />

Array von<br />

Und-Gattern<br />

...<br />

Array von<br />

Oder-Gattern<br />

programmierbar<br />

Wortbreite m<br />

2 n ...<br />

Adressen<br />

fest, komplette<br />

Dekodierung aller<br />

m Ausgangsfunktionen<br />

Eingangskombinationen<br />

(=Adressen)<br />

ROM's: die Information im Speicher wird bei der<br />

Herstellung (Layout) festgelegt<br />

PROM's: Personalisierung durch den Anwender<br />

bei ROM's/PROM's ist die Optimierung offensichtlich<br />

unsinnig<br />

die Restriktionen durch die Anzahl der Variablen und<br />

durch die Wortbreite = Anzahl der realisierbaren<br />

Funktionen müssen berücksichtigt werden<br />

10-9<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

35<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

37<br />

simples Beispiel:<br />

a b c<br />

Dekodierer<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

1 0 1 0<br />

0 0 1 1<br />

0 1 0 1<br />

0 1 1 0<br />

0 0 0 1<br />

0 0 1 0<br />

0 0 0 0<br />

0 1 1 1<br />

f 1 f 2 f 3 f 4<br />

ROM-Inhalt =<br />

Funktionswerte<br />

4-bit Wort unter<br />

Adresse 110<br />

4 Ausgangsfunktionen<br />

in drei Variablen<br />

• EPROM´s, EEPROM's (electrically erasable<br />

programmable read-only memory):<br />

reversibel programmierbare Logik durch Löschen<br />

der gespeicherten Information über UV-Licht bzw.<br />

elektrisch<br />

Prinzip:<br />

— MOS-Transistor mit sog. "floating gate"<br />

— im Programmierbetrieb wird durch Anlegen einer<br />

Spannung > Betriebsspannung eine Ladung<br />

(5.000 < bzw. < 30.000 Elektronen !) auf das<br />

floating gate gebracht<br />

— diese Ladung hebt die Schwellspannung des<br />

Transistors so an, daß Änderungen am Gate bei<br />

normaler Betriebsspannung keine Auswirkungen<br />

haben und der Transistor dauernd gesperrt ist

DIN<br />

F'<br />

G'<br />

H'<br />

G'<br />

H'<br />

DIN<br />

F'<br />

G'<br />

H'<br />

H'<br />

F'<br />

1<br />

1<br />

S/R<br />

Control<br />

S/R<br />

Control<br />

SD<br />

D Q<br />

EC<br />

RD<br />

SD<br />

D Q<br />

EC<br />

RD<br />

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

38<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

40<br />

• EEPROM's/Flash sind<br />

ideal für field upgrades (Bootsoftware, BIOS, MP3, Handy<br />

Firmware) und zum Speichern individueller Kenndaten<br />

(IP Adresse)<br />

unsicher gegenüber Manipulationen<br />

• Flash-Speicher kommt praktisch in jedem PC, PDA, Handy<br />

vor, z.B. "digitaler Film" in der Digitalkamera bzw. "digitales<br />

Band" im MP3-Spieler<br />

Schreiben per Bit/Byte/Block<br />

Löschen per Block (8kBits - 1 MBit)<br />

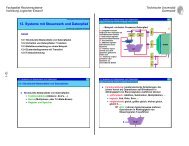

• Speicher-basierte PGA's (Xilinx)<br />

G4<br />

G3<br />

G2<br />

G1<br />

F4<br />

F3<br />

F2<br />

F1<br />

K<br />

CLB<br />

CLB<br />

Switch<br />

Ma trix<br />

CLB<br />

CLB<br />

Programmable<br />

Interconnect<br />

G<br />

Func.<br />

Gen.<br />

F<br />

Func.<br />

Gen.<br />

H<br />

Func.<br />

Gen.<br />

C1 C2 C3<br />

C4<br />

H1 DIN S/R EC<br />

Y<br />

X<br />

Configurable<br />

Logic Blocks (CLBs)<br />

Vcc<br />

Slew Passive<br />

Rate Pull-Up,<br />

Control Pull-Down<br />

D Q<br />

Output<br />

Buffer<br />

Input<br />

Buffer<br />

Q D<br />

Delay<br />

I/O Blocks (IOBs)<br />

Pad<br />

Quelle: Xilinx<br />

10-10<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

39<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

41<br />

Programmable Interconnect Points, PIPs (White)<br />

• <strong>Programmierbare</strong> Gate-Arrays (PGA's) bestehen aus<br />

einer Matrix personalisierbarer universeller<br />

<strong>Logikbausteine</strong> und<br />

personalisierbaren Verbindungen zwischen diesen<br />

Bausteine<br />

Switch<br />

Matrix<br />

Direct<br />

Interconnect<br />

(Green)<br />

Routed Wires (Blue)<br />

Quelle: Xilinx<br />

CLB<br />

(Red)<br />

Long Lines<br />

(Purple)

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

43<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

45<br />

• Beispiel Xilinx Spartan-3 Serie<br />

— jeder CLB kann<br />

- jede boolesche Funktion in fünf<br />

- bzw. zwei beliebige Funktionen in vier<br />

Variablen realisieren<br />

CLB's werden durch Laden von Flipflops mit<br />

Steuerungsinformation personalisiert. Prinzip:<br />

FF FF FF FF FF FF FF FF<br />

a<br />

b<br />

c<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

f<br />

10-11<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

44<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

46<br />

• CLB´s (configurable logic blocks):<br />

universelle Funktionsblöcke plus (u.a.) Speicherelemente<br />

— Beispiel: Xilinx XC4000 CLB (vereinfacht)<br />

H<br />

DIN<br />

• <strong>Programmierbare</strong> Verbindungen (Prinzip)<br />

Switch-<br />

Matrix<br />

Grundzellenanbindung<br />

Switch-<br />

Matrix<br />

A1<br />

A2<br />

A3<br />

A4<br />

B1<br />

B2<br />

B3<br />

B4<br />

Univ.<br />

Funkt.<br />

Block<br />

Univ.<br />

Funkt.<br />

Block<br />

Univ.<br />

Funkt.<br />

Block<br />

><br />

><br />

Switch-<br />

Matrix<br />

Grundzelle<br />

Grundzellenanbindung<br />

Grundzellenanbindung<br />

Grundzellenanbindung<br />

Switch-<br />

Matrix

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

47<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

49<br />

Aufbau der Switch-Matrix<br />

FF<br />

FF<br />

Verzweigungen:<br />

FF<br />

FF<br />

FF<br />

FF<br />

Grundzelle<br />

FF<br />

Grundzelle<br />

FF<br />

FF<br />

FF<br />

FF<br />

FF<br />

10-12<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

48<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

50<br />

gleichzeitige Verbindungen:<br />

FF<br />

FF<br />

Anbindung der Grundzelle:<br />

FF<br />

Switchmatrix<br />

FF<br />

FF<br />

Grundzelle<br />

FF<br />

Grundzelle<br />

FF<br />

FF<br />

Switchmatrix

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

51<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

53<br />

Switchmatrix<br />

andere Möglichkeiten:<br />

FF FF<br />

FF<br />

FF<br />

• Multiplexor-basierte PGA's<br />

— Beispiel Actel A1280, insgeamt 1232<br />

kombinatorische Grundzellen der folgenden Art:<br />

Grundzelle<br />

FF<br />

FF<br />

0 1<br />

≥ 1<br />

A1<br />

B1<br />

Switchmatrix<br />

FF<br />

FF<br />

FF<br />

FF<br />

0 1<br />

0 1<br />

I00 I01 I10 I11<br />

&<br />

A0<br />

B0<br />

10-13<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

52<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

54<br />

• Die Personalisierung erfolgt durch Laden der<br />

Steuerflipflops<br />

da die Steuerungsinformation flüchtig ist, muß diese<br />

z.B. aus einem EPROM beim Einschalten geladen<br />

werden<br />

eine Umprogrammierung ist während es Betriebs<br />

möglich<br />

• Eine zweistufige Minimierung ist offenbar unsinnig, da<br />

es nicht auf die Anzahl der Primimplikanten ankommt,<br />

sondern nur auf die Anzahl der Variablen, von denen<br />

eine Funktion abhängt<br />

die Verbindungen zwischen Grundzellen und die<br />

Programmierung der Grundzellen sind irreversibel<br />

(anti-fuse)<br />

naheliegende Realisierung von OBDD's

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

• Wie kann eine beliebige boolesche Funktion in k<br />

Variablen auf ein Netzwerk z.B. von CLB's in n Variablen<br />

abgebildet werden?<br />

• Wie kann eine boolesche Funktion überhaupt in<br />

Teilfunktionen zerlegt werden?<br />

55<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

• Bei gegebenem Gatternetz ist die Abbildung auf CLB's in<br />

n Variablen möglich durch eine Partitionierung in<br />

Teilnetze mit weniger als oder gleich n Eingängen.<br />

Beispiel CLB's in drei Variablen:<br />

a<br />

d<br />

&<br />

57<br />

b<br />

d<br />

a<br />

1<br />

1<br />

1<br />

b<br />

&<br />

& 1<br />

c<br />

&<br />

&<br />

1<br />

&<br />

a<br />

b<br />

d<br />

a<br />

b<br />

c<br />

CLB CLB<br />

CLB<br />

10-14<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

56<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

58<br />

• Bilden von Teilnetzen mit einem Ausgang und n<br />

verschiedenen Eingängen<br />

die Funktion des Teilnetzes ist eine Funktion in n<br />

Variablen realisierbar durch einen CLB in n Variablen<br />

&<br />

≥1<br />

≥1<br />

≥1<br />

≥1<br />

&<br />

≥1<br />

durch CLB in<br />

3 Variablen<br />

realisierbar<br />

b<br />

d<br />

a<br />

b<br />

d<br />

a<br />

1<br />

a<br />

d<br />

1<br />

1<br />

1<br />

b<br />

a<br />

d<br />

1<br />

1<br />

b<br />

&<br />

&<br />

& 1<br />

c<br />

&<br />

&<br />

& 1<br />

&<br />

&<br />

c<br />

&<br />

1<br />

1<br />

&<br />

&<br />

&<br />

a<br />

b<br />

d<br />

a<br />

b<br />

c<br />

a<br />

b<br />

d<br />

a<br />

b<br />

CLB CLB<br />

CLB CLB<br />

c<br />

CLB<br />

CLB

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

59<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

61<br />

• Gibt es keine Gatterrealisierung, kann der OBDD benutzt<br />

werden, der einem Netz aus 2:1-Multiplexoren entspricht<br />

— gesucht ist eine Realisierung mit CLB's in vier Variablen<br />

— Fiktion: der OBDD entspricht einer Multiplexorschaltung<br />

a<br />

0<br />

1<br />

b<br />

0 1<br />

c<br />

0 1<br />

0 1<br />

0 1<br />

0 1<br />

0 c<br />

a<br />

b<br />

f<br />

e<br />

1<br />

d<br />

f<br />

c<br />

e<br />

b<br />

d<br />

a<br />

c<br />

b<br />

CLB<br />

10-15<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

6.4 CLB-Realisierung boolescher Funktionen<br />

60<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

62<br />

— Beispiel: ein Verknüpfungsnetz mit Ausgang r soll<br />

überprüfen, ob von den 6 Eingängen a, ..., f<br />

jeweils genau einer den Wert 1 hat<br />

(1-aus-n Funktion in 6 Variablen)<br />

r = abcdef + abcdef + abcdef +<br />

abcdef + abcdef + abcdef<br />

Konvention:<br />

1-Pfeile nach rechts,<br />

0-Pfeile nach links<br />

Pfeile nach 0 weggelassen<br />

x<br />

0 1<br />

f<br />

e<br />

1<br />

d<br />

f<br />

c<br />

e<br />

b<br />

d<br />

a<br />

c<br />

b<br />

— gesucht ist eine Realisierung mit CLB's in vier Variablen<br />

— Fiktion: der OBDD entspricht einer Multiplexorschaltung<br />

f<br />

e<br />

1<br />

d<br />

f<br />

c<br />

e<br />

b<br />

d<br />

a<br />

b 0 1 b<br />

0 1<br />

0 1<br />

c<br />

b<br />

c 0 1 c<br />

d 0 1 d<br />

0 1<br />

0 1<br />

e 0 1 e<br />

f 0 1 f<br />

0 1<br />

0 0<br />

a<br />

0<br />

0 1<br />

0<br />

0<br />

0<br />

CLB

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

63<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

65<br />

— die Multiplexorschaltung wird so geschnitten, daß<br />

Funktionen in nur vier Variablen übrig bleiben<br />

— die Multiplexorschaltung wird so geschnitten, daß<br />

Funktionen in nur vier Variablen übrig bleiben<br />

f<br />

e<br />

1<br />

d<br />

f<br />

c<br />

0 1<br />

e<br />

b<br />

b 0 1 0 1 b<br />

<br />

c 0 1 c 0<br />

0 1<br />

d<br />

a<br />

c<br />

d 0 1 d<br />

e 0 1 e<br />

0 1<br />

0 1<br />

f 0 1 f<br />

0 0<br />

a<br />

0<br />

0 1<br />

0<br />

b<br />

0<br />

f<br />

e<br />

1<br />

a<br />

b<br />

a<br />

0 1<br />

b 0 1 0 1 b<br />

<br />

0<br />

c<br />

d<br />

f<br />

b<br />

0 1 0 1 c<br />

d 0 1 d<br />

0 1<br />

e<br />

d<br />

e 0 1 e<br />

0 1<br />

f 0 1 f<br />

0 1<br />

0 1 f<br />

0 0<br />

0 1 e<br />

0 1 d<br />

0<br />

0<br />

0<br />

10-16<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

64<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

66<br />

— die Multiplexorschaltung wird so geschnitten, daß<br />

Funktionen in nur vier Variablen übrig bleiben<br />

— die Multiplexorschaltung wird so geschnitten, daß<br />

Funktionen in nur vier Variablen übrig bleiben<br />

<br />

a<br />

b<br />

a<br />

0 1<br />

b 0 1 0 1 b<br />

0<br />

b<br />

<br />

a<br />

b<br />

0 1<br />

a<br />

0 1<br />

b 0 1 b<br />

b<br />

0<br />

c 0 1 0 1 c<br />

c<br />

0 1<br />

0 1 c<br />

d 0 1 0 1 d<br />

e 0 1 0 1 e 0<br />

f 0 1 0 1 f 0<br />

0 0<br />

f<br />

e<br />

1<br />

d<br />

f<br />

e<br />

d<br />

0<br />

f<br />

d 0 1 d<br />

e<br />

0 1<br />

1<br />

d<br />

0 1<br />

f<br />

e<br />

d<br />

e 0 1 e<br />

f 0 1 f<br />

0 1<br />

0 0<br />

0<br />

0<br />

1<br />

f<br />

e<br />

0 1 f<br />

d<br />

0 1 e<br />

0<br />

0 1 d<br />

0<br />

0<br />

0

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

67<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

69<br />

r = a b t + abt + a b s,<br />

s = c d ef + cdef + c d ef + c d ef,<br />

t = c d ef<br />

s<br />

c<br />

d<br />

e e<br />

f f<br />

1<br />

b<br />

d<br />

a<br />

t<br />

c<br />

b<br />

s<br />

b<br />

1<br />

a<br />

t<br />

b<br />

das Verfahren findet nicht immer die global optimale<br />

Lösung<br />

— Beispiel für CLB's in drei Variablen:<br />

1<br />

b<br />

d<br />

a<br />

c<br />

1<br />

3<br />

b<br />

d<br />

3 CLB's<br />

2<br />

b<br />

d<br />

1<br />

2<br />

a<br />

c<br />

1<br />

b<br />

d<br />

2 CLB's<br />

10-17<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>4 CLB-Realisierung boolescher Funktionen<br />

68<br />

• Verfahren:<br />

Partitionierung z.B. beginnend bei der Wurzel<br />

Zusammenfassungen mit soviel Variablen, wie lokal<br />

möglich ("Greedy-Algorithmus")<br />

f<br />

e<br />

1<br />

d<br />

f<br />

1<br />

c<br />

e<br />

b<br />

d<br />

2<br />

a<br />

c<br />

b<br />

3