10. Programmierbare Logikbausteine - Fachgebiet Rechnersysteme ...

10. Programmierbare Logikbausteine - Fachgebiet Rechnersysteme ...

10. Programmierbare Logikbausteine - Fachgebiet Rechnersysteme ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

DIN<br />

F'<br />

G'<br />

H'<br />

G'<br />

H'<br />

DIN<br />

F'<br />

G'<br />

H'<br />

H'<br />

F'<br />

1<br />

1<br />

S/R<br />

Control<br />

S/R<br />

Control<br />

SD<br />

D Q<br />

EC<br />

RD<br />

SD<br />

D Q<br />

EC<br />

RD<br />

<strong>Fachgebiet</strong> <strong>Rechnersysteme</strong><br />

Vorlesung Logischer Entwurf<br />

Technische Universität<br />

Darmstadt<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>2 PLA's, PAL's, PROM's<br />

38<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

40<br />

• EEPROM's/Flash sind<br />

ideal für field upgrades (Bootsoftware, BIOS, MP3, Handy<br />

Firmware) und zum Speichern individueller Kenndaten<br />

(IP Adresse)<br />

unsicher gegenüber Manipulationen<br />

• Flash-Speicher kommt praktisch in jedem PC, PDA, Handy<br />

vor, z.B. "digitaler Film" in der Digitalkamera bzw. "digitales<br />

Band" im MP3-Spieler<br />

Schreiben per Bit/Byte/Block<br />

Löschen per Block (8kBits - 1 MBit)<br />

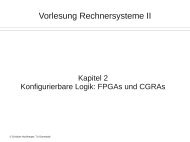

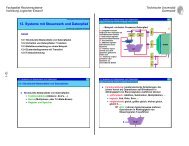

• Speicher-basierte PGA's (Xilinx)<br />

G4<br />

G3<br />

G2<br />

G1<br />

F4<br />

F3<br />

F2<br />

F1<br />

K<br />

CLB<br />

CLB<br />

Switch<br />

Ma trix<br />

CLB<br />

CLB<br />

Programmable<br />

Interconnect<br />

G<br />

Func.<br />

Gen.<br />

F<br />

Func.<br />

Gen.<br />

H<br />

Func.<br />

Gen.<br />

C1 C2 C3<br />

C4<br />

H1 DIN S/R EC<br />

Y<br />

X<br />

Configurable<br />

Logic Blocks (CLBs)<br />

Vcc<br />

Slew Passive<br />

Rate Pull-Up,<br />

Control Pull-Down<br />

D Q<br />

Output<br />

Buffer<br />

Input<br />

Buffer<br />

Q D<br />

Delay<br />

I/O Blocks (IOBs)<br />

Pad<br />

Quelle: Xilinx<br />

10-10<br />

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

39<br />

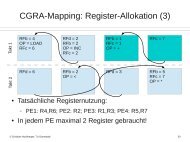

<strong>10.</strong> <strong>Programmierbare</strong> <strong>Logikbausteine</strong><br />

<strong>10.</strong>3 <strong>Programmierbare</strong> Gate-Arrays<br />

41<br />

Programmable Interconnect Points, PIPs (White)<br />

• <strong>Programmierbare</strong> Gate-Arrays (PGA's) bestehen aus<br />

einer Matrix personalisierbarer universeller<br />

<strong>Logikbausteine</strong> und<br />

personalisierbaren Verbindungen zwischen diesen<br />

Bausteine<br />

Switch<br />

Matrix<br />

Direct<br />

Interconnect<br />

(Green)<br />

Routed Wires (Blue)<br />

Quelle: Xilinx<br />

CLB<br />

(Red)<br />

Long Lines<br />

(Purple)