3. Die Code-Morphing-Software - TU Bergakademie Freiberg

3. Die Code-Morphing-Software - TU Bergakademie Freiberg

3. Die Code-Morphing-Software - TU Bergakademie Freiberg

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Der Transmeta Crusoe<br />

Prozessor<br />

Ausarbeitung zum Vortrag im Seminar: Projekte der Informatik WS 04/05<br />

an der <strong>TU</strong>-<strong>Bergakademie</strong> <strong>Freiberg</strong><br />

Dirk Bräuer<br />

Januar 2005<br />

1

Inhaltsverzeichnis<br />

1. Einleitung......................................................................................................................................... 6<br />

1.1 <strong>Die</strong> Firma Transmeta................................................................................................................. 6<br />

1.2 Der Crusoe Prozessor.................................................................................................................7<br />

2. Der Aufbau des Crusoe Prozessors.................................................................................................. 8<br />

<strong>3.</strong> <strong>Die</strong> <strong>Code</strong>-<strong>Morphing</strong>-<strong>Software</strong> (CMS)............................................................................................11<br />

<strong>3.</strong>1 Einleitung.................................................................................................................................11<br />

<strong>3.</strong>2 Befehlsverarbeitung................................................................................................................. 11<br />

<strong>3.</strong>3 Struktur.................................................................................................................................... 13<br />

4. Hardwareunterstütrzung für <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong>..................................................................16<br />

4.1 Ausnahmebehandlung..............................................................................................................16<br />

4.2 Alias Hardware........................................................................................................................ 16<br />

4.3 Selbstmodifizierender <strong>Code</strong>.....................................................................................................18<br />

4.<strong>3.</strong>1 Einleitung......................................................................................................................... 18<br />

4.<strong>3.</strong>2 Fine Grain Protection....................................................................................................... 18<br />

4.<strong>3.</strong>3 Self Revalidating Translations......................................................................................... 18<br />

4.<strong>3.</strong>4 Self Checking Translation................................................................................................19<br />

4.<strong>3.</strong>5 Stylized SMC................................................................................................................... 19<br />

4.<strong>3.</strong>6 Translation Groups...........................................................................................................20<br />

5. LongRun Power Management........................................................................................................ 21<br />

5.1 Einleitung.................................................................................................................................21<br />

5.2 LongRun Fähigkeiten...............................................................................................................22<br />

5.3 LongRun Funktionsweise........................................................................................................ 23<br />

5.4 Weitere LongRun Leistungen.................................................................................................. 23<br />

6. Zusammenfassung.......................................................................................................................... 25<br />

2

Abbildungsverzeichnis<br />

Abbildung 1: Firmensitz.......................................................................................................................6<br />

Abbildung 2: TM3120 & TM5400.......................................................................................................7<br />

Abbildung 3: Schichtenaufbau des Crusoe...........................................................................................8<br />

Abbildung 4: Temperatur TM5400...................................................................................................... 8<br />

Abbildung 5: Temperatur Pentium II................................................................................................... 8<br />

Abbildung 6: Hardwaredesign TM5400...............................................................................................9<br />

Abbildung 7: Hardwaredesign TM3120.............................................................................................10<br />

Abbildung 8: CMS - Startup...............................................................................................................11<br />

Abbildung 9: Molekülkombinationen................................................................................................ 12<br />

Abbildung 10: Pipelinestruktur.......................................................................................................... 12<br />

Abbildung 11: Befehlsverteilung verschiedener Architekturen......................................................... 13<br />

Abbildung 12: Flussdiagramm der CMS............................................................................................14<br />

Abbildung 13: Beispiel einer schrittweisen Übersetzung...................................................................15<br />

Abbildung 14: Beispiel Alias Hardware.............................................................................................17<br />

Abbildung 15: Ablauf Alias Hardware...............................................................................................17<br />

Abbildung 16: Falsches Aliasing........................................................................................................17<br />

Abbildung 17: Beispiel Stylized SMC............................................................................................... 19<br />

Abbildung 18: Lineares Power Management..................................................................................... 21<br />

Abbildung 19: LongRun Power Management....................................................................................22<br />

Abbildung 20: LongRun im Vergleich...............................................................................................22<br />

Abbildung 21: Integrierte Northbridge...............................................................................................24<br />

3

Tabellenverzeichnis<br />

Tabelle 1: Crusoe Prozessoren............................................................................................................. 7<br />

Tabelle 2: Compilerähnliche Optimierungen..................................................................................... 14<br />

Tabelle 3: Power Management Technologien.................................................................................... 21<br />

4

Abkürzungsverzeichnis<br />

ACPI Advanced Configuration and Power Interface<br />

ALU Arithmetic Logical Unit<br />

AMD Advanced Micro Devices<br />

APM Advanced Power Management<br />

BIOS Basic Input/Output System<br />

CMS <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong><br />

DDR-SDRAM Double Data Rate Synchronous Dynamic Random Access Memory<br />

DVD Digital Versatile Disc / Digital Video Disc<br />

FPU Floating Point Unit<br />

I/O Input/Output<br />

LTX LongRun Thermal Extension<br />

MMX Multi Media Extension<br />

PC Personal Computer<br />

PCI Peripheral Component Interconnect<br />

PLL Phase Lock Loop<br />

RISC Reduced Instruction Set Computing<br />

ROM Read-Only-Memory<br />

SMC Self Modifying <strong>Code</strong><br />

VIA Very Innovative Architecture<br />

VLIW Very Long Instruction Word<br />

5

1. Einleitung<br />

1.1 <strong>Die</strong> Firma Transmeta<br />

<strong>Die</strong> Firma Transmeta (Abbildung 1) wurde im Jahre 1995 in Santa Clara Kalifornien, einen Steinwurf von Intel entfernt,<br />

gegründet. Wesentliche Beteiligung an dieser Gründung hatten unter anderem David Ditzel, ein ehemaliger Mitarbeiter<br />

von Sun Microsystems, sowie Douglas Laird. Nicht zuletzt aus Werbegründen wurde Linus Torvalds 1997 ins Team<br />

aufgenommen. Jedoch verließ er nach fünf Jahren die Firma um sich der Weiterentwicklung des Linux Kernels zu<br />

widmen. [7], [10]<br />

Knapp fünf Jahre nach der Gründung brachte die Firma im Januar 2000 ihre erste Prozessorfamilie, die Crusoe<br />

Prozessoren, auf den Markt. Nur zwölf Monate später erfolgte der Börsengang. Nach einer weiteren Entwicklungszeit<br />

wurde im Oktober 2003 der Efficeon Prozessor als Nachfolger des Crusoes vorgestellt. [7]<br />

Mit seinen 296 Beschäftigten (Stand 2003) gilt Transmeta, im Vergleich zu den anderen Prozessorherstellern, als sehr<br />

kleine Firma. So musste auch die eigentliche Produktion der Prozessoren ausgelagert werden. IBM übernahm diese<br />

Aufgabe und fertig in seinen Werken Transmetas Produkte. [10]<br />

Im <strong>3.</strong> Quartal 2004 konnte die Firma einen Umsatz von 7 Mio. US$ verbuchen. <strong>Die</strong>s stellt ein Plus von 159% zum<br />

Vorjahr dar. Jedoch steht diesen Zahlen die Summe von 27.5 Mio US$ Verlust im gleichen Quartal gegenüber. <strong>Die</strong>se<br />

Zahlen lassen vermuten, dass das große Ziel, AMD beziehungsweise Intel Konkurrenz zu machen, bisher unerreichbar<br />

ist. Mit einem Marktanteil von 0.8% liegt Transmeta deutlich hinter den langjährigen Herstellern (AMD: 17.7%,<br />

Intel: 82.5%). Lediglich VIA mit 1% Marktanteil ist in Reichweite. [10]<br />

Große Hoffnung diese Zahlen weiter zu steigern macht der neue 90nm Efficeon Prozessor.<br />

Abbildung 1: Firmensitz<br />

6

1.2 Der Crusoe Prozessor<br />

<strong>Die</strong> Entwicklung des Crusoe Prozessors begann zeitgleich mit der Firmengründung. Über die gesamte Entwicklungszeit,<br />

wurden keine Informationen nach außen abgegeben. Es machte sich die Redewendung vom Mysterium Transmeta breit.<br />

<strong>Die</strong> einzigen Gerüchte die kursierten besagten etwas über die Entwicklung eines schnellen RISC-Prozessors.<br />

Am 19. Januar 2000 wurden schließlich zwei Prozessoren vorgestellt: Der TM3120 sowie der TM5400<br />

(Abbildung 2).<br />

Es handelt sich hierbei um VLIW-Prozessoren (Very Long Instruction Word), welche mit einer speziellen <strong>Code</strong>-<br />

<strong>Morphing</strong> <strong>Software</strong> (CMS) ausgestattet sind. Eine weitere Besonderheit stellt der Verbrauch von lediglich 1W unter<br />

Volllast dar. Im Vergleich verbraucht ein Mobile PIII 10W. Um einen weiteren Vorsprung im mobilen Sektor zu<br />

erreichen wurde im TM5400 zusätzlich eine neue Art von Power-Management, das LongRun Power-Management,<br />

implementiert. <strong>Die</strong>ses ermöglicht eine automatische <strong>Software</strong>regelung von Takt und Spannung.<br />

<strong>Die</strong> beiden Prozessoren kosteten mit 65$ (TM3120) beziehungsweise 119$ (TM5400) nur einen Bruchteil der anderen<br />

auf dem Markt vertretenen. [7]<br />

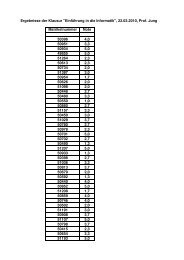

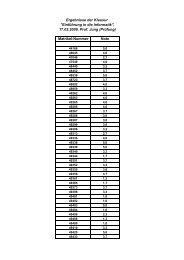

In der folgenden Tabelle 1 sollen die einzelnen Crusoe Prozessoren kurz mit den wichtigsten Daten genannt werden.<br />

[11]<br />

Bezeichnung Erschienen Takt L1-Cache L2-Cache<br />

TM3120 9. Jan 2000 333,366,400 MHz 96 KB -<br />

TM5400 9. Jan 2000 500-700 MHz 128 KB 256 KB<br />

TM5600 7. Okt 2000 300-600 MHz 128 KB 256 KB<br />

TM5500 25. Jun 2001 300-800 MHz 128 KB 256 KB<br />

TM5800 25. Jun 2001 300-1000 MHz 128 KB 512 KB<br />

TM5700 5. Jan 2004 667 MHz 128 KB 256 KB<br />

TM5900 5. Jan 2004 800-1000 MHz 128 KB 512 KB<br />

Tabelle 1: Crusoe Prozessoren<br />

Abbildung 2: TM3120 & TM5400<br />

7

2. Der Aufbau des Crusoe Prozessors<br />

Der Crusoe Prozessor ist ein sogenannter Hybrid Prozessor. Dass bedeutet, er ist zum Teil in Hard- und zum Teil in<br />

<strong>Software</strong> implementiert. Beim Crusoe ist die Aufteilung circa ¼ Hardware und ¾ <strong>Software</strong>.<br />

Zum Hardwareteil gehört allein der VLIW-Kern mit seinen Schnittstellen. <strong>Die</strong> <strong>Software</strong> unterteilt sich in die <strong>Code</strong><br />

<strong>Morphing</strong> <strong>Software</strong> und dem streng mit ihr verbundenen LongRun Power Management.<br />

<strong>Die</strong> Vorteile dieser Architektur liegen auf der Hand. Durch die Verwendung von <strong>Software</strong> werden Transistoren<br />

eingespart. <strong>Die</strong>s ermöglicht wiederum eine Einsparung von Strom und somit können Akkus von Notebooks längere<br />

Laufzeiten bieten. Ebenso ist die Wärmeabgabe verringert, was die Verwendung von passiven und somit leisen<br />

Kühlsystemen gestattet. [1], [4], [7]<br />

Abbildung 3 zeigt den angesprochenen Aufbau des Prozessors.<br />

Abbildung 3: Schichtenaufbau des Crusoe<br />

<strong>Die</strong> Abbildungen 4 und 5 zeigen die unterschiedliche Wärmeabgabe eines TM5400 und eines Pentium III, bei der DVD<br />

Wiedergabe. <strong>Die</strong> Werte sprechen deutlich für Transmeta. Jedoch bleiben die genauen Bedingungen für diesen Test<br />

verborgen. Ebenso wäre der Mobile PIII sicherlich ein besserer Konkurrent gewesen. [1]<br />

Abbildung 4: Temperatur TM5400 Abbildung 5: Temperatur Pentium II<br />

8

Abbildung 6 zeigt das Hardwaredesign des TM5400, welches im folgenden Abschnitt näher erläutert werden soll.<br />

Der Prozessor besitzt fünf Funktionseinheiten: zwei ALUs für Operationen mit ganzen Zahlen, eine FPU/Multimedia<br />

Einheit, welche für Gleitkommaoperationen zuständig ist sowie Befehle des MMX Befehlssatzes unterstüzt. Weiterhin<br />

ist eine Load/Store Unit für Speicherzugriffe sowie eine Branch Unit für Sprungvorhersagen vorhanden.<br />

Jede der ALUs hat Zugriff auf 32 General Purpose Registers, 48 dieser gesamt 64 Register sind zusätzlich in so<br />

genannten Shadow Registern gespiegelt. Ähnlich verhält es sich mit den 32 Floating Point Registern von denen 16<br />

gespiegelt sind. <strong>Die</strong>se Shadow Register umfassen die x86 Zustände des Prozessors. Ihre nähere Bedeutung wird in<br />

Kapitel 4 erläutert.<br />

Eine weitere Besonderheit stellen der Gated Store Buffer, der Translation-Bit Buffer und die Alias Hardware dar. Sie<br />

dienen wie die Shadow Register der Ausnahmebehandlung des Prozessors und werden ebenfalls in Kapitel 4 näher<br />

erläutert.<br />

Abbildung 6: Hardwaredesign TM5400<br />

<strong>Die</strong> Schnittstelle für das LongRun Power Management ist ebenfalls in den Kern eingebunden.<br />

Es ist zu erkennen das der Crusoe eine integrierte Northbridge besitzt. <strong>Die</strong>se bietet neben einer Standard und DDR-<br />

SDRAM Unterstützung eine 32Bit, 33MHz PCI Interface.<br />

<strong>Die</strong> weiteren Komponenten sind ähnlich denen eines x86 Prozessors und sollen deshalb nicht näher erläutert werden.<br />

9

In Abbildung 7 ist zum Vergleich das Hardwaredesign des TM3120 dargestellt. In den wesentlichen Komponenten<br />

besteht kein Unterschied zum größeren Modell. Das Bild dient der Vollständigkeit.<br />

<strong>Die</strong> erkennbaren Unterschiede sind der geringere Cache, die fehlende DDR-SDRAM Unterstützung sowie das fehlende<br />

LongRun Power Management Interface. [4]<br />

Abbildung 7: Hardwaredesign TM3120<br />

10

<strong>3.</strong> <strong>Die</strong> <strong>Code</strong>-<strong>Morphing</strong>-<strong>Software</strong> (CMS)<br />

<strong>3.</strong>1 Einleitung<br />

Das Herz des Crusoe Prozessors liegt in der <strong>Code</strong>-<strong>Morphing</strong>-<strong>Software</strong>. Sie stellt einen dynamischen Übersetzer dar,<br />

welcher Instruktionen einer fremden Architektur in die Eigene übersetzt. <strong>Die</strong> <strong>Software</strong> ist in einem 512KB Flash-ROM<br />

Speicher abgelegt und wird beim Booten in den Hauptspeicher expandiert, wo sie 2MB Speicherplatz belegt. Sie stellt<br />

die einzige für den VLIW-Kern geschriebene <strong>Software</strong> dar. Im Wesentlichen wird sie für die Übersetzung von x86<br />

Instruktionen verwendet, wobei jedoch die Übersetzung anderer Architekturen ebenso denkbar ist (Übersetzen von Java<br />

Byte <strong>Code</strong> wurde bereits demonstriert). Zur Unterstützung stehen ihr 4-14MB Translation Cache zur Verfügung, welche<br />

vom Hauptspeicher des PCs abgezweigt werden.<br />

Mit diesem System ist es möglich veränderte Architekturen durch ein Flash Update auf dem Prozessor lauffähig zu<br />

machen. Ebenso können eventuelle Fehler der Architektur behoben werden. [1], [4], [6], [7]<br />

<strong>3.</strong>2 Befehlsverarbeitung<br />

Um den Übersetzungsvorgang näher zu betrachten, ist es zunächst notwendig die VLIW Befehle näher zu untersuchen.<br />

Sie haben eine Bandbreite von 64Bit beziehungsweise 128Bit und umfassen damit zwei oder vier einzelnen Befehle,<br />

welche von Transmeta als Atome bezeichnet werden. <strong>Die</strong> Bündel dieser Befehle werden Moleküle genannt. Alle Atome<br />

innerhalb eines solchen Moleküls werden parallel ausgeführt. Voraussetzung dafür ist, dass die entsprechende Anzahl an<br />

Funktionseinheiten vorhanden ist. [1]<br />

512kByte<br />

FlashROM<br />

CMS<br />

Decompress<br />

2 MBytes of<br />

Crusoe <strong>Code</strong><br />

14 MByte of<br />

Crusoe data<br />

Abbildung 8: CMS - Startup<br />

8 KB Crusoe<br />

Local Ins Mem<br />

8 KB Crusoe<br />

Local Data Mem<br />

Durch diese Einschränkung bleiben insgesamt sechs Molekülvarianten übrig, welche in Abbildung 9 dargestellt sind.<br />

Es gibt zwei Moleküle mit vier Atomen und vier Moleküle mit jeweils zwei Atomen. Spezielle Bits ermöglichen die<br />

Unterscheidung der einzelnen Moleküle und damit die richtige Verteilung auf die einzelnen Funktionseinheiten.<br />

Alle Moleküle enthalten ein sogenanntes Commit Flag, dessen Bedeutung in der Ausnahmebehandlung liegt. [4]<br />

11

Ein weiterer Aspekt der Molekülverarbeitung stellen die Pipelines dar (Abbildung 10). Ihre Länge ist um einiges kürzer,<br />

als bei vergleichbaren Prozessoren (Pentium IV: 20 Stufen). Ansonsten sind die wesentlichen Funktionen einer<br />

herkömmlichen Pipeline integriert. [4]<br />

Abbildung 9: Molekülkombinationen<br />

Abbildung 10: Pipelinestruktur<br />

In Abbildung 11 soll nun noch einmal der Unterschied in der Befehlsverwaltung zwischen x86, einem herkömmlichen<br />

VLIW Prozessor sowie dem Crusoe Prozessor dargestellt werden. Beim x86 erfolgt die Aufteilung auf einzelnen<br />

Funktionseinheit durch Prozessorhardware (Instruction Scheduler).<br />

Beim VLIW-Prozessor ist es für den Compiler bereits notwendig die vorhanden Funktionseinheiten zu kennen. Auf<br />

dieser Basis werden die Befehle bereits beim Übersetzen aufgeteilt.<br />

12

Der Crusoe arbeitet nach einem ähnlichen Prinzip. Da jedoch die Übersetzung Just In Time erfolgt, gilt dies auch für die<br />

Verteilung der Befehle. In diesem Fall wird sie von der <strong>Code</strong>-<strong>Morphing</strong>-<strong>Software</strong> übernommen. [4], [9]<br />

<strong>3.</strong>3 Struktur<br />

x86 VLIW<br />

Crusoe<br />

Abbildung 11: Befehlsverteilung verschiedener Architekturen<br />

<strong>Die</strong> <strong>Code</strong>-<strong>Morphing</strong>-<strong>Software</strong> besteht aus einem Interpreter und einem Translator.<br />

Der Interpreter führt die x86 Instruktionen In-Order aus, damit sind sowohl geordnete Speicherzugriffe als auch eine<br />

präzise Reproduktion von Fehlern möglich. Während der Ausführung werden Informationen über den <strong>Code</strong> gesammelt.<br />

<strong>Die</strong>se Informationen geben Aufschluss darüber, wie häufig ein <strong>Code</strong>block durchlaufen wird, zu welchem Pfad bei<br />

bedingten Sprüngen häufiger verzweigt wird und wann memory-mapped-I/O Operationen verwendet werden. <strong>Die</strong>ses<br />

Sammeln geschieht im Gegensatz zu einem <strong>Software</strong>-Profiler während der Ausführung. Damit passt sich der Prozessor<br />

optimal an den Benutzer an.<br />

<strong>Die</strong>se Art der Befehlsverarbeitung ist sehr langsam, dass heisst es werden mindestens 12 Takte je x86 Befehl benötigt.<br />

Wird ein <strong>Code</strong>block wiederholt aufgerufen (circa 50 mal), so wird seine Adresse zum Translator geschickt. [3]<br />

Der Translator wählt nun einen Bereich um diese Adresse herum aus. <strong>Die</strong>ser Bereich wird schrittweise in VLIW <strong>Code</strong><br />

übersetzt. Zunächst dekodiert das frontend die Befehle und übersetzt sie in Atome. Anschliessend führt der optimizer<br />

bestimmt Compilerähnliche-, x86-spezifische oder VLIW-spezifische Optimierungen durch. Bevor im dritten Schritt der<br />

scheduler die Atome zu Molekülen zusammenfasst.<br />

Der übersetzte Block wird im Translation Cache abgelegt und bis zur eventuellen Neuübersetzung aus diesem heraus<br />

ausgeführt. Ein solcher <strong>Code</strong>block kann bis zu 200 x86 Instruktionen umfassen. [3]<br />

In Abbildung 12 ist das Flussdiagramm der CMS dargestellt. Eine Befehlsfolge trifft zunächst auf den Interpreter.<br />

<strong>Die</strong>ser untersucht ob das Ausführungslimit bereits überschritten wurde. Ist dies nicht der Fall so interpretiert er den<br />

entsprechenden Befehl, andernfalls wird die Adresse zum Translator übergeben. <strong>Die</strong>ser übersetzt den <strong>Code</strong>, speichert<br />

ihn im Translation Cache und führt ihn von dort aus. Verweist ein Sprung innerhalb dieses Blocks auf einen anderen, so<br />

wird dieser als Kette aus dem Cache heraus ausgeführt (Chain). Nach dem die Instruktion interpretiert oder aus dem<br />

13

Translation Cache heraus ausgeführt wurde, wird überprüft, ob sich der nächste <strong>Code</strong>block ebenfalls bereits im<br />

Translation Cache befindet. Ist dies der Fall, so wird er von dort aus ausgeführt. Andernfalls übernimmt der Interpreter<br />

seine Verarbeitung.<br />

Eine Besonderheit stellt der Fall dar, bei dem es während der Ausführung zu einer Exception (Ausnahme) kommt. <strong>Die</strong>s<br />

kann durch herkömmliche Fehler wie Page Fault oder Division durch 0, durch Interrupts oder aufgrund der Übersetzung<br />

ausgelöst werden. [3]<br />

Interpreter<br />

not<br />

found<br />

Start<br />

exceeded<br />

translation<br />

Threadhold?<br />

find next<br />

instruction<br />

in Tcache?<br />

Abbildung 12: Flussdiagramm der CMS<br />

<strong>Die</strong> einzelnen Möglichkeiten zur Optimierung sollen im Folgenden kurz erläutert werden. Zunächst werden die<br />

Compilerähnlichen-Optimierungsverfahren in Tabelle 2 dargestellt. [5]<br />

Optimierung Beschreibung<br />

Common Subexpression Elimination Redundante Anweisungen und Ausdrücke werden eliminiert.<br />

Beispiel: P=A+B+C, Q=A+B+D --> Zusammenfassen von A+B: S=A+B --><br />

Einsetzen in Ausgangsgleichungen: P=S+C, Q=S+D<br />

Copy Propagation Zuweisungen wie X:=Y werden weit gehend vermieden. Es wird so lange wie<br />

möglich wird mit Y gearbeitet.<br />

Dead-<strong>Code</strong> Elimination <strong>Code</strong> der nicht ausgeführt wird, wird entfernt.<br />

Constant Folding Ist eine Variable über den gesamten Programmablauf konstant, so wird sie<br />

durch die entsprechenden Konstante ersetzt.<br />

Loop Invariant <strong>Code</strong> Removal <strong>Code</strong>, welcher innerhalb einer Schleife nicht verwendet wird, wird ausserhalb<br />

der Schleife platziert.<br />

Loop Strength Reduction Komplizierte Ausdrücke innerhalb von Schleifen werden vereinfacht.<br />

Beispiel: for (j=x;j>0;j--) {t=4*j; ...} Ersetzen durch: t:=x; for (j=x;j>0;j--)<br />

{t=t-4;...}<br />

Loop Induction-Variable Elimination Elimination von Zählvariablen innerhalb von Schleifen.<br />

Tabelle 2: Compilerähnliche Optimierungen<br />

no<br />

interpret<br />

next<br />

instruction<br />

yes<br />

no fault<br />

found<br />

Rollback<br />

fault<br />

translate region,<br />

store in Tcache<br />

execute<br />

translation<br />

from<br />

Tcache<br />

Beispiel: t=4*j;u=4*i; --> i>j ist identisch mit u>t<br />

chain<br />

Translator<br />

14

Neben den Compilerähnlichen Optimierungen gibt es noch x86 spezifische Optimierungen. <strong>Die</strong>se beschränken sich auf<br />

das Entfernen unnötig gesetzter Condition <strong>Code</strong>s. Setzt eine Instruktion bestimmte Flags, welche jedoch von Programm<br />

nicht ausgelesen werden, so ist es nicht notwendig diese Flags zu setzen.<br />

<strong>Die</strong> letzte Gruppe bilden die VLIW spezifischen Optimierungen. Sie entfernen unnötige Sprünge und können somit<br />

mehrere x86 <strong>Code</strong>blöcke vereinen. [1], [3]<br />

Der Ablauf einer Schrittweisen Übersetzung ist in Abbildung 13 dargestellt. [1]<br />

addl<br />

x86 <strong>Code</strong><br />

%eax,(%esp) // load data from stack, add to %eax<br />

addl %ebx,(%esp) // ditto, for %ebx<br />

movl %esi,(%ebp) // load %esi from memory<br />

subl %ecx,5 // substract 5 from %ecx register<br />

frontend<br />

ld %r30,[%esp] // load data from stack into temporary<br />

add.c %eax,%eax,%r30 // add to %eax, set condition codes<br />

ld %r31,[%esp]<br />

add.c %ebx,%ebx,%r31<br />

ld %esi,[%ebp]<br />

sub.c %ecx,%ecx,5<br />

optimizer<br />

ld %r30,[%esp] // load data from stack only once<br />

add %eax,%eax,%r30<br />

add %ebx,%ebx,%r30 // reuse data loaded earlier<br />

ld %esi,[%ebp]<br />

sub.c %ecx,%ecx,5 // only this last condition code needed<br />

scheduler<br />

ld %r30,[%esp]; sub.c %ecx,%ecx,5<br />

ld %esi,[%ebp]; add %eax,%eax,%r30; add %ebx,%ebx,%r30<br />

Abbildung 13: Beispiel einer schrittweisen Übersetzung<br />

15

4. Hardwareunterstützung für <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong><br />

4.1 Ausnahmebehandlung<br />

In einem herkömmlichen Prozessor erfolgt die Ausnahmebehandlung durch Hardwaremechanismen. <strong>Die</strong>se ermöglichen<br />

es, Befehlsketten rückgängig zu machen und somit wieder einen gültigen Zustand im Prozessor herzustellen.<br />

Der Crusoe Prozessor verwendet zur Ausnahmebehandlung zwei Registersätze, welche bereits im Kapitel 2 erwähnt<br />

wurden. Man spricht von der sogenannten „Working Copy“ und von der „Shadow Copy“.<br />

Werden Atome ausgeführt, so wird stets die Working Copy verändert. Wird ein <strong>Code</strong>block vollständig ausgeführt, ohne<br />

dass eine Ausnahme aufgetreten ist, so wird im ersten Molekül des folgenden <strong>Code</strong>blocks das Commit Flag auf wahr<br />

gesetzt. <strong>Die</strong>s bewirkt eine Übertragung aller Werte aus der Working Copy in die Shadow Copy. Es wird also der letzte<br />

gültige Zustand des Prozessors gespeichert.<br />

<strong>Die</strong> Übertragung zwischen den Registern läuft dabei nahezu ohne Zeitverlust ab.<br />

Tritt während der Ausführung eine Exception auf, so sorgt ein Rollback Befehl für das Wiederherstellen der letzten<br />

gültigen Sicherheitskopie. Es werden also alle Werte der Shadow Copy in die Working Copy übertragen. Anschliessend<br />

werden die Befehle des <strong>Code</strong>blocks vom Interpreter In-Order ausgeführt. Dadurch kann die exakte Stelle der Exception<br />

ermittelt werden.<br />

Schwieriger ist es die Änderungen im Speicher zu verfolgen. Dafür ist der Gated Store Buffer zuständig. Sämtliche<br />

Speicher-Operationen werden werden zunächst in ihm ausgeführt. Bei einem Commit werden die Werte in den<br />

Hauptspeicher übertragen. Ein Rollback sorgt für das Leeren des Puffers.<br />

Je nachdem wie häufig ein Fehler auftritt wird der <strong>Code</strong> entweder vom Interpreter übernommen oder er wird neu<br />

übersetzt. <strong>Die</strong> Angaben beziehen sich auf [1], [3], [4].<br />

4.2 Alias Hardware<br />

Es ist klar, dass die Freiheit des Schedulers ausschlaggebend für die Performance des Prozessors ist. Je freier er die<br />

Gruppierung der Atome vornehmen kann, umso schneller kann das Programm ausgeführt werden. Dabei ist es wichtig,<br />

dass Speicheroperationen beim Vertauschen berücksichtigt werden. Allgemein ist es günstig load vor store Befehlen<br />

auszuführen, da nachfolgende Operationen nicht auf die Operanden warten müssen. Sollte allerdings ein load ein<br />

vorheriges store benötigen und diese Anweisungen vertauscht wurden sein, so muss dies bei der Ausführung bemerkt<br />

werden. [1]<br />

Hierfür ist die sogenannte Alias Hardware implementiert. Wird ein load Befehl vor einen store Befehl gesetzt, so wird er<br />

durch load-and-protect ersetzt. Dabei wird die Adresse, von welcher geladen wird sowie die Größe des zu ladenden<br />

Datenblocks im Alias-Buffer abgelegt. Der entsprechende store Befehl wird durch store-under-alias-mask ersetzt. <strong>Die</strong>ser<br />

16

Befehl untersucht zusätzlich, ob er in einen durch load-and-protect geschützten Speicherbereich schreibt.<br />

Sollte ein store Befehl einen solchen Bereich überschreiben, so wird eine Exception aufgerufen und ein Rollback<br />

durchgeführt. [1]<br />

Dadurch ist ein sicheres Vertauschen der Operationen möglich. Abbildung 14 zeigt in einem Beispiel diesen Vorgang.<br />

Abbildung 14: Beispiel Alias Hardware<br />

Es ist möglich den zweiten load Befehl zu eliminieren und mit dem bereits vorher geladenen Wert zu arbeiten. Dabei ist<br />

es jedoch wichtig, dass der store Befehl nicht auf die zu ladende Adresse schreibt. Deshalb werden die Befehle<br />

entsprechend durch load-and-protect und store-under-alias-mask ersetzt. Sollte der store Befehl die zu ladende Adresse<br />

überschreiben, so wird eine Exception aufgerufen. [1]<br />

Abbildung 15 zeigt nun den Ablauf beim Vertauschen von load und store Befehlen.[6]<br />

Alias Buffer stam<br />

yes<br />

Raise<br />

Exception<br />

ldp<br />

ld %r30,[%x] // first load from location X<br />

…<br />

st %data,[%y] // might overwrite location X<br />

ld %r31,[%x] // this accesses location X again<br />

use %r31<br />

ldp %r30,[%x] // load from X and protect it<br />

…<br />

stam %data,[%y] // this store traps if it writes X<br />

use %r30 // can use data from first load<br />

Addr Size<br />

Abbildung 15: Ablauf Alias Hardware<br />

Ein Phänomen, was bei der Verwendung von Aliasing auftreten kann ist das sogenannte falsche Aliasing, welches in<br />

Abbildung 16 in einem kleinen Beispiel dargestellt ist.<br />

Original Übersetzt<br />

…<br />

st %w,[%data1]<br />

ld %data2, [%x]<br />

st %y, [%data3]<br />

ld %data4, [%z]<br />

Abbildung 16: Falsches Aliasing<br />

Aliasing?<br />

Beide load Befehle werden vor einen store Befehl gesetzt und folglich werden sie durch load-and-protect ersetzt, ebenso<br />

werden die store Befehle durch store-under-alias-mask ersetzt. <strong>Die</strong> Reihenfolge des zweiten und dritten Befehls wurde<br />

dabei nicht verändert. Trotzdem kommt es zu einer Exception, falls X=Y ist. [6]<br />

no<br />

ldp %data2, [%x]<br />

ldp %data4, [%z]<br />

stam %w, [%data1]<br />

stam %y ,[%data3]<br />

X=Y<br />

Continue<br />

Execution<br />

Exception<br />

17

4.3 Selbstmodifizierender <strong>Code</strong><br />

4.<strong>3.</strong>1 Einleitung<br />

Ein weiteres Problem, mit dem dynamische Übersetzer wie die <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong> umgehen müssen ist<br />

Selbstmodifizierender <strong>Code</strong>. Er tritt zum Beispiel auf, wenn das Betriebssystem ein neues Programm in den<br />

Hauptspeicher lädt. Aber auch Programme selbst können ihren <strong>Code</strong> während der Laufzeit ändern.<br />

Wurde dieser <strong>Code</strong> bereits von der <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong> übersetzt, so muss diese die Änderungen bemerken. [1],<br />

[3]<br />

Um dies zu realisieren wird der Translation-Bit Buffer genutzt. Für jeden übersetzten Speicherbereich wird ein Bit in<br />

diesem Puffer gesetzt. Sollte nun ein Schreibzugriff auf diesen Speicherbereich durchgeführt werden, so wird der<br />

entsprechende <strong>Code</strong>block neu übersetzt.<br />

Ziel ist es, bei selbstmodifizierendem <strong>Code</strong> ein häufiges Neuübersetzten zu vermeiden. <strong>Die</strong>s wäre insbesondere dann<br />

notwendig, wenn <strong>Code</strong> und Daten vermischt in einem Speicherbereich liegen. Bei jeder Datenänderung würde ebenso<br />

der <strong>Code</strong> neu übersetzt werden.<br />

Um die Zahl der Neuübersetzungen zu verringern, sind verschiedene Verfahren in der CMS implementiert. <strong>Die</strong>se<br />

Verfahren sollen in den nächsten Kapiteln vorgestellt werden. Alle Verfahren sind der Quelle [3] entnommen.<br />

4.<strong>3.</strong>2 Fine Grain Protection<br />

Das erste Verfahren ist die Fine Grain Protection. <strong>Die</strong>ses relativ einfache Verfahren sorgt dafür, dass mit dem<br />

Translation Bit nicht immer eine komplette Seite im Speicher geschützt werden muss. Lässt sich dieser geschützte<br />

Bereich also verkleinern, dann sinkt die Wahrscheinlichkeit, dass bei einem <strong>Code</strong> Daten Mix der <strong>Code</strong>block neu<br />

übersetzt wird, wenn sich nur der Datenbereich geändert hat.<br />

Wichtig ist hierbei, dass dieses Verfahren nur für wenige Bereiche gleichzeitig verwendet wird. Damit ist es möglich<br />

den Speicheraufwand für die übersetzten Bereich zu minimieren.<br />

4.<strong>3.</strong>3 Self Revalidating Translations<br />

Das zweite solche Verfahren sind die Self Revalidating Translations.<br />

Bemerkt die <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong> den <strong>Code</strong> Daten Mix, so wird der Übersetzung ein Prolog vorangestellt. Dabei ist<br />

es notwendig, dass die Startadresse des <strong>Code</strong>blocks durch die Adresse des Prologs ersetzt wird.<br />

Der konkrete Ablauf soll im Folgenden erläutert werden. Zunächst wird der entsprechende <strong>Code</strong>, mit einem Flag<br />

18

gekennzeichnet. Wird er danach aufgerufen, so wird der Bereich neu übersetzt. Dabei wird der <strong>Code</strong> aus den Daten<br />

herausgefiltert. Erkennt nun die Fine Grain Protection einen Schreibzugriff auf den Bereich, so wird der Prolog aktiviert.<br />

Zusätzlich wird der Schutz für den Speicherbereich abgeschaltet. Dadurch verursacht ein erneuter Schreibzugriff auf den<br />

Bereich kein Neuübersetzen des <strong>Code</strong>s.<br />

Wird der <strong>Code</strong> später erneut aufgerufen, so gibt der Prolog Auskunft darüber, ob er sich durch die Schreibzugriffe<br />

verändert hat. Sollte dies der Fall sein, so wird er erneut übersetzt.<br />

Ist der <strong>Code</strong> unverändert, so wird die Protection wieder aktiviert, der <strong>Code</strong> wird verifiziert, der Prolog deaktiviert und<br />

schließlich wird der <strong>Code</strong> ausgeführt.<br />

<strong>Die</strong> Self Revalidating Translations sind sinnvoll, wenn der <strong>Code</strong> relativ selten verändert wird. Somit kann ein häufiges<br />

Neuübersetzen vermieden werden.<br />

4.<strong>3.</strong>4 Self Checking Translation<br />

Ein den Self Revalidating Translations ähnliches Verfahren stellen die Self Checking Translations dar.<br />

Hierbei bleibt der Speicherbereich komplett ungeschützt. Dazu ist es notwendig, dass der <strong>Code</strong> selbst prüft, ob er<br />

verändert wurde. Dabei wird der ursprünglichen Übersetzung <strong>Code</strong> zum Überprüfen hinzugefügt. Sollte dieser <strong>Code</strong><br />

eine Veränderung feststellen, so wird ein Rollback ausgelöst gesendet.<br />

Eine wichtige Bedingung hierbei ist, dass der <strong>Code</strong> zum Überprüfen nach sämtlichen store Operationen ausgeführt wird.<br />

Denn diese store Befehle könnten den <strong>Code</strong> verändern. Folglich darf die Alias Hardware diesen <strong>Code</strong> zum Überprüfen<br />

nicht umsortieren.<br />

<strong>Die</strong>ses Verfahren bietet vor allem bei selten ausgeführtem <strong>Code</strong> Einsparungen. Es tritt hierbei ein Overhead von circa<br />

83% auf, jedoch ist die Ausführung dieses Overheads schneller als der Aufruf des Interpreters beziehungsweise die<br />

komplette Neuübersetzung.<br />

4.<strong>3.</strong>5 Stylized SMC<br />

<strong>Die</strong> bisher vorgestellten Verfahren sind vor allem dann sinnvoll, wenn nur die Daten innerhalb eines Speicherbereichs<br />

verändert werden. Wenn sich der <strong>Code</strong> selbst ändert erfordern sie jedoch eine komplette Neuübersetzung.<br />

Anders ist es beim Stylized SMC. Hierbei wird durch eine geschickte Übersetzung vermieden, dass viele <strong>Code</strong>-<br />

Änderungen auftreten.<br />

Als Beispiel soll der Offset in einer Schleife dienen (Abbildung 17).<br />

label: add %eax, 0x123456<br />

ld<br />

add<br />

%temp, [label+1]<br />

%eax, %eax, %temp<br />

Abbildung 17: Beispiel Stylized SMC<br />

Angenommen die Adresse 0x123456 stellt den Index in einer Schleife dar. Bei jedem Durchlauf würde nun der <strong>Code</strong><br />

19

verändert werden. Damit wäre für jeden Schleifendurchlauf ein Aufruf des Interpreters nötig.<br />

<strong>Die</strong> Übersetzung scheint nun zunächst etwas untypisch. Das vorherige label dient zum Auslesen des Offsets. <strong>Die</strong><br />

Adresse [label+1] enthält nun bei jedem Durchlauf den aktuell zu lesenden Speicherbereich. <strong>Die</strong> Daten werden also<br />

direkt aus dem <strong>Code</strong>-Stream gelesen.<br />

<strong>Die</strong>ses Verfahren vermeidet häufige Neuübersetzungen trotz ursprünglicher Veränderung des <strong>Code</strong>s, es ist jedoch<br />

zusätzlich mit Self Revalidating oder Self Checking zu Überprüfen, ob sich der <strong>Code</strong> selbst verändert hat.<br />

4.<strong>3.</strong>6 Translation Groups<br />

Beim letzten Verfahren zur Vermeidung von Neuübersetzung geht man davon aus, dass es lediglich eine geringe Anzahl<br />

verschiedener Versionen des modifizierten <strong>Code</strong>s gibt. Ist dies der Fall, so ist es sinnvoll die alten Versionen des <strong>Code</strong>s<br />

für die spätere Verwendung zu speichern.<br />

<strong>Die</strong> <strong>Code</strong>-<strong>Morphing</strong>-<strong>Software</strong> kann diese Übersetzungen in sogenannten Translation Groups hinterlegen. Dabei steht die<br />

letzte verwendete Version am Anfang der Liste.<br />

Trifft die CMS auf einen <strong>Code</strong>block wird zunächst überprüft, ob die erste Version gültig ist. Schlägt dies fehl, so wird<br />

der Rest der Liste nach der passenden Version durchsucht. Wird ein passender <strong>Code</strong>block gefunden so wird er an den<br />

Anfang der Liste gebracht und ausgeführt. Findet sich in der gesamten Liste ein passender Block, so wird der <strong>Code</strong> neu<br />

übersetzt und der neue Block an den Anfang der Liste verschoben.<br />

20

5. LongRun Power Management<br />

5.1 Einleitung<br />

<strong>Die</strong> Bedeutung von Power Management Technologien begann mit der Einführung von leistungsstarken PCs für den<br />

privaten Gebrauch. Es war wichtig geworden Strom zu sparen und somit die Kosten zu senken. Eine besondere<br />

Bedeutung hat das Power Management jedoch im mobilen Sektor. Es ist entscheidend für die Akku-Laufzeit von<br />

Notebooks.<br />

Das Minimieren des Stromverbrauchs hat ebenso eine geringere Abwärme zur Folge. Damit können Kosten für teure<br />

Kühlsysteme gespart werden. Gleichzeitig werden Systeme leiser.<br />

<strong>Die</strong> verschiedenen Technologien des Power Managements sollen in Tabelle 3 kurz mit ihrer Einführungszeit und<br />

gegebenenfalls dem Hersteller genannt werden.<br />

Jahreszahl Technologie<br />

1990 APM (Advanced Power Management)<br />

1995 ACPI (Advanced Configuration and Power Interface)<br />

2000 SpeedStep (Intel)<br />

2000 LongRun (Transmeta)<br />

2000 PowerNow! (AMD)<br />

2003 Enhanced SpeedStep (Intel)<br />

2003 Enhanced LongRun (Transmeta)<br />

Tabelle 3: Power Management Technologien<br />

Herkömmliche Methoden des Power Managements basieren auf einem stetigen An- und Abschalten des Prozessors.<br />

<strong>Die</strong>s führt zu einem linearen Verhalten zwischen Leistungsaufnahme und Performance wie in Abbildung 18 zu sehen ist.<br />

[2]<br />

Abbildung 18: Lineares Power Management<br />

21

5.2 LongRun Fähigkeiten<br />

Im Gegensatz zum herkömmlichen Power Management ermöglicht LongRun ein flexibles Verändern von Takt und<br />

Spannung. So lassen sich Frequenzen in 33 MHz Schritten und Spannungen in 25mV Stufen variieren. Insgesamt sind<br />

200 dieser Änderungen je Sekunde möglich.<br />

<strong>Die</strong> minimale Frequenz beträgt beim TM5400 300MHz, unter dieser Grenze wird das normale ACPI mit An- und<br />

Abschalten des Prozessors verwendet. Dadurch, dass Takt und Spannung nicht im gleichen Verhältnis geändert werden<br />

müssen, wird kein lineares Verhalten zwischen Performance und Leistungsaufnahme erreicht. Damit kann mehr Strom<br />

eingespart werden (Abbildung 19). [2], [4]<br />

Abbildung 20 zeigt die Vorteile von LongRun im Vergleich zum herkömmlichen Power Management. Um den<br />

Prozessor bei herkömmlichen Methoden auf die Hälfte des Taktes zu reduzieren, wird er 50% der Laufzeit in den Sleep<br />

State versetzt. LongRun senkt die Frequenz um weniger als 50% und kann gleichzeitig die Spannung auf mehr als 50%<br />

absenken. [2]<br />

Abbildung 19: LongRun Power Management<br />

Abbildung 20: LongRun im Vergleich<br />

22

5.3 LongRun Funktionsweise<br />

Wie die Absenkung/Erhöhung von Takt und Spannung funktioniert, soll im folgenden Abschnitt erläutert werden.<br />

Ändert sich die Prozessorauslastung, so wird dies von der <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong> durch das sogenannte<br />

CMS-Monitoring bemerkt.<br />

Ist die Auslastung größer, so gibt LongRun dem Chip vor seine Spannung zu erhöhen. Stabilisiert sich die Spannung auf<br />

den neuen Wert, wird die Frequenz angepasst.<br />

Ist die Auslastung geringer, wird zunächst die Frequenz abgesenkt, synchronisiert sich die Frequenz auf den<br />

vorgegebenen Wert (PLL- phase lock loop) so wird die Spannung abgesenkt. [4]<br />

<strong>Die</strong> Frequenzänderung muss dabei nicht in einzelnen 33Mhz Schritten erfolgen. Soll beispielsweise der Takt von<br />

600MHz auf 700MHz angehoben werden, so wird zunächst die Spannung in Einzelschritten auf 1.6V gesetzt.<br />

Anschliessend „springt“ die Frequenz auf 700MHz. [4]<br />

Um ein effizientes Power Management zu ermöglichen, ist es notwendig die Reaktionszeiten sehr gering zu halten. <strong>Die</strong><br />

Änderung der Prozessorauslastung kann in ½µs festgestellt werden. Spannungsänderungen werden in weniger als 20µs<br />

durchgeführt.<br />

Im Worts Case bedeutet diese lediglich eine Zeitspanne von 280µs bei einer Spannungsänderung von 1.1V auf 1.6V und<br />

einer Frequenzänderung von 200MHz auf 700MHz. [4]<br />

Ein weiterer Vorteil der LongRun Technologie besteht darin, dass bei einer Änderung der Spannung kein Abschalten<br />

des Prozessors notwendig ist. Lediglich das PLL erfordert ein Abschalten von maximal 20µs. [4]<br />

5.4 Weitere LongRun Leistungen<br />

In den letzten Kapiteln wurde die LongRun Technologie mit ihren grundlegenden Fähigkeiten vorgestellt. Neben diesen<br />

gibt es noch weitere Vorteile gegenüber anderen Systemen.<br />

In Kapitel 2 wurde die in den Prozessor integrierte Northbridge genannt. Von ihr profitiert ebenso das LongRun Power<br />

Management. So ist es möglich den Takt und die Spannung des Speichers ebenso wie die des Kerns zu verändern<br />

(Abbildung 21). <strong>Die</strong>s ermöglicht ein weiteres Herabsenken der Leistungsaufnahme.<br />

Ebenso beinhaltet LongRun eine Technologie namens LongRun Thermal Extension (LTX), welche mit einem<br />

sogenannten „termal budget“ arbeitet. Der Benutzer kann dabei festlegen, wie viel Strom verbraucht werden darf. Im<br />

Performance Mode gibt es beispielsweise keine Einschränkungen für Takt und Spannung. Im Economy Mode wird ein<br />

maximaler Stromverbrauch festgelegt. Somit kann der Nutzer selbst entscheiden, ob er seine Priorität auf volle<br />

Performance oder auf lange Akku Laufzeiten legt.<br />

Damit entsprechenden Änderungen der Lüfterdrehzahl und der Takt und Spannungsänderungen effizient arbeiten,<br />

werden die Clock Throttling Register aus der Southbridge vom BIOS in die Northbridge repliziert. Damit kommt es bei<br />

der Übertragung zu keinem Overhead. [2], [4]<br />

23

Abbildung 21: Integrierte Northbridge<br />

24

6. Zusammenfassung<br />

In der vorliegenden Ausarbeitung wurde ein Überblick über den Crusoe Prozessor der Firma Transmeta gegeben. Im<br />

Vordergrund dabei stand die <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong>, welche das Herzstück des Prozessors ist. Es wurde erläutert wie<br />

diese <strong>Software</strong> das Ausführen von x86 Anwendungen auf dem VLIW-Kern ermöglicht.<br />

Um das Reibungslose Übersetzen zu ermöglichen benötigt der Crusoe verschiedene Hardwareimplementationen, welche<br />

vor allem die Ausnahmebehandlung unterstützen. Neben der <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong> wurde auch das LongRun Power<br />

Management vorgestellt. <strong>Die</strong>ses erlaubt es, dass Notebooks ihre Akku Laufzeit erheblich vergrößern.<br />

Der Crusoe bietet ein neuartiges und innovatives Konzept. <strong>Die</strong> Möglichkeit neben x86 Befehlen auch andere<br />

Instruktionen zu übersetzen bietet ein breites Einsatzspektrum. Leider wurde diese Möglichkeit bisher nicht<br />

ausgeschöpft.<br />

Der übersetzte <strong>Code</strong> wird umso schneller, je länger Anwendungen ausgeführt werden. Ist er vollständig optimiert, so<br />

steigt die Ausführungsgeschwindigkeit stark an. Darin ist ein besonderer Vorteil des Crusoe zu sehen, da solch<br />

vielseitige Optimierungen bei herkömmlichen Prozessoren fehlen.<br />

Ebenso Vorteilhaft ist, dass die CMS per Flash Update aktualisiert werden kann. Damit können Fehler innerhalb der<br />

Architektur ausgeglichen werden und es ist eine Implementierung neuer Befehle möglich. Eine solche Funktion ist in<br />

anderen Prozessoren ebenfalls kaum vorhanden.<br />

Ausserdem ist der Crusoe Prozessor aufgrund des geringen Hardware Teils kostengünstig zu erwerben und durch den<br />

geringen Energieverbrauch können weitere Einsparungen erzielt werden.<br />

Neben diesen positiven Eigenschaften gibt es in der Crusoe-Architektur auch durchaus Nachteile. So ist die Performance<br />

besonders beim Häufigen Wechsel von Aufgaben sehr gering, da die CMS diese <strong>Software</strong>teile nicht optimiert.<br />

Weiterhin ist der zusätzliche Speicherbedarf zu nennen. In heutigen Systemen fallen die 16MB, welche als Translation<br />

Cache verwendet werden kaum ins Gewicht. Betrachtet man jedoch Webpads oder einfache Subnotebooks, so können<br />

sich diese Speichereinbußen negativ auf die Performance auswirken.<br />

Ein weiteres Problem stellt die Ausnahmebehandlung dar. Sie ist perfekt auf die Architektur zugeschnitten, muss jedoch<br />

aufgrund der dynamischen Übersetzung relativ komplex implementiert werden. Besonders bei der Verwendung von<br />

Selbstmodifizierendem <strong>Code</strong> sind dabei Performanceverluste in Kauf zu nehmen.<br />

Abschliessend ist zu sagen, das Crusoe ein im Gesamteindruck positives Konzept liefert. Es ist jedoch bisher nicht<br />

gelungen auf dem Markt Fuss zu fassen. <strong>Die</strong> Entwicklung des Efficeon Prozessors wird ausschlaggebend für die Zukunft<br />

von Transmeta sein.<br />

25

Literaturverzeichnis<br />

[1] Alexander Klaiber: The Technology Behind Crusoe Processors. White paper, Transmeta Corporation, Januar<br />

2000<br />

[2] Marc Fleischmann: LongRun Power Management – Dynamic Power Management for Crusoe Processors.<br />

White paper, Transmeta Corporation, 17.01.2001<br />

[3] James C. Dehnert, u.w.: The Transmeta <strong>Code</strong> <strong>Morphing</strong> <strong>Software</strong> – Using Speculation, Recovery, and<br />

Adaptive Retranslation to Adress Real-Life Challenges. White paper, Transmeta Corporation<br />

[4] Tom R. Halfhill: Transmeta breaks x86 Low-Power Barrier – VLIW Chips use Hardware-Assisted x86<br />

Emulation. Microprocessor Report, 14.2.2001<br />

[5] A. Artale: Principle of Compilers: Lecture IX: Principles of <strong>Code</strong> Optimization. Vorlesungsunterlagen, Free<br />

University of Bolzano, 2004<br />

[6] Erik R. Altman: Dynamic Binary Translation and Optimization: DAISY, Crusoe, Dynamo. Micro-33 Tutorial,<br />

1<strong>3.</strong>12.2000<br />

[7] Andreas Stiller: Zu Neuen Ufern – Transmeta enthüllt Crusoe Design. Zeitschriftenartikel in c't 2000/03 S. 32,<br />

Heise Verlag<br />

[8] Nico Ernst: Transmeta-Crusoe im Detail. http://www.tecchannel.de/hardware/256/index.html, 24.01.2000<br />

Stand 12.12.2004.<br />

[9] <strong>Die</strong>ter Kranzlmüller: Transmeta's Crusoe. Vorlesungsunterlagen Technische Informatik und Telematik. UNI<br />

Linz<br />

[10] Transmeta Corp., http://www.ecoreporter.de, Stand 12.11.2004<br />

[11] http://www.transmeta.com<br />

Abbildungsquellen<br />

Abbildung 1 : [8]<br />

Abbildungen 2,3 : [11]<br />

Abbildungen 4,5 : [1]<br />

Abbildungen 6,7,9,10 : [4]<br />

Abbildung 11 : [9]<br />

Abbildungen 18,19,20,21 : [2]<br />

26