7. Speicher - Rechnersysteme

7. Speicher - Rechnersysteme

7. Speicher - Rechnersysteme

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>7.</strong> <strong>Speicher</strong><br />

Inhalt<br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

<strong>7.</strong>2 Cache-Organisation<br />

<strong>7.</strong>3 SRAM<br />

<strong>7.</strong>4 DRAM<br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

<strong>7.</strong>6 Festplatten<br />

<strong>7.</strong>7 DMA<br />

<strong>7.</strong> <strong>Speicher</strong><br />

Fachgebiet <strong>Rechnersysteme</strong>1<br />

<strong>Rechnersysteme</strong> I

<strong>7.</strong> <strong>Speicher</strong><br />

Lernziele von Kap. 7:<br />

� Organisationsformen und Realisierungsmöglichkeiten von<br />

Caches und virtuellem <strong>Speicher</strong> kennen<br />

� Eigenschaften und inneren Aufbau von SRAM- und DRAM-<br />

<strong>Speicher</strong>n verstehen<br />

� Methoden der Zugriffsbeschleunigung bei RAM-<br />

Bausteinen (Synchronisierung, Burst, Pipelining) kennen<br />

� Basiseigenschaften von Flash- und Platten-<strong>Speicher</strong>n<br />

wissen<br />

� Konzepte: voll/teil-assoziativer und direkt-abbildender<br />

Cache, write-through, write-back, write-allocate, write-notallocate,<br />

CAM, wide-bus RAM, Burst, floating-gate, Flash,<br />

DMA<br />

2

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Die in digitalen Systemen benutzten <strong>Speicher</strong><br />

unterscheiden sich stark hinsichtlich ihrer Kapazität,<br />

Zugriffsgeschwindigkeit und Kosten<br />

3

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Die Kapazität eines <strong>Speicher</strong> ist das Produkt<br />

� der Anzahl der adressierbaren Worte<br />

� und der Wortbreite<br />

─ Beispiel: ein <strong>Speicher</strong> von 1 KB (Kilo-Byte)<br />

Adressleitungen<br />

10<br />

Adressdekodierer<br />

<strong>Speicher</strong><br />

0<br />

...<br />

1023<br />

8<br />

1024<br />

8 Bit-Worte<br />

8<br />

4

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Kapazitäten werden als Vielfaches von Bit oder Byte<br />

angegeben<br />

� dabei werden Zweierpotenzen abgekürzt:<br />

K ~ 210 , M ~ 220 , G ~ 230 � kb Kilo-Bit, Mb Mega-Bit<br />

� kB Kilo-Byte, MB Mega-Byte, GB Giga-Byte<br />

� die Kapazität eines <strong>Speicher</strong>s wird oft explizit als Produkt<br />

der Anzahl der Worte und der Wortbreite angegeben, um<br />

die Organisationsform zu kennzeichnen<br />

─ Beispiel: ein 256K * 4 Bit-<strong>Speicher</strong> enthält 218 4-Bit<br />

Worte und hat eine Kapazität von 128 KB<br />

5

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Die Zugriffszeit eines <strong>Speicher</strong>s ist die Zeit vom Anlegen<br />

der Adresse bis zum Erscheinen der ausgelesenene<br />

Daten am Ausgang des <strong>Speicher</strong>s<br />

Adressleitungen<br />

Daten D<br />

Zugriffszeit<br />

Adressleitungen<br />

10<br />

Adressdekodierer<br />

<strong>Speicher</strong><br />

0<br />

...<br />

1023<br />

8<br />

1024<br />

8 Bit-Worte<br />

8<br />

Daten D<br />

6

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Die Datenrate eines <strong>Speicher</strong>s<br />

� Datenrate = Bitbreite des ausgelesenen Datenwortes/<br />

Zugriffszeit<br />

─ Beispiel: 256K*4 SRAM-<strong>Speicher</strong>, Zugriffszeit 12ns:<br />

Datenrate = 4 Bit/12ns ≈ 4Bit * 83MHz =<br />

41,5 MB/sec.<br />

─ Beispiel: 64K*16 SRAM-<strong>Speicher</strong>, Zugriffszeit 15ns:<br />

Datenrate = 16 Bit/15ns ≈ 16Bit * 67MHz ≈<br />

134 MB/sec.<br />

7

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Datenrate und Kapazität verschiedener <strong>Speicher</strong>technologien<br />

Datenrate<br />

Bits/sec.<br />

1G bipolar<br />

10M<br />

CMOS SRAM<br />

CMOS<br />

DRAM Magnetplattenspeicher<br />

1M 100M 10G Kapazität<br />

Magnetband<br />

Bits<br />

Quelle: Haraszti, CMOS Memory Circuits<br />

8

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Wachstum der Integrationsdichte von DRAM-Chips<br />

10000000<br />

1000000<br />

100000<br />

kB 10000<br />

1000<br />

100<br />

10<br />

1<br />

1977<br />

1980<br />

1983<br />

1985<br />

1989<br />

1992<br />

1995<br />

1998<br />

2001<br />

2003<br />

Jahr<br />

9

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Zugriffszeiten von DRAM´s<br />

ns<br />

250<br />

200<br />

150<br />

100<br />

50<br />

0<br />

64kB 256kB 1MB 4MB 16MB 64MB<br />

10

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Während die <strong>Speicher</strong>kapazität seit langer Zeit exponentiell<br />

anwächst (Faktor 4 in drei Jahren), verringert sich die<br />

Zugriffszeit nur langsam (Reduktion um ein Drittel in 10<br />

Jahren)<br />

� damit wird die Lücke zwischen Prozessorgeschwindigkeit<br />

und <strong>Speicher</strong>geschwindigkeit immer größer<br />

� daher: Einführung einer <strong>Speicher</strong>hierarchie<br />

11

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� <strong>Speicher</strong>hierarchie in einem Rechner<br />

r[0]<br />

...<br />

r[31]<br />

Register<br />

des Prozessors<br />

Cache<br />

Hauptspeicher<br />

32*32 Bit 256 kB 512 MB<br />

SRAM SRAM DRAM<br />

1 ns 5ns 20ns<br />

Plattenspeicher<br />

60 GB<br />

10 ms<br />

12

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Prinzip der Lokalität:<br />

� zeitlich: benutzte Daten/Befehle werden bald wieder<br />

benutzt<br />

� räumlich: auf Daten/Befehle, die im Adreßraum nahe<br />

zu gerade benutzten liegen, wird wahrscheinlicher<br />

verwiesen als auf weiter weg liegende<br />

13

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>1 <strong>Speicher</strong>hierarchie<br />

� Idee: räumlich nahe beieinanderliegende und oft<br />

referenzierte Teile (Blöcke) werden möglichst "nahe" am<br />

Prozessor gehalten<br />

Registersatz<br />

Cache<br />

1. Ebene<br />

Cache<br />

2. Ebene<br />

Hauptspeicher<br />

14

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Prinzip: nur die jeweils tatsächlich benötigten Blöcke<br />

werden im Cache gehalten<br />

Prozessor<br />

Cache<br />

Block<br />

Hauptspeicher<br />

15

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Daten werden bei der Organisation von Caches meist in<br />

Blöcken (oder Cache-Zeilen) zusammengefaßt<br />

� Blöcke bestehen aus Daten an aufeinanderfolgenden<br />

Adressen<br />

─ Beispiel: ein Block besteht aus 32 oder 64<br />

aufeinanderfolgender Bytes<br />

� es werden jeweils ganze Blöcke ausgetauscht<br />

Prozessor Cache<br />

Block<br />

Hauptspeicher<br />

16

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Für die Cache-Organisation sind 4 Fragen entscheidend:<br />

� A: wo kann ein Block im Cache plaziert werden?<br />

� B: wie kann festgestellt werden, ob ein Block im<br />

Cache ist?<br />

� C: welcher Block soll ersetzt werden, falls Platz<br />

für einen neuen Block gebraucht wird?<br />

� D: was geschieht beim Schreiben?<br />

Prozessor Cache<br />

Block<br />

Hauptspeicher<br />

17

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� A: wo kann ein Block plaziert werden ?<br />

� 1. Verfahren: voll-assoziativ<br />

� jeder Block kann an allen Adressen gespeichert<br />

werden<br />

Cache<br />

0<br />

1<br />

2<br />

3<br />

Hauptspeicher<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

18

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� 2. Verfahren: direkt abbildend<br />

� ein Block kann nur an einer Adresse mod n (n<br />

Cache-Größe, hier: 4) gespeichert werden<br />

Cache<br />

0<br />

1<br />

2<br />

3<br />

Hauptspeicher<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

19

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� mehrere Hauptspeicherblöcke mit gleicher Adresse<br />

mod n werden einem einzigen Block im Cache<br />

zugeordnet<br />

Cache<br />

0<br />

1<br />

2<br />

3<br />

Hauptspeicher<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

20

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� 3. Verfahren: n-Wege assoziativ<br />

� ein Block kann an jeder der n Cache-Adressen<br />

gespeichert werden, bei denen die Hauptspeicher-<br />

Adresse mod m gleich der Cache-Adresse mod m ist<br />

� physikalischer Aufbau von n unabhängigen Caches<br />

� Beispiel: 2-Wege assoziativ, m = 4:<br />

0<br />

1<br />

2<br />

3<br />

0<br />

1<br />

2<br />

3<br />

Cache<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

Hauptspeicher<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

21

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� B: wie kann festgestellt werden, ob ein Block im Cache<br />

ist ?<br />

� Verfahren bei direkt abbildendem Cache<br />

� Annahme: pro Block im Cache werden k Worte<br />

gespeichert, z.B. 4 Worte zu je 8 Byte<br />

� Offset ist die Adresse innerhalb eines Blocks, z.B. 2<br />

Bits bei 4 Worten pro Block<br />

� Index gibt die Adresse im Cache an<br />

Tag 19 Bit<br />

Block-Adresse<br />

Tag Index<br />

Cache-Adresse, z.B. 8 Bit<br />

Hauptspeicher-Adresse 32 Bit<br />

2Bit<br />

Offset<br />

3Bit<br />

Byteadresse<br />

innerhalb<br />

eines<br />

Wortes<br />

22

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

Hauptspeicher-Adresse 29 Bit<br />

Block-Adresse<br />

Tag Index<br />

Tag 19 Bit<br />

=<br />

Cache-Adresse 8 Bit<br />

Offset<br />

Offset 2 Bit<br />

0<br />

...<br />

255<br />

Valid-<br />

Bit<br />

1<br />

=1<br />

256 * (8*4) Byte = 8 kByte<br />

direkt abbildender Cache<br />

Tag Datenblock<br />

19<br />

4 Worte zu 8 Bytes<br />

Tag 4*8 Bytes<br />

8 Byte Daten<br />

23

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Beispiel: Blockgröße = 1<br />

1101<br />

11 01<br />

Tag Index<br />

�<br />

=<br />

1<br />

Cache<br />

11 y<br />

00<br />

01<br />

10<br />

11<br />

x<br />

y<br />

0000<br />

0001<br />

0010<br />

0011<br />

0100<br />

0101<br />

0110<br />

0111<br />

1000<br />

1001<br />

1010<br />

1011<br />

1100<br />

1101<br />

1110<br />

1111<br />

Hauptspeicher<br />

24

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Beispiel: Blockgröße = 1<br />

1101<br />

11 01<br />

Tag Index<br />

�<br />

=<br />

1<br />

Cache<br />

10 x<br />

00<br />

01<br />

10<br />

11<br />

x<br />

y<br />

0000<br />

0001<br />

0010<br />

0011<br />

0100<br />

0101<br />

0110<br />

0111<br />

1000<br />

1001<br />

1010<br />

1011<br />

1100<br />

1101<br />

1110<br />

1111<br />

Hauptspeicher<br />

25

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Aufwand:<br />

─ <strong>Speicher</strong>platz im Cache für Daten, Tag´s, Valid-<br />

Bits<br />

─ 1 Vergleicher<br />

26

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Verfahren bei n-Wege assoziativem Cache:<br />

� Prinzip: n-maliger Aufbau der o.a. Hardware<br />

� Beispiel: 2-Wege assoziativer Cache, gleiche<br />

Cachegröße:<br />

27

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

Block-Adresse<br />

Tag Index<br />

Tag 20 Bit<br />

Hauptspeicher-Adresse 29 Bit<br />

Cache-Adresse 7 Bit<br />

Offset<br />

Offset 2 Bit<br />

Valid-<br />

Bit<br />

0<br />

...<br />

127<br />

0<br />

...<br />

127<br />

=1<br />

=1<br />

Tag<br />

20<br />

Tag 8 Bytes<br />

=<br />

Tag<br />

=<br />

28<br />

2*128 * (8*4) Byte = 8 kByte<br />

2-Wege assoziativer Cache<br />

Datenblock<br />

4 Worte zu 8 Bytes<br />

8 Bytes

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Beispiel: Blockgröße = 1<br />

1101<br />

110 1<br />

Tag Index<br />

1<br />

1<br />

Cache<br />

001 x<br />

=<br />

=<br />

�<br />

110 y<br />

�<br />

0<br />

1<br />

0<br />

1<br />

x<br />

y<br />

0000<br />

0001<br />

0010<br />

0011<br />

0100<br />

0101<br />

0110<br />

0111<br />

1000<br />

1001<br />

1010<br />

1011<br />

1100<br />

1101<br />

1110<br />

1111<br />

Hauptspeicher<br />

29

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Aufwand:<br />

─ <strong>Speicher</strong>platz im Cache für Daten, Tag´s, Valid-<br />

Bit<br />

─ n Vergleicher<br />

─ Multiplexoren bzw. Tri-State Treiber<br />

30

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� ein voll-assoziativer Cache benötigt spezielle<br />

Bausteine (CAM´s, content-addressable memory)<br />

31

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� C: welcher Block soll ersetzt werden, falls Platz für einen<br />

neuen Block gebraucht wird ?<br />

� direkt-abbildend: klar<br />

Cache<br />

0<br />

1<br />

2<br />

3<br />

Hauptspeicher<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

32

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� n-Wege assoziativ:<br />

─ LRU (least recently used): Versuch, die zuletzt<br />

benutzten Daten zu erhalten, z.B. PowerPC 603<br />

LRU bei 4-Wege teilass. Cache<br />

─ zufallsgesteuert<br />

─ experimentelles Ergebnis: LRU nur<br />

bei kleinen Cache´s (16kB) geringfügig<br />

(

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� D: was geschieht beim Schreiben ?<br />

� Daten in Cache und Hauptspeicher korrespondieren<br />

einander nur solange, wie der Prozessor nicht die<br />

Daten im Cache überschreibt<br />

11010101<br />

Cache<br />

Prozessor ≠<br />

Hauptspeicher<br />

00001111<br />

34

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� 2 Strategien:<br />

─ Schreiben in Cache und Hauptspeicher (writethrough)<br />

─ Schreiben nur in Cache, zurückschreiben in den<br />

Hauptspeicher nur bei Austausch des Blocks<br />

(write-back)<br />

11010101<br />

Cache<br />

Prozessor ≠<br />

Hauptspeicher<br />

00001111<br />

35

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Write-through: Beim Schreiben in Cache und<br />

Hauptspeicher muß wegen der Langsamkeit des<br />

Hauptspeichers ein Schreib-Puffer benutzt werden,<br />

d.h. zu schreibende Daten werden in Cache und<br />

Schreib-Puffer geschrieben<br />

Prozessor<br />

11010101<br />

11010101<br />

Cache<br />

Schreib-<br />

Puffer<br />

Hauptspeicher<br />

11010101<br />

36

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Falls ein Wort nicht im Cache ist (write miss), gibt es zwei<br />

Möglichkeiten:<br />

─ der gesamte Block wird erst aus dem Hauptspeicher in<br />

den Cache gelesen, dann wie oben (write allocate)<br />

─ die Daten werden nur in den Hauptspeicher<br />

zurückgeschrieben (write not allocate)<br />

Hauptspeicher<br />

Prozessor<br />

11010101<br />

11010101<br />

Cache<br />

Schreib-<br />

Puffer<br />

11010101<br />

37

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Aufbau des Schreib-Puffers:<br />

� Größe z.B. 4 Blöcke<br />

� FIFO (first-in-first-out) Organisation<br />

� Block-Organisation, d.h. sollen nacheinander 2 Bytes<br />

mit unterschiedlichen Adressen, die aber in einem<br />

Block liegen, weggeschrieben werden, wird nur ein<br />

Block des Schreibpuffers belegt<br />

38

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Wie oft kommt Schreiben überhaupt vor ?<br />

� bei DLX z.B. gab es 9% Store- und 26% Ladebefehle<br />

� d.h. 0,09/(0,26+0,09) oder etwa 26% aller<br />

Datentransporte sind Schreibzugriffe<br />

� bzw. 0,09/(1 + 0,26 + 0,09) oder etwa 7% aller<br />

<strong>Speicher</strong>zugriffe insgesamt<br />

� Die Anzahl der Schreibzugriffe muß wesentlich kleiner<br />

sein als 1/Hauptspeicher-Zugriffszeit<br />

39

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Lösungsmöglichkeit: Einführung eines Caches der<br />

2. Ebene<br />

Prozessor<br />

L1-<br />

Cache<br />

Schreib-<br />

Puffer<br />

L2-<br />

Cache<br />

Hauptspeicher<br />

40

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Beispiel SPARC 20<br />

� L1-Daten-Cache:<br />

─ 16 kByte, 4-Wege assoziativ, write through<br />

(Schreiben in Cache 1. und 2. Ebene), kein Lesen<br />

des gesamten Blocks bei Schreib-Fehlzugriff<br />

(write not allocate), 64 Byte Blöcke<br />

� L1-Befehls-Cache<br />

─ 20 kByte, 5-Wege assoziativ, 64 Byte Blöcke<br />

� L2-Cache (für Daten und Instruktionen)<br />

─ 1 MByte, direkt abbildend, Zurückschreiben bei<br />

Anforderung (write back), Lesen des gesamten<br />

Blocks bei Schreib-Fehlzugriff (write allocate),<br />

128 Byte Blöcke<br />

41

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Leistungsmaße für Caches<br />

� mittlere Zugriffszeit = Zugriffszeit + Fehlrate *<br />

Fehlzugriffszeit<br />

� Zugriffszeit z.B. 1, Fehlzugriffszeit z.B. 10<br />

� Beispiel: 4 kByte Datencache, Fehlrate 15,9%,<br />

Fehlzugriffszeit 10<br />

⇒ mittlere Zugriffszeit = 1 + 0,159*10 = 2,59<br />

42

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Fehlraten in Abhängigkeit von der Cache-Größe,<br />

direkt abbildender Cache<br />

%<br />

30<br />

25<br />

20<br />

15<br />

10<br />

5<br />

0<br />

Daten-<br />

Cache<br />

Daten/Befehls-<br />

Cache<br />

1kB 2kB 4kB 8kB 16kB 32kB 64kB 128kB<br />

Befehls-<br />

Cache<br />

43

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Wie geht dies in die Leistung ein ?<br />

� bisher:<br />

� jetzt:<br />

Ausführungszeit = IC * CPI * Taktdauer<br />

Ausführungszeit =<br />

<strong>Speicher</strong>zugriffe<br />

IC * (CPI +<br />

Instruktion<br />

*Fehlrate*Fehlzugriffszeit) *<br />

Taktdauer<br />

44

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Beispiel: 4 kByte gemeinsamer Daten/Befehls-Cache,<br />

Fehlrate 7,2%, Fehlzugriffszeit 10, CPI = 1,<br />

1,35 <strong>Speicher</strong>zugriffe pro Instruktion<br />

Ausführungszeit =<br />

<strong>Speicher</strong>zugriffe<br />

IC * (CPI +<br />

Instruktion<br />

*Fehlrate*Fehlzugriffszeit) *<br />

Taktdauer<br />

= IC * (1 + 1,35*0,072*10) * Taktdauer = IC * 1,97 * Taktdauer<br />

� d.h. nur noch die halbe Leistung<br />

� aber: ohne Cache ist die Ausführungszeit<br />

IC * (1 + 1,35*10) * Taktdauer, d.h. 14,5* so lange<br />

45

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Reduzierung der Fehlrate<br />

� Fehlzugriffe entstehen<br />

─ unvermeidlich zu Beginn !<br />

─ durch mangelnde Kapazität<br />

─ durch Konflikte<br />

� Maßnahmen gegen Fehlzugriffe:<br />

─ größere Blöcke<br />

─ n-Wege assoziativ: n vergrößern<br />

─ vorausschauendes Lesen von Befehlen/Daten<br />

(prefetch)<br />

46

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Fehlraten in Abhängigkeit von der Block-Größe<br />

und Cache-Größe<br />

Fehlrate<br />

%<br />

25<br />

20<br />

15<br />

10<br />

5<br />

0<br />

16 32 64 128 256<br />

Cache-Größe<br />

1kB<br />

4kB<br />

Block-Größe<br />

16kB<br />

64kB<br />

47

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Fehlraten in Abhängigkeit von der Cache-Größe<br />

und dem Assoziationsgrad<br />

Fehlrate<br />

%<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

direkt abbildend<br />

2-Wege<br />

4-Wege<br />

8-Wege<br />

1 2 4 8 16 32 64 128<br />

Cache-Größe (kB)<br />

48

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Reduzierung der Fehlzugriffszeit<br />

─ z.B. Cache 2. Ebene<br />

49

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Experiment: Einfluß der Caches auf verschiedene<br />

Algorithmen für die Multiplikation von n*n Matrizen<br />

� Algorithmus ijk:<br />

for (i=0; i

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Algorithmus ikj:<br />

for (i=0; i

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Algorithmus jki:<br />

for (j=0; j

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Blockweise Multiplikation:<br />

for (kk=0; kk

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

a 11<br />

a 21<br />

─ Idee:<br />

a 12<br />

a 22<br />

A 11<br />

A 21<br />

A 12<br />

A 22<br />

*<br />

B 11<br />

B 21<br />

B 12<br />

B 22<br />

=<br />

C 11<br />

C 21<br />

C 12<br />

C 22<br />

z.B. ist<br />

C 11 = A 11 B 11 + A 12 B 21 , C 12 = A 11 B 12 + A 12 B 22<br />

usw.<br />

*<br />

b 11<br />

b 21<br />

b 12<br />

b 22<br />

+<br />

a 13<br />

a 23<br />

a 14<br />

a 24<br />

*<br />

b 31<br />

b 41<br />

b 32<br />

b 42<br />

54

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>2 Cache-Organisation<br />

� Meßergebnisse:<br />

rel. Zeit<br />

0,4500<br />

0,4000<br />

0,3500<br />

0,3000<br />

0,2500<br />

0,2000<br />

0,1500<br />

0,1000<br />

0,0500<br />

0,0000<br />

10 25 50 100 150 200 300 400 600 800<br />

n<br />

Zeitijk/n**3<br />

Zeitikj/n**3<br />

Zeitjki/n**3<br />

Zeitbl/n**3<br />

55

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� RAM: random access memory, wahlfreier Zugriff,<br />

� die Zugriffszeit ist unabhängig vom Ort (Adresse) der<br />

<strong>Speicher</strong>ung<br />

� SRAM: statischer RAM<br />

� die Daten werden als Zustände von Flipflops<br />

gespeichert, d.h. über Rückkopplungen<br />

� CMOS/Bipolare Versionen<br />

� DRAM: dynamischer RAM<br />

� die Daten werden als Ladung von Kapazitäten<br />

gespeichert<br />

� Datenverlust, falls keine Auffrischung alle n ms<br />

� Integrationsdichte etwa 4 ...10*SRAM<br />

� z.B. 256 Mbit in Massenproduktion<br />

56

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Prinzipiell werden die einzelnen <strong>Speicher</strong>elemente eines<br />

<strong>Speicher</strong>s in einer Matrix angeordnet<br />

─ Beispiel: 1Mb <strong>Speicher</strong><br />

höchstwertige<br />

Bits<br />

Adressen<br />

20<br />

Zeilen-<br />

Adresse<br />

Spalten-<br />

Adresse<br />

Zeilendekodierer<br />

10<br />

10<br />

0<br />

...<br />

1023<br />

1<br />

1024 * 1024<br />

<strong>Speicher</strong>zellen<br />

0 ...<br />

1023<br />

Verstärker/<br />

Spaltendekodierer<br />

1<br />

adressierte<br />

Zeile<br />

57<br />

WE_L<br />

Lese/Schreibleitung

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Zeitlicher Ablauf:<br />

Dekodierung der<br />

Zeilenadresse<br />

Adressen<br />

20<br />

Verstärkung und<br />

Auslesen der<br />

ausgew. Zeile<br />

Zeilen-<br />

Adresse<br />

Spalten-<br />

Adresse<br />

Zeilendekodierer<br />

10<br />

10<br />

0<br />

...<br />

1023<br />

Dekodierung<br />

der<br />

Spaltenadresse<br />

1<br />

1024 * 1024<br />

<strong>Speicher</strong>zellen<br />

0 ...<br />

1023<br />

Verstärker/<br />

Spaltendekodierer<br />

1<br />

Ausgangsverstärkung<br />

t<br />

adressierte<br />

Zeile<br />

58<br />

WE_L<br />

Lese/Schreibleitung

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Aus Laufzeitgründen werden oft andere physikalische<br />

Aufteilungen gewählt, z.B.:<br />

512 * 1024<br />

<strong>Speicher</strong>zellen<br />

Schreib/Leseverstärker<br />

Zeilendekodierer<br />

...<br />

512 * 1024<br />

<strong>Speicher</strong>zellen<br />

Schreib/Leseverstärker<br />

Spaltendekodierer<br />

A0 A9<br />

10 Zeilenadressen<br />

Spaltendekodierer<br />

adressierte<br />

Zeile<br />

59

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� SRAM-<strong>Speicher</strong>zelle, Prinzip<br />

Zeilenauswahlleitung<br />

1<br />

0 1<br />

q q<br />

60

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Lesevorgang<br />

Zeilenauswahlleitung<br />

1<br />

bei <strong>Speicher</strong>n lange<br />

Leitungen, daher<br />

Differenzverstärker<br />

am Ausgang q<br />

notwendig<br />

Leitungen<br />

auf 1 vorgeladen<br />

0 1<br />

q<br />

61

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Schreibvorgang<br />

Zeilenauswahlleitung<br />

1<br />

0 1<br />

1 q<br />

q 0<br />

62

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Zeitverhältnisse beim Lesevorgang<br />

WE_L<br />

Adressen<br />

D<br />

Zykluszeit<br />

Zugriffszeit<br />

ungültige<br />

Daten<br />

t h<br />

gültige<br />

Daten<br />

63

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Zeitverhältnisse beim Schreibvorgang<br />

Adressen<br />

WE_L<br />

D<br />

Zykluszeit<br />

t suWE<br />

t suD<br />

t hWE<br />

t hD<br />

64<br />

Daten müssen stabil<br />

am Eingang anliegen

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Fazit:<br />

� der <strong>Speicher</strong> arbeitet während des Lesevorgangs wie<br />

ein Verknüpfungsnetz<br />

� die Schreibleitung WE_L entspricht der Taktleitung<br />

65

66<br />

<strong>7.</strong> <strong>Speicher</strong><br />

ALU<br />

Daten-<br />

speicher<br />

32*32<br />

Register-<br />

satz rf<br />

a<br />

b<br />

MPX<br />

ar<br />

di<br />

do<br />

MPX<br />

temp<br />

pc<br />

Befehls-<br />

speicher<br />

ir<br />

rs1<br />

rs2<br />

rd<br />

MPX<br />

∑<br />

temp1<br />

ir1<br />

ir2<br />

ir3<br />

rd<br />

rs1<br />

rs2<br />

MPX<br />

temp<br />

temp1<br />

di<br />

di<br />

MPX<br />

temp<br />

temp1<br />

di<br />

rfa<br />

alu<br />

+4<br />

temp<br />

temp1<br />

imm<br />

<strong>7.</strong>3 SRAM

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Lesevorgang in einer getakteten Umgebung:<br />

Takt<br />

Ausgang ar<br />

Ausgang D<br />

Datenspeicher<br />

Ausgang di<br />

n<br />

ar<br />

0<br />

Datenspeicher(n)<br />

Datenspeicher<br />

D<br />

di<br />

67

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Wide-Bus SRAM's<br />

� dieselbe <strong>Speicher</strong>kapazität läßt sich für<br />

<strong>Speicher</strong>bausteine unterschiedlicher Busbreiten<br />

einsetzen<br />

─ Beispiel: 1 MBit SRAM <strong>Speicher</strong><br />

256K * 4 Bit: 4 Pins Daten-Ein/Ausgänge, 18 Pins<br />

Adressleitungen = 22 Pins,<br />

64K * 16 Bit: 16 Pins Daten-Ein/Ausgänge, 16<br />

Adressleitungen = 32 Pins<br />

Adress-<br />

Bus<br />

18<br />

Daten-<br />

Bus<br />

4<br />

<strong>Speicher</strong>-<br />

Baustein<br />

Adress-<br />

Bus<br />

16<br />

Daten-<br />

Bus<br />

16<br />

<strong>Speicher</strong>-<br />

Baustein<br />

68

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� 64K * 16 Bit Wide-Bus SRAM<br />

Adressen<br />

16<br />

Zeilen-<br />

Adresse<br />

Spalten-<br />

Adresse<br />

Zeilendekodierer<br />

8<br />

8<br />

0<br />

...<br />

255<br />

1<br />

1024 * 1024<br />

<strong>Speicher</strong>zellen<br />

1024 256 * 1024 256<br />

<strong>Speicher</strong>zellen<br />

0 ...<br />

255<br />

Verstärker/<br />

Spaltendekodierer<br />

1<br />

16<br />

16<br />

1<br />

255<br />

adressierte<br />

Zeilen<br />

69<br />

WE_L<br />

Lese/Schreibleitung

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� <strong>Speicher</strong>arten<br />

� asynchrone <strong>Speicher</strong> (s.o.)<br />

� synchrone <strong>Speicher</strong><br />

� heute überwiegend synchrone <strong>Speicher</strong><br />

� keine Übermittlung zeitlich komplexer Signale<br />

wie z.B. WE_L<br />

� Möglichkeit der Zugriffsbeschleunigung durch<br />

Pipelining usw.<br />

70

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Synchrone SRAM-Bausteine<br />

� <strong>Speicher</strong>ung der Adressen und der Daten in Registern<br />

Adressen<br />

20<br />

AR-Register<br />

Zeilen-<br />

Adresse<br />

Spalten-<br />

Adresse<br />

Zeilendekodierer<br />

10<br />

10<br />

0<br />

...<br />

1023<br />

DI-Register<br />

1<br />

1024 * 1024<br />

<strong>Speicher</strong>zellen<br />

0 ...<br />

1023<br />

Verstärker/<br />

Spaltendekodierer<br />

1<br />

DO-Register<br />

71<br />

Bus

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Versionen von synchronen SRAM-Bausteinen<br />

� Version mit gepuffertem Pipeline-Register am<br />

Ausgang (Latenzzeit: 2 Takte)<br />

� flow-through Version mit ungepuffertem Register am<br />

Ausgang, d.h. die Daten müssen vor der nächsten<br />

Taktflanke stabil sein (Latenzzeit: 1 Takt)<br />

72

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Zeitlicher Ablauf beim Lesevorgang (mit Pipeline-<br />

Register am Ausgang):<br />

Takt<br />

Adressen<br />

Datenbus<br />

n<br />

Prozessor<br />

m o<br />

n<br />

Adressen<br />

Datenbus<br />

m<br />

Synchroner<br />

SRAM<br />

DO<br />

AR<br />

…<br />

o<br />

…<br />

73

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� In vielen Fällen muß eine Folge von Daten an aufeinanderfolgenden<br />

Adressen, ein Burst, gelesen oder geschrieben<br />

werden<br />

� insbesondere beim Laden eines Blocks (einer cacheline)<br />

in oder aus Caches muß ein Burst transportiert<br />

werden, z.B. vier mal 64 Bit an aufeinanderfolgenden<br />

Adressen<br />

� da bei jedem <strong>Speicher</strong>zugriff eine ganze Zeile ausgelesen<br />

wird, ist die Datenrate am Zeilenverstärker sehr viel höher<br />

als am Ausgang<br />

� die ausgelesene Zeile wirkt wie ein Cache<br />

� durch Ändern alleine der Spaltenadresse können<br />

weitere Daten aus einer bereits dekodierten Zeile oder<br />

auch die gesamte Zeile (page-mode) ausgelesen werden<br />

� Erweiterung des Adressregisters um einen Burst-<br />

Counter<br />

74

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

─ Auslesen einer kompletten Zeile:<br />

Adressen<br />

20<br />

Zeilen-<br />

Adresse<br />

Spalten-<br />

Adresse<br />

Zeilendekodierer<br />

10<br />

10<br />

0<br />

...<br />

1023<br />

1<br />

1024 * 1024<br />

<strong>Speicher</strong>zellen<br />

0 ...<br />

1023<br />

Verstärker/<br />

Spaltendekodierer<br />

1<br />

adressierte<br />

Zeile<br />

75<br />

WE_L<br />

Lese/Schreibleitung<br />

1024 Bit<br />

verfügbar !

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Synchroner SRAM mit Burst-Unterstützung durch Burst-<br />

Counter BC<br />

Adressen<br />

20<br />

18<br />

AR-Reg.<br />

BC<br />

Zeilen-<br />

Adresse<br />

8<br />

2 2<br />

Zeilendekodierer<br />

10<br />

0<br />

...<br />

1023<br />

DI-Register<br />

1024 * 1024<br />

<strong>Speicher</strong>zellen<br />

0 ...<br />

1023<br />

Verstärker/<br />

Spaltendekodierer<br />

10<br />

Spalten-<br />

1<br />

Adresse<br />

1<br />

DO-Register<br />

76<br />

Bus

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Registersatz, z.B. 32*32 Bit<br />

Zeilen-<br />

(Wort-)<br />

dekodierer<br />

A0 ... A4<br />

5 Wortadressen<br />

0<br />

31<br />

...<br />

...<br />

D0<br />

Schreibverstärker<br />

...<br />

0 31<br />

...<br />

0 31<br />

D0<br />

32 Worte zu 32 Bit<br />

Leseverstärker<br />

...<br />

D31<br />

D31<br />

77

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� Ein Registerinhalt = 32 Bit wird parallel ausgelesen<br />

� in Rechnerkernen ist oft das unabhängige Lesen von<br />

zwei Registern parallel zum Schreiben in ein drittes<br />

Register erlaubt (vgl. DLX), d.h. es sind drei<br />

Adressdekodierer nötig<br />

� wegen der geringen Größe sind an den Leseausgängen<br />

keine Differenzverstärker notwendig<br />

78

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>3 SRAM<br />

� <strong>Speicher</strong>zelle hierfür:<br />

Schreibauswahlleitung<br />

r3<br />

Leseauswahlleitung<br />

r1<br />

Leseauswahlleitung<br />

r2<br />

d<br />

q1 q2<br />

d<br />

79

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� SRAM-Zelle: 6-4 Transistoren<br />

� DRAM-Zelle: 1 Transistor<br />

Spaltenauswahl<br />

Zeilenauswahl<br />

80

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Größenvergleich zwischen SRAM und DRAM tatsächlich<br />

noch drastischer als 6:1<br />

� Beispiel Infineon 0,20 μm Technologie<br />

─ SRAM 10-11 μm2 ─ DRAM 1-0,7 μm 2<br />

� "embedded DRAM"<br />

81

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Lesen:<br />

� Spaltenauswahl-Leitung vorladen (precharge)<br />

� Zeilenauswahl auf 1 setzen<br />

� bei gespeicherter 0 sehr kleine Ladungsänderung<br />

auf der Spaltenauswahl-Leitung<br />

� Verstärkung dieser Änderung<br />

� Zurückschreiben des gelesenen Resultats !<br />

Zeilenauswahl<br />

Spaltenauswahl<br />

82

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Schreiben:<br />

� Wert auf Spaltenauswahl-Leitung legen<br />

� Zeilenauswahl auf 1 setzen<br />

Spaltenauswahl<br />

Zeilenauswahl<br />

83

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Auffrischen:<br />

� lesen (und zurückschreiben) jeder Zelle<br />

� geht zeilenweise in einem Schritt<br />

� für Refresh gehen typischerweise 1-2% aller<br />

Zyklen verloren<br />

Zeilenauswahl<br />

Spaltenauswahl<br />

84

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Zur Einsparung von Anschlüssen für die Adressen<br />

werden die Zeilen- und Spaltenadressen von DRAM-<br />

Bausteinen gemultiplext und im <strong>Speicher</strong>chip in<br />

Registern zwischengespeichert<br />

� Signale RAS_L (row-address select) bzw. CAS_L<br />

(column-address select)<br />

85

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Lesevorgang:<br />

RAS_L<br />

CAS_L<br />

WE_L<br />

Adressen<br />

D<br />

Zykluszeit<br />

Z.Adr. Sp.Adr. Z.Adr. Sp.Adr.<br />

t r<br />

gültige<br />

Daten<br />

precharge Zeit<br />

86

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� die Zugriffszeit t r ist wesentlich kleiner als<br />

die Zykluszeit<br />

87

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Schreibvorgang:<br />

RAS_L<br />

CAS_L<br />

WE_L<br />

Adressen<br />

D<br />

Zykluszeit<br />

Z.Adr. Sp.Adr. Z.Adr. Sp.Adr.<br />

gültige<br />

Daten<br />

88

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Die Techniken der Zugriffsbeschleunigung sind<br />

prinzipiell ähnlich denen von SRAM-Bausteinen<br />

� überwiegend synchrone Bausteine<br />

� Unterstützung von Bursts und Pipelining<br />

� mehrere <strong>Speicher</strong>bänke mit jeweils eigenem<br />

Zeilendekodierer<br />

─ Maskierung der Precharge-Zeit<br />

─ Vervielfachung der "offenen" Zeilen-Caches<br />

� ...<br />

89

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Synchroner DRAM mit Burst-Unterstützung durch Burst-<br />

Counter BC<br />

Adressanschlüsse<br />

10<br />

10<br />

RAS<br />

8<br />

RA-Reg.<br />

CA-Reg.<br />

CAS<br />

BC<br />

Zeilen-<br />

Adresse<br />

2 2<br />

CAS<br />

8<br />

10<br />

Zeilendekodierer<br />

0<br />

...<br />

1023<br />

DI-Register<br />

1024 * 1024<br />

<strong>Speicher</strong>zellen<br />

0 ...<br />

1023<br />

Verstärker/<br />

Spaltendekodierer<br />

10<br />

Spalten-<br />

1<br />

Adresse<br />

1<br />

DO-Register<br />

90<br />

Bus

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

Takt<br />

Adressanschlüsse<br />

Datenbus<br />

� Zeitlicher Ablauf beim Lesevorgang (Burst mit<br />

Pipelining):<br />

Laden der<br />

Zeilenadresse<br />

r<br />

Laden der<br />

Spaltenadresse<br />

n<br />

CAS-<br />

Latenzzeit<br />

m<br />

n n+1 n+2 n+3 m m+1<br />

Burst<br />

91<br />

Laden einer<br />

anderen<br />

Spaltenadresse<br />

derselben Zeile

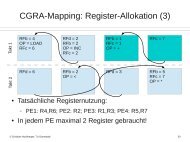

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

Takt<br />

Adressanschlüsse<br />

Datenbus<br />

� Zeitlicher Ablauf beim Lesevorgang (Burst mit<br />

Pipelining, wechseln der Zeile):<br />

Laden der<br />

Zeilenadresse<br />

r<br />

Laden der<br />

Spaltenadresse<br />

n<br />

CAS-<br />

Latenzzeit<br />

n n+1 n+2 n+3<br />

Burst<br />

Precharge-Zeit<br />

zum Rückschreiben<br />

des Zeileninhalts<br />

s<br />

Laden einer<br />

neuen<br />

Zeilenadresse<br />

92

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� DDR SDRAM<br />

� Doppelte Datenrate durch<br />

─ Auslesen eines doppelt breiten Datenvektors mit<br />

jeder Spaltenadresse in jedem Takt<br />

─ Durchschalten der beiden Hälften mit der<br />

abfallenden und ansteigenden Taktflanke<br />

93

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Prinzipieller Aufbau:<br />

16.384*<br />

2.048*8<br />

8<br />

8<br />

8<br />

4<br />

4<br />

4<br />

94<br />

Quelle: JEDEC STANDARD Double Data Rate (DDR)<br />

SDRAM Specification JESD79D

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Zeitliches Verhalten:<br />

95<br />

Quelle: JEDEC STANDARD Double Data Rate (DDR)<br />

SDRAM Specification JESD79D

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>4 DRAM<br />

� Nicht-optimierte vs. durch Burst usw. optimierte<br />

Zyklusszeiten von DRAM´s<br />

ns<br />

250<br />

200<br />

150<br />

100<br />

50<br />

0<br />

64kB<br />

256kB<br />

1MB<br />

4MB<br />

16MB<br />

64MB<br />

optimiert<br />

96

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

� RAM: flüchtiger <strong>Speicher</strong><br />

� ROM:<br />

� fest maskenprogrammiert durch den Hersteller<br />

� nicht veränderbar<br />

� sicher gegen Manipulation<br />

� höchste Integrationsdichte<br />

� sinnvoll > 10.000 Stück<br />

97

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

� EPROM:<br />

� programmierbar durch Hersteller/Benutzer<br />

� flexibel bezgl. Stückzahl<br />

� schnell programmierbar (typ. 100 μs)<br />

� OTP-(one time programmable)-Versionen oder<br />

komplett durch Bestrahlen mit UV-Licht löschbare<br />

Versionen<br />

98

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

99

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

� EEPROM's/Flash:<br />

� ideal für field upgrades (Bootsoftware, BIOS, Firmware)<br />

und zum <strong>Speicher</strong>n individueller Kenndaten (IP Adresse)<br />

� ermöglicht inkrementelle Produkte durch Hinzufügen<br />

neuer oder weiterer Firmware-Versionen<br />

� "digitaler Film" in der Digitalkamera bzw. "digitales<br />

Band" im MP3-Spieler<br />

� unsicher gegenüber Manipulationen<br />

� Feldprogrammierbarkeit schwierig, z.B. sicher gegen<br />

Unterbrechung der Programmierung, usw.<br />

� Flash organisiert in Blöcken, die jeweils für sich als<br />

Ganzes gelöscht/beschrieben werden<br />

� vergleichsweise langsam zu programmieren (typ. 10 ms)<br />

� Größen z.B. 32 MB - 4 GB, Zugriffszeit ~ 50 ns<br />

100

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

� Programmierung:<br />

� MOS-Transistor mit sog. "floating gate"<br />

� im Programmierbetrieb wird durch Anlegen einer<br />

Spannung > Betriebsspannung eine Ladung<br />

(5.000 < bzw. < 30.000 Elektronen !) auf das floating<br />

gate gebracht<br />

� diese Ladung hebt die Schwellspannung des<br />

Transistors so an, daß Änderungen am Gate bei<br />

normaler Betriebsspannung keine Auswirkungen<br />

haben und der Transistor dauernd gesperrt ist<br />

101

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

─ Beispiel: Intel StrataFlash <strong>Speicher</strong><br />

Technologie, speichern von 2 Bit pro Zelle<br />

102

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>5 <strong>Speicher</strong>arten<br />

� Flash-Varianten:<br />

� NOR (Intel 1988)<br />

─ ~ SRAM, d.h. wahlfreier Zugriff<br />

─ hoher Platzbedarf<br />

─ sehr langsames Schreiben/Löschen<br />

─ Code-<strong>Speicher</strong>ung und Ausführung möglich<br />

� NAND (Toshiba 1989)<br />

─ sequentieller Datenzugriff, d.h. auch der<br />

Lesezugriff ist nur in einer vorgegebenen<br />

Ordnung möglich<br />

─ blockweise Übertragung, z.B. Blöcke von 512<br />

Bytes<br />

─ Benutzung in USB-Sticks, SD-Karten usw. für<br />

große Datenmengen<br />

103

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>6 Plattenspeicher<br />

� Festplatten<br />

� Ferro-magnetische <strong>Speicher</strong>ung von Daten<br />

� 1-12 beidseitig beschichtete, gemeinsam<br />

rotierende Platten<br />

� Durchmesser 3,5", 2,5", 1"<br />

� Rotationsgeschwindigkeit 4.000 –<br />

10.000 U/min.<br />

� Kapazität 1 – 400 GB<br />

Cache<br />

Hauptspeicher<br />

Festplatte<br />

104

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>6 Plattenspeicher<br />

� Aufteilung:<br />

� 5.000 bis 30.000 Spuren (tracks) pro Plattenoberfläche<br />

� Spuren an derselben Position auf mehreren<br />

Oberflächen bilden einen Zylinder<br />

� Unterteilung einer Spur in 150 … 500 Sektoren zu<br />

typischerweise 512 Bytes<br />

� Lesen und Schreiben durch Lese/Schreibköpfe, die<br />

einen Zylinder auslesen<br />

…<br />

105<br />

Seagate ST1 1" 4-8GB Festplatte<br />

42.8 x 36.4 x 5 mm, 19 g

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>6 Plattenspeicher<br />

� Zugriffszeiten (Beispiel)<br />

� Typische mittlere Zylinder-Zugriffszeit der Köpfe 5–12<br />

ms<br />

� Rotationszeit 1/10.0000 U/min. = 6 ms<br />

� mittlere Verzögerung durch Rotation ~ 50%*1/10.0000<br />

U/min. = 3 ms<br />

� Annahmen: 360 Sektoren/Spur, Sektoren von 512<br />

Bytes, Rotationszeit = 6ms ⇒ Auslesegeschwindigkeit<br />

30 MB/sec. ⇒ Lesezeit/Sektor = 0,5 KB/30 MB/sec. ~<br />

0,017 ms<br />

…<br />

106

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>6 Plattenspeicher<br />

� Wegen der im Vergleich zur Zeit für die Positionierung der<br />

Köpfe sehr kleinen Lesezeit pro Sektor (wenige Promille<br />

der gesamtzeit) werden typischerweise räumlich<br />

naheliegende Sektoren vorausschauend ebenfalls<br />

ausgelesen und ein einem einige MB großen Puffer<br />

gehalten<br />

107

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>7 DMA<br />

� DMA: direct memory access<br />

� in einfachen Systemen geschah der Datenaustausch<br />

zwischen <strong>Speicher</strong> und E/A-Gerät unter Prozessorkontrolle,<br />

d.h. durch ein Programm, das Daten vom Puffer der<br />

Geräteschnittstelle in den <strong>Speicher</strong> schrieb<br />

Prozessor <strong>Speicher</strong><br />

Bus<br />

bewirkt durch z.B.<br />

MOVE-Befehle<br />

E/A-<br />

Puffer<br />

E/A-<br />

Puffer<br />

108

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>7 DMA<br />

� Bei DMA werden Daten zwischen <strong>Speicher</strong> und<br />

Ein/Ausgabegerät unter Kontrolle eines DMA-Controllers<br />

ausgetauscht<br />

� die CPU kann parallel dazu Programme ausführen<br />

� die Buszugriffe müssen sich Prozessor und DMA-<br />

Controller teilen ("cycle stealing")<br />

Arbiter<br />

Prozessor <strong>Speicher</strong><br />

Bus<br />

Transport durch<br />

DMA-Controller<br />

DMA-<br />

Controller<br />

E/A-<br />

Puffer<br />

109

<strong>7.</strong> <strong>Speicher</strong><br />

<strong>7.</strong>7 DMA<br />

� Üblicherweise teilt der Prozessor dem DMA-Controller<br />

Anfangsadresse und Umfang der zu transportierenden<br />

Daten mit, das Inkrementieren der Adresse usw.<br />

übernimmt der DMA-Controller<br />

110

<strong>7.</strong> <strong>Speicher</strong><br />

� Literatur für dieses Kapitel (außer Hen/Pat):<br />

� B. Prince: High Performance Memories, John Wiley<br />

1999<br />

� T. P. Haraszti: CMOS Memory Circuits, Kluwer 2000<br />

111