PAL, CPLD, FPGA etc. - Lehrstuhl für Schaltungstechnik und ...

PAL, CPLD, FPGA etc. - Lehrstuhl für Schaltungstechnik und ...

PAL, CPLD, FPGA etc. - Lehrstuhl für Schaltungstechnik und ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

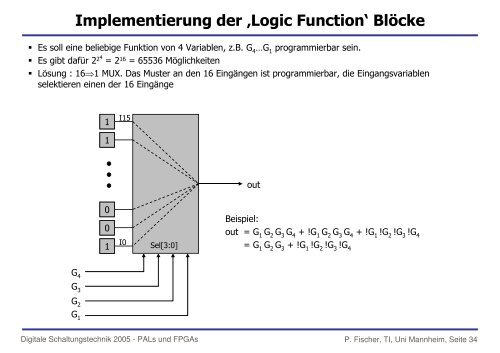

Implementierung der ‚Logic Function‘ Blöcke Es soll eine beliebige Funktion von 4 Variablen, z.B. G 4…G 1programmierbar sein. Es gibt dafür 2 24 = 2 16 = 65536 Möglichkeiten Lösung : 16⇒1 MUX. Das Muster an den 16 Eingängen ist programmierbar, die Eingangsvariablenselektieren einen der 16 Eingänge1I151out001I0Sel[3:0]Beispiel:out = G 1G 2G 3G 4+ !G 1G 2G 3G 4+ !G 1!G 2!G 3!G 4= G 1G 2G 3+ !G 1!G 2!G 3!G 4G 4G 3G 2G 1Digitale <strong>Schaltungstechnik</strong> 2005 - <strong>PAL</strong>s <strong>und</strong> <strong>FPGA</strong>sP. Fischer, TI, Uni Mannheim, Seite 34