COMPUTER ARCHITECTURE AND ORGANIZATION: An ... - IIUSA

COMPUTER ARCHITECTURE AND ORGANIZATION: An ... - IIUSA

COMPUTER ARCHITECTURE AND ORGANIZATION: An ... - IIUSA

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

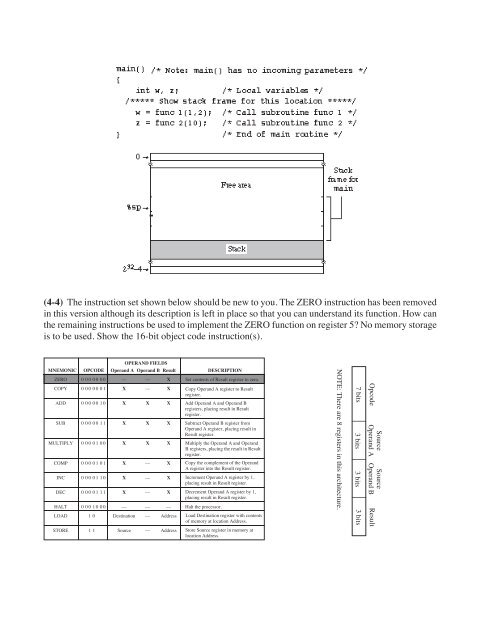

(4-4) The instruction set shown below should be new to you. The ZERO instruction has been removed<br />

in this version although its description is left in place so that you can understand its function. How can<br />

the remaining instructions be used to implement the ZERO function on register 5? No memory storage<br />

is to be used. Show the 16-bit object code instruction(s).<br />

MNEMONIC OPCODE<br />

OPER<strong>AND</strong> FIELDS<br />

Operand A Operand B Result<br />

DESCRIPTION<br />

ZERO 0000000 –– –– X Set contents of Result register to zero.<br />

COPY<br />

ADD<br />

SUB<br />

MULTIPLY<br />

COMP<br />

INC<br />

DEC<br />

HALT<br />

LOAD<br />

0000001 X –– X Copy Operand A register to Result<br />

register.<br />

0000010 X X X<br />

0000011 X X X<br />

0000100 X X X<br />

0000101 X –– X<br />

0000110 X –– X<br />

0000111 X –– X<br />

0001000 –– –– –– Halt the processor.<br />

Add Operand A and Operand B<br />

registers, placing result in Result<br />

register.<br />

Subtract Operand B register from<br />

Operand A register, placing result in<br />

Result register.<br />

Multiply the Operand A and Operand<br />

B registers, placing the result in Result<br />

register.<br />

Copy the complement of the Operand<br />

A register into the Result register.<br />

Increment Operand A register by 1,<br />

placing result in Result register.<br />

Decrement Operand A register by 1,<br />

placing result in Result register.<br />

10 Destination –– Address Load Destination register with contents<br />

of memory at location Address.<br />

STORE 11 Source –– Address Store Source register in memory at<br />

location Address.<br />

NOTE: There are 8 registers in this architecture.<br />

Source Source<br />

Opcode Operand A Operand B Result<br />

7 bits 3 bits 3 bits 3 bits