annel Length and External Series Resistance Models of Scaled LDD ...

annel Length and External Series Resistance Models of Scaled LDD ...

annel Length and External Series Resistance Models of Scaled LDD ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

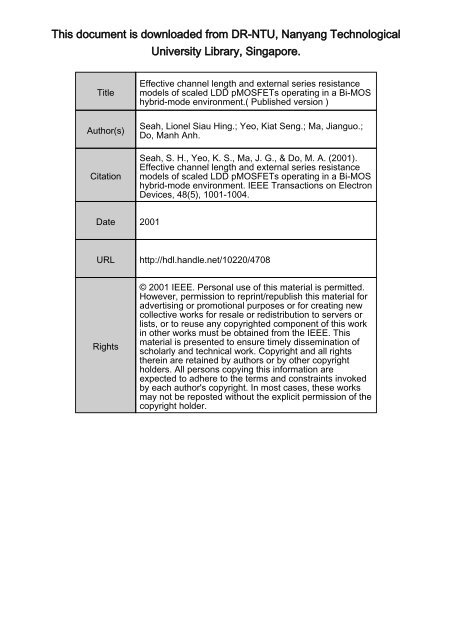

This document is downloaded from DR-NTU, Nanyang Technological<br />

University Library, Singapore.<br />

Title<br />

Author(s)<br />

Citation<br />

Effective ch<strong>annel</strong> length <strong>and</strong> external series resistance<br />

models <strong>of</strong> scaled <strong>LDD</strong> pMOSFETs operating in a Bi-MOS<br />

hybrid-mode environment.( Published version )<br />

Seah, Lionel Siau Hing.; Yeo, Kiat Seng.; Ma, Jianguo.;<br />

Do, Manh Anh.<br />

Seah, S. H., Yeo, K. S., Ma, J. G., & Do, M. A. (2001).<br />

Effective ch<strong>annel</strong> length <strong>and</strong> external series resistance<br />

models <strong>of</strong> scaled <strong>LDD</strong> pMOSFETs operating in a Bi-MOS<br />

hybrid-mode environment. IEEE Transactions on Electron<br />

Devices, 48(5), 1001-1004.<br />

Date 2001<br />

URL<br />

http://hdl.h<strong>and</strong>le.net/10220/4708<br />

Rights<br />

© 2001 IEEE. Personal use <strong>of</strong> this material is permitted.<br />

However, permission to reprint/republish this material for<br />

advertising or promotional purposes or for creating new<br />

collective works for resale or redistribution to servers or<br />

lists, or to reuse any copyrighted component <strong>of</strong> this work<br />

in other works must be obtained from the IEEE. This<br />

material is presented to ensure timely dissemination <strong>of</strong><br />

scholarly <strong>and</strong> technical work. Copyright <strong>and</strong> all rights<br />

therein are retained by authors or by other copyright<br />

holders. All persons copying this information are<br />

expected to adhere to the terms <strong>and</strong> constraints invoked<br />

by each author's copyright. In most cases, these works<br />

may not be reposted without the explicit permission <strong>of</strong> the<br />

copyright holder.

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 48, NO. 5, MAY 2001 1001<br />

reduction can be utilized to improve the low-frequency noise performance<br />

<strong>of</strong> analog circuits implemented in triple-well CMOS technologies<br />

[15]–[17].<br />

ACKNOWLEDGMENT<br />

The authors are grateful to Dr. G. Bosman for valuable comments<br />

<strong>and</strong> suggestions.<br />

REFERENCES<br />

[1] F. N. Hooge, “1/f noise,” Physica, vol. 83B, pp. 14–23, 1976.<br />

[2] L. K. J. V<strong>and</strong>amme, “Model for 1/f noise in MOS transistors biased in<br />

the linear region,” Solid-State Electron., vol. 23, pp. 317–323, 1980.<br />

[3] A. L. McWhorter, Semiconductor Surface Physics. Philadelphia, PA:<br />

Univ. <strong>of</strong> Pennsylvania Press, 1957, pp. 207–228.<br />

[4] S. Christensson, I. Lundstrom, <strong>and</strong> C. Svensson, “Low frequency noise<br />

in MOS transistors—I (Theory),” Solid-State Electron., vol. 11, pp.<br />

797–812, 1968.<br />

[5] , “Low frequency noise in MOS transistors—II (Experiment),”<br />

Solid-State Electron., vol. 11, pp. 813–820, 1968.<br />

[6] F. M. Kaassen, “Characterization <strong>of</strong> low 1/f noise in MOS transistors,”<br />

IEEE Trans. Electron Devices, vol. ED-18, pp. 887–891, Oct. 1971.<br />

[7] G. Reimbold, “Modified 1/f trapping noise theory <strong>and</strong> experiments in<br />

MOS transistors biased from weak to strong inversion-Influence <strong>of</strong> interface<br />

states,” IEEE Trans. Electron Devices, vol. ED-31, pp. 1190–1198,<br />

Sept. 1984.<br />

[8] K. H. Duh <strong>and</strong> A. van der Ziel, “Flicker noise in MOSFET’s with<br />

gate voltage-dependent mobility,” Solid-State Electron., vol. 27, pp.<br />

459–461, 1984.<br />

[9] C. Jakobson, I. Bloom, <strong>and</strong> Y. Nemirovsky, “1/f noise in CMOS transistors<br />

for analog applications from subthreshold to saturation,” Solid-State<br />

Electron., vol. 42, no. 10, pp. 1807–1817, 1998.<br />

[10] S. L. Jang, H. K. Chen, <strong>and</strong> M. C. Hu, “Low frequency 1/f noise model<br />

for short <strong>LDD</strong> MOS FET’s,” Solid-State Electron., vol. 42, no. 6, pp.<br />

891–899, 1998.<br />

[11] J. Brini, G. Ghibaudo, G. Kamarinos, <strong>and</strong> O. Roux-dit-Buisson, “Scaling<br />

down <strong>and</strong> low frequency noise in MOSFET’s,” Amer. Inst. Phys., pp.<br />

31–48, 1993.<br />

[12] M. H. Tsai <strong>and</strong> T. P. Ma, “The impact <strong>of</strong> device scaling on the current<br />

fluctuations in MOSFET’s,” IEEE Trans. Electron Devices, vol. 41, pp.<br />

2061–2221, Nov. 1994.<br />

[13] H. S. Park <strong>and</strong> A. van der Ziel, “Noise measurement in ion implanted<br />

MOSFET’s,” Solid-State Electron., vol. 26, no. 8, pp. 747–751, 1983.<br />

[14] M. J. Deen <strong>and</strong> Y. Zhu, “1/f noise in n-ch<strong>annel</strong> MOSFET’s at high<br />

temperatures,” Amer. Inst. Phys., pp. 165–188, 1993.<br />

[15] T. Takayanagi, K. Sawada, T. Sakurai, Y. Parameswar, S. Tanaka,<br />

N. Ikumi, M. Nagamatsu, Y. Kondo, K. Minagawa, J. Brennan, P.<br />

Hsu, P. Rodman, J. Bratt, J. Scanlon, M. Tang, C. Joshi, <strong>and</strong> M.<br />

N<strong>of</strong>al, “Embedded memory design for a four issue superscaler RISC<br />

microprocessor,” in Proc. IEEE Custom Integrated Circuits Conf.,<br />

1994, pp. 585–590.<br />

[16] M. Takada, K. Nakamura, <strong>and</strong> T. Yamazaki, “High speed submicron<br />

BiCMOS memory,” IEEE Trans. Electron Devices, vol. 42, pp. 497–505,<br />

Mar. 1995.<br />

[17] W. Muth, “Matrix method for latch-up free demonstration in a<br />

triple-well bulk-silicon technology,” IEEE Trans. Nucl. Sci., vol. 39, pt.<br />

I, pp. 396–400, Mar. 1992.<br />

[18] Y. Taur <strong>and</strong> T. H. Ning, Fundamentals <strong>of</strong> Modern VLSI Devices.<br />

Cambridge, U.K.: Cambridge Univ. Press, 1998.<br />

[19] F. Stern <strong>and</strong> W. E. Howard, “Properties <strong>of</strong> semiconductor inversion<br />

layers in the electric quantum limit,” Phys. Rev., vol. 163, pp. 816–835,<br />

1967.<br />

[20] Y. Ohkura, “Quantum effects in Si n-MOS inversion layer at high<br />

substrate concentration,” Solid-State Electron., vol. 33, pp. 1581–1585,<br />

1990.<br />

[21] F.-J. Huang <strong>and</strong> K. K. O, “Schottky-clamped NMOS transistors implemented<br />

in a conventional 0.8-m CMOS process,” IEEE Electron Device<br />

Lett., vol. 19, pp. 326–328, Sept. 1998.<br />

Effective Ch<strong>annel</strong> <strong>Length</strong> <strong>and</strong> <strong>External</strong> <strong>Series</strong> <strong>Resistance</strong><br />

<strong>Models</strong> <strong>of</strong> <strong>Scaled</strong> <strong>LDD</strong> pMOSFETs Operating in a Bi-MOS<br />

Hybrid-Mode Environment<br />

Siau Hing Lionel Seah, Kiat Seng Yeo, Jian Guo Ma, <strong>and</strong><br />

Manh Anh Do<br />

Abstract—The effective ch<strong>annel</strong> length <strong>and</strong> total external series<br />

resistance<br />

<strong>of</strong> deep submicron lightly doped drain (<strong>LDD</strong>)<br />

pMOSFETs, operating in a Bi-MOS hybrid-mode environment, have<br />

been modeled as functions <strong>of</strong> bias <strong>and</strong> temperature. The accuracy <strong>of</strong> the<br />

device threshold voltage used in the <strong>and</strong> extraction routine<br />

is discussed. The proposed models have been verified for temperature<br />

ranging from 223 K to 398 K <strong>and</strong> source-to-body voltage 0 V<br />

conditions.<br />

Index Terms—Deep submicron, effective ch<strong>annel</strong> length, external series<br />

resistance, hybrid-mode, lightly doped drain (<strong>LDD</strong>), temperature-dependent.<br />

I. INTRODUCTION<br />

The L e <strong>and</strong> R TOText are important parameters needed to accurately<br />

model the I-V characteristics <strong>of</strong> short-ch<strong>annel</strong> <strong>LDD</strong> MOSFETs<br />

[1]. Most analyses in the literature (e.g., [2]–[12]) either ignore the<br />

body terminal <strong>of</strong> the devices, assume the body <strong>and</strong> source terminals<br />

having the same potential, or consider the source-body junction<br />

in reverse biased mode. Recently, hybrid-mode devices employing<br />

lateral p-n-p BJT in a pMOS structure have been brought into attention<br />

due to their high current gain <strong>and</strong> simple technology [13]–[15].<br />

For a device operating in a Bi-MOS hybrid-mode environment, its<br />

gate <strong>and</strong> body terminals may be biased independently such that potential<br />

across the source-body junction becomes greater than 0 V,<br />

while maintaining the MOSFET in active mode. This requirement<br />

has prompted the question <strong>of</strong> whether or not L e <strong>and</strong> R TOText commonly<br />

extracted from the experimental data remain valid for V SB 0<br />

V. The knowledge <strong>of</strong> such dependency on the body bias is important<br />

to ensure proper prediction <strong>of</strong> the device performance in hybrid-mode<br />

operation.<br />

II. DEVICE STRUCTURES AND MEASURING EQUIPMENT<br />

The device structure used in the measurement consists <strong>of</strong> a series<br />

<strong>of</strong> silicon p-ch<strong>annel</strong> <strong>LDD</strong> MOSFETs fabricated with a gate oxide<br />

thickness t ox <strong>of</strong> 5 nm. The ch<strong>annel</strong> width W for all devices is 20<br />

m, whereas the gate length L varies from 1 m down to 0.25<br />

m. N-well implantation was formed using phosphorus <strong>of</strong> 2 2 10 13<br />

cm 02 dosage <strong>and</strong> an energy level <strong>of</strong> 600 keV. The drain/source<br />

implantation was carried out using boron with a dose <strong>of</strong> 3 2 10 15<br />

cm 02 <strong>and</strong> an energy level <strong>of</strong> 30 keV. The p 0 <strong>LDD</strong> implants were<br />

established with a dose <strong>of</strong> 2 2 10 14 cm 02 <strong>and</strong> an energy level<br />

<strong>of</strong> 20 keV. The p + junction depth X j <strong>and</strong> the p-<strong>LDD</strong> junction<br />

depth r j are approximately 0.15 m <strong>and</strong> 0.075 m, respectively. A<br />

ch<strong>annel</strong> implant dose <strong>of</strong> 3 2 10 12 cm 02 <strong>and</strong> an energy level <strong>of</strong> 70<br />

keV is added for threshold voltage adjustment. Device measurements<br />

were performed using a semiconductor parameter analyzer <strong>and</strong> a<br />

TEMPTRONIC system which controls the temperature <strong>of</strong> the wafer<br />

Manuscript received June 19, 2000; revised September 22, 2000. The review<br />

<strong>of</strong> this brief was arranged by Editor M. Hirose.<br />

The authors are with the Division <strong>of</strong> Circuits <strong>and</strong> Systems, School <strong>of</strong> Electrical<br />

<strong>and</strong> Electronic Engineering, Nanyang Technological University, Singapore<br />

639798.<br />

Publisher Item Identifier S 0018-9383(01)03255-5.<br />

0018–9383/01$10.00 © 2001 IEEE

1002 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 48, NO. 5, MAY 2001<br />

to an accuracy <strong>of</strong> 6 0.5 K. Measurements were done <strong>and</strong> repeated<br />

on a vibration-free table with the CASCADE MICROTECH probing<br />

station enclosed in a light-shield box.<br />

III. R TOText AND L e EXTRACTION AND MODELING<br />

Assuming symmetrical device <strong>and</strong> applying very low source-todrain<br />

voltage V SD , the total source-to-drain resistance across the<br />

extrinsic pMOSFET can be derived from the liner region drain current<br />

expression as in [16], expressed as<br />

R tot = R TOText(V SG;V SB;T)<br />

L 0 1L(V SG ;V SB ;T)<br />

+<br />

pe C ox W (V SG 0 V te 0 0:5V SD )<br />

(1)<br />

where<br />

R TOText<br />

1L<br />

sum <strong>of</strong> resistances <strong>of</strong> the contact, wiring, p + diffusion<br />

region, <strong>and</strong> p 0 lightly doped regions <strong>of</strong> the source <strong>and</strong><br />

drain side;<br />

ch<strong>annel</strong> length reduction;<br />

C ox gate oxide capacitance per unit area;<br />

pe temperature-dependent hole mobility adapted from [17].<br />

Expressions similar to (1) have been reported in [1]–[8], [18]. However,<br />

they have generally made use <strong>of</strong> a device threshold voltage obtained<br />

at room temperature <strong>and</strong> V SB = 0 V. As widely known, the<br />

threshold voltage <strong>of</strong> short-ch<strong>annel</strong> devices is related to the drain/body<br />

bias, ch<strong>annel</strong> length <strong>and</strong> temperature. Hence, using a bias/temperature-independent<br />

threshold voltage in the extraction routine would be<br />

inadequate for V SB 0 V <strong>and</strong>/or when the temperature differs from<br />

the room temperature. To overcome this problem, an effective threshold<br />

voltage suitable for Bi-MOS hybrid-mode operating condition is used<br />

here. The effective threshold voltage, considering drain-induced barrier<br />

lowering (DIBL), body-induced-barrier-lowering (BIBL), <strong>and</strong> temperature<br />

effects, is expressed as<br />

Fig. 1. Effects <strong>of</strong> V on the effective threshold voltage V . The data<br />

markers , , , , , }, 4, <strong>and</strong> represent the extracted threshold voltage<br />

at 223 K, 248 K, 273 K, 300 K, 323 K, 348 K, 373 K, <strong>and</strong> 398 K, respectively.<br />

The solid lines represent the modeled results using TC = 0:25 V <strong>and</strong><br />

TC =0:23 V.<br />

V te = V TO 0 V SD 0 V SB 0 (TC 1 + TC 2V SB)<br />

T<br />

1<br />

300 K 0 1 (2)<br />

where V TO is the zero-bias threshold voltage extracted at T = 300<br />

K using the “Transconductance Peak” method [19]. For V SD =0:05<br />

V considered here, the DIBL effect contributed by the term V SD<br />

can be ignored. The BIBL factor accounts for the reduction<br />

in the threshold voltage when V SB increases [13]. The parameter<br />

TC 1 is defined as the temperature compensation factor extracted at<br />

V SB = V SD =0V, whereas TC 2 is the temperature compensation<br />

factor for V SB > 0 V. The composite effect <strong>of</strong> V SB <strong>and</strong> temperature<br />

on V te is illustrated in Fig. 1. At V SB =0V, V te reduces about<br />

23% when the temperature increases from 223 K to 398 K. However,<br />

for V SB > 0 V, the reduction rate <strong>of</strong> V te with temperature<br />

increases. The use <strong>of</strong> (2) in the extraction procedure implies that for a<br />

specific source-to-gate bias V SG , the gate drive V GT =(V SG 0V te 0<br />

0:5V SD) varies with L, T <strong>and</strong> V SB through V te . Therefore, any<br />

extraction errors contributed by using a bias/temperature-independent<br />

threshold voltage are avoided.<br />

As widely known, the carrier density modulation effect in the<br />

overlapping regions between the lightly doped regions <strong>and</strong> the gate<br />

in the <strong>LDD</strong> structure, <strong>and</strong> the fringing field conductivity modulation<br />

effect cause R TOText to be gate-bias-dependent. On the other h<strong>and</strong>,<br />

the increase in gate control over the mobile charge at the two ends <strong>of</strong><br />

the ch<strong>annel</strong> leads to the expansion <strong>of</strong> the effective ch<strong>annel</strong> toward the<br />

source <strong>and</strong> drain regions. Fig. 2 shows R TOText <strong>and</strong> 1L at various<br />

Fig. 2. Gate modulation effects <strong>of</strong> R <strong>and</strong> 1L observed using “Paired<br />

V ” method [3]. Data markers <strong>and</strong> represent the R <strong>and</strong> 1L<br />

at 300 K, respectively; <strong>and</strong> represent the R <strong>and</strong> 1L at 398 K <strong>and</strong><br />

4 <strong>and</strong> represent the R <strong>and</strong> 1L at 223 K.<br />

temperatures exhibiting similar declining trends with increasing V GT .<br />

For V SB = 0 V <strong>and</strong> T = 300 K, R TOText <strong>and</strong> 1L decrease by<br />

28.75% <strong>and</strong> 18.02%, respectively, as the gate drive V GT increases<br />

from 0.55 V to 1.95 V. Reductions in R TOText <strong>and</strong> 1L result in higher<br />

V SDe appearing across a “longer” intrinsic pMOSFET ch<strong>annel</strong>. This<br />

phenomenon is critical in deep submicron devices because <strong>of</strong> the<br />

associated scaling <strong>of</strong> supply voltage (i.e., V SD) applied to the extrinsic<br />

pMOSFET. If gate-bias-independent R TOText <strong>and</strong> 1L values, extrapolated<br />

at a low gate bias, are used in modeling the I-V characteristics<br />

<strong>of</strong> the device, underestimation <strong>of</strong> source-to-drain current I SD would be<br />

resulted at high V SG biases. Therefore, the determination <strong>of</strong> R TOText<br />

(V SG ) <strong>and</strong> 1L (V SG ) is important to ensure accurate prediction <strong>of</strong> the<br />

device characteristics for a wide range <strong>of</strong> gate biases.<br />

To investigate the effect <strong>of</strong> V SB <strong>and</strong> temperature independently, the<br />

extracted R TOText <strong>and</strong> 1L are averaged over the entire V GT range<br />

considered earlier. This is accomplished by extending the method<br />

proposed in [18] to various V SB biasing <strong>and</strong> temperature conditions.<br />

This technique allows the isolation <strong>of</strong> the gate modulation effect <strong>and</strong><br />

yet does not require a fixed gate bias to be defined. In retrospect

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 48, NO. 5, MAY 2001 1003<br />

TABLE I<br />

EXTRACTED COEFFICIENTS FOR THE R<br />

OUR DEVICES<br />

AND 1L MODELS FOR<br />

Combining the gate bias modulation, temperature <strong>and</strong> body bias effects,<br />

the R TOText () <strong>and</strong> L e (m) are modeled as<br />

R TOText (V SG ;V SB ;T)=aT + b 0 c(V SG 0 V te ) 0 dV SB (3)<br />

L e (V SG;V SB;T)=L(m) 0 1L(V SG;V SB;T) (4)<br />

1L(V SG ;V SB ;T)=eT + f 0 g(V SG 0 V te ) 0 hV SB (5)<br />

Fig. 3. Dependence <strong>of</strong> R <strong>and</strong> 1L on source-body voltage V <strong>and</strong><br />

temperature (inset).<br />

where a; b; c; d; e; f; g; <strong>and</strong> h are coefficients extracted experimentally,<br />

given in Table I. The validity <strong>of</strong> the proposed R TOText , L e <strong>and</strong> V te<br />

models are verified by applying the modeled values into conventional<br />

drain current model expression as in [16]. Fig. 4 demonstrates good<br />

agreements between the experimental <strong>and</strong> modeled drain current characteristics<br />

for a wide range <strong>of</strong> biases <strong>and</strong> temperatures.<br />

IV. CONCLUSIONS<br />

The R TOText <strong>and</strong> L e <strong>of</strong> scaled hybrid-mode devices have been<br />

investigated. Together with a novel V te expression, analytical L e<br />

<strong>and</strong> R TOText models useful for devices operating in a Bi-MOS hybrid-mode<br />

environment have been presented. By including the effect <strong>of</strong><br />

body bias <strong>and</strong> temperature in the R TOText , L e , <strong>and</strong> V te models, the<br />

drain current characteristics <strong>of</strong> scaled devices operating in a Bi-MOS<br />

hybrid-mode environment can be predicted accurately using conventional<br />

drain current expression.<br />

ACKNOWLEDGMENT<br />

Fig. 4. Prediction <strong>of</strong> the drive current (solid lines) for different temperatures,<br />

gate lengths <strong>and</strong> body/gate terminal biases. The markers , }, <strong>and</strong> 4 represent<br />

the measurement data for V = 0 V, 0.4 V, <strong>and</strong> 0.6 V, respectively.<br />

[4], a very slight increment in R TOText <strong>and</strong> 1L with temperature<br />

has been observed, as depicted in Fig. 3 (inset). Although applying<br />

V SB > 0 V reduces the charge sharing effect [5], [7], narrowing<br />

<strong>of</strong> the depletion width at the source-body <strong>and</strong> drain-body junctions<br />

lengthens the effective ch<strong>annel</strong> region, justified by the reduction in<br />

1L with increasing V SB as indicated in Fig. 3. It is interesting to note<br />

that this ch<strong>annel</strong> lengthening effect appears to increase the numerator<br />

<strong>of</strong> the second term in (1), <strong>and</strong> hence the ch<strong>annel</strong> resistance. However,<br />

applying V SB also causes the physical broadening <strong>of</strong> the ch<strong>annel</strong><br />

formation under the gate. In contrast, this phenomenon reduces the<br />

intrinsic ch<strong>annel</strong> resistance. As mentioned earlier, increasing V SB<br />

reduces V te . This effect reduces the ch<strong>annel</strong> resistance per unit<br />

length <strong>and</strong> is well represented by utilizing V te in the second term in<br />

(1). As compared to V SB =0V condition, I SD increases when the<br />

device is biased with V SB > 0 V. For a fixed V SD, R tot = V SD=I SD<br />

reduces as a result. From the experimental results, the drop in R tot<br />

resulted from the increase in ch<strong>annel</strong> carriers collected at the drain<br />

region is also reflected in the trend <strong>of</strong> R TOText, as shown in Fig. 3.<br />

Therefore, the results have proven that one important contributing<br />

factor to I SD increment for V SB > 0 V is the composite effect<br />

between the resultant R TOText , 1L, <strong>and</strong> V te .<br />

The authors would like to acknowledge Chartered Semiconductor<br />

Manufacturing Ltd for supplying the test wafers. They are also grateful<br />

to the reviewers for their valuable comments.<br />

REFERENCES<br />

[1] S. S. S. Chung <strong>and</strong> J. S. Lee, “A new approach to determine the<br />

drain-<strong>and</strong>-source resistance <strong>of</strong> <strong>LDD</strong> MOSFETs,” IEEE Trans. Electron<br />

Devices, vol. 40, pp. 1709–1711, Sept. 1993.<br />

[2] J. Y. C. Sun, M. R. Wordeman, <strong>and</strong> S. E. Laux, “On the accuracy <strong>of</strong><br />

ch<strong>annel</strong> length characterization <strong>of</strong> <strong>LDD</strong> MOSFETs,” IEEE Trans. Electron<br />

Devices, vol. ED-33, pp. 1556–1562, Oct. 1986.<br />

[3] G. J. Hu, C. Chang, <strong>and</strong> Y. T. Chia, “Gate-voltage-dependent effective<br />

ch<strong>annel</strong> length <strong>and</strong> series resistance <strong>of</strong> <strong>LDD</strong> MOSFETs,” IEEE Trans.<br />

Electron Devices, vol. ED-34, pp. 2469–2475, Dec. 1987.<br />

[4] Y. Taur, D. S. Zicherman, D. R. Lombardi, P. J. Restle, C. H. Hsu, H. I.<br />

Hanafi, M. R. Wordeman, B. Davari, <strong>and</strong> G. G. Shahidi, “A new shift <strong>and</strong><br />

ratio method for MOSFET ch<strong>annel</strong>-length extraction,” IEEE Electron<br />

Device Lett., vol. 13, pp. 267–269, May 1992.<br />

[5] S. Hong <strong>and</strong> K. Lee, “Extraction <strong>of</strong> metallurgical effective ch<strong>annel</strong><br />

length in <strong>LDD</strong> MOSFETs,” IEEE Trans. Electron Devices, vol. 42, pp.<br />

1461–1466, Aug. 1995.<br />

[6] Y. S. Jean <strong>and</strong> C. Y. Wu, “A new extraction algorithm for the metallurgical<br />

ch<strong>annel</strong> length <strong>of</strong> conventional <strong>and</strong> <strong>LDD</strong> MOSFETs,” IEEE Trans.<br />

Electron Devices, vol. 43, pp. 946–953, June 1996.<br />

[7] C. M. Wu <strong>and</strong> C. Y. Wu, “A new method for extracting the<br />

ch<strong>annel</strong>-length reduction <strong>and</strong> the gate-voltage-dependent series resistance<br />

<strong>of</strong> counter-implanted p-MOSFETs,” IEEE Trans. Electron<br />

Devices, vol. 44, pp. 2193–2199, Dec. 1997.<br />

[8] T. H. Chang, J. G. Lo, T. C. Kuo, C. C. H. Hsu, S. Y. Yu, K. F. Tseng, <strong>and</strong><br />

L. S. Lu, “Effective ch<strong>annel</strong> length <strong>and</strong> source-drain series-resistance determination<br />

after electrical gate length verification <strong>of</strong> metal-oxide-semiconductor<br />

field-effect-transistor,” Jpn. J. Appl. Phys., vol. 37, part 1, no.<br />

3A, pp. 796–800, Mar. 1998.

1004 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 48, NO. 5, MAY 2001<br />

[9] K. K. Ng <strong>and</strong> W. T. Lynch, “Analysis <strong>of</strong> the gate-voltage-dependent<br />

series resistance <strong>of</strong> MOSFETs,” IEEE Trans. Electron Devices, vol.<br />

ED-33, pp. 965–972, July 1986.<br />

[10] K. Takeuchi, N. Kasai, <strong>and</strong> K. Terada, “A new effective ch<strong>annel</strong> length<br />

determination method for <strong>LDD</strong> MOSFETs,” in Proc. IEEE Int. Conf.<br />

Microelectronic Test Structures, vol. 4, Mar. 1991, pp. 215–220.<br />

[11] J. A. M. Otten <strong>and</strong> F. M. Klaassen, “A novel technique to determine<br />

the gate <strong>and</strong> drain bias dependent series resistance in drain engineered<br />

MOSFETs using one single device,” IEEE Trans. Electron Devices, vol.<br />

43, pp. 1478–1488, Sept. 1996.<br />

[12] S. S. Liu <strong>and</strong> S. L. Jang, “Deep-submicron lightly-doped-drain <strong>and</strong><br />

single-drain metal-oxide-semiconductor transistor drain current model<br />

for circuit simulation,” Jpn. J. Appl. Phys., vol. 37, part 1, pp. 64–71,<br />

Jan. 1998.<br />

[13] S. S. R<strong>of</strong>ail <strong>and</strong> K. S. Yeo, “Experimentally-based analytical model <strong>of</strong><br />

deep submicron <strong>LDD</strong> MOSFETs in a Bi-MOS hybrid-mode environment,”<br />

IEEE Trans. Electron Devices, vol. 44, pp. 1473–1482, Sept.<br />

1997.<br />

[14] S. A. Parke, C. H. Hu, <strong>and</strong> P. K. Ko, “Bipolar-FET hybrid-mode operation<br />

<strong>of</strong> quarter-micrometer SOI MOSFETs,” IEEE Electron Device<br />

Lett., vol. 14, pp. 234–236, May 1993.<br />

[15] S. Verdouckt-V<strong>and</strong>erbroek, S. S. Wong, J. C. S. Woo, <strong>and</strong> P. K. Ko,<br />

“High-gain lateral bipolar action in a MOSFET structure,” IEEE Trans.<br />

Electron Devices, vol. 38, pp. 2487–2496, Nov. 1991.<br />

[16] K. Y. Toh, P. K. Ko, <strong>and</strong> R. G. Meyer, “An engineering model for<br />

short-ch<strong>annel</strong> MOS devices,” IEEE J. Solid-State Circuits, vol. 23, pp.<br />

950–957, Aug. 1988.<br />

[17] B. H. Cheng <strong>and</strong> J. Woo, “A temperature-dependent MOSFET inversion<br />

layer carrier mobility model for device <strong>and</strong> circuit simulation,” IEEE<br />

Trans. Electron Devices, vol. 44, pp. 343–345, Feb. 1997.<br />

[18] S. E. Laux, “Accuracy <strong>of</strong> an effective ch<strong>annel</strong> length/external resistance<br />

extraction algorithm for MOSFETs,” IEEE Trans. Electron Devices, vol.<br />

ED-31, pp. 1245–1251, Sept. 1984.<br />

[19] R. V. Booth, M. H. White, H. S. Wong, <strong>and</strong> T. J. Krutsick, “The effect<br />

<strong>of</strong> ch<strong>annel</strong> implants on MOS transistor characterization,” IEEE Trans.<br />

Electron Devices, vol. ED-34, pp. 2501–2508, Dec. 1987.<br />

Patterning Sub-30-nm MOSFET Gate with<br />

Lithography<br />

-Line<br />

Kazuya Asano, Yang-Kyu Choi, Tsu-Jae King, <strong>and</strong> Chenming Hu<br />

Abstract—We have investigated two process techniques: resist ashing<br />

<strong>and</strong> oxide hard mask trimming. A combination <strong>of</strong> ashing <strong>and</strong> trimming<br />

produces sub-30-nm MOSFET gate. These techniques require neither<br />

specific equipment nor materials. These can be used to fabricate experimental<br />

devices with line width beyond the limit <strong>of</strong> optical lithography or<br />

high-throughput -beam lithography. They provide 25-nm gate pattern<br />

with -line lithography <strong>and</strong> sub-20-nm pattern with -beam lithography.<br />

A 40-nm gate ch<strong>annel</strong> length nMOSFET is demonstrated.<br />

I. INTRODUCTION<br />

Currently, MOSFET gate length for advanced research is below<br />

50 nm. Making such a small feature is not an easy task, in general.<br />

Although e-beam lithography employing some positive resists such as<br />

PMMA has high resolution, its throughput is too low even for research.<br />

Manuscript received May 30, 2000; revised October 12, 2000. This work was<br />

supported by DARPA AME Program under Contract N66001-97-1-8910. The<br />

review <strong>of</strong> this brief was arranged by Editor R. Singh.<br />

K. Asano is with the NKK Corporation, Kanagawa 212-0013, Japan.<br />

Y.-K. Choi, T.-J. King, <strong>and</strong> C. Hu are with the Department <strong>of</strong> Electrical Engineering<br />

<strong>and</strong> Computer Sciences, University <strong>of</strong> California, Berkeley, CA 94720<br />

USA (e-mail: ykchoi@eecs.berkeley.edu).<br />

Publisher Item Identifier S 0018-9383(01)03256-7.<br />

We will discuss two techniques that provide sub-30-nm line width<br />

without using any special equipment or materials. The first technique<br />

is resist ashing. This technique was developed for making submicron<br />

devices from g-line lithography about ten years ago [1]. Since then, it<br />

has been rather widely used to produce smaller features than the resolution<br />

limit <strong>of</strong> optical lithography [2]–[4]. The second technique is<br />

an oxide hard mask trimming. Oxide hard mask trimming is relatively<br />

straightforward, but we have found no reports that describe it, let alone<br />

report on its use in the sub-30-nm regime. A combination <strong>of</strong> these two<br />

techniques makes it possible to fabricate 25 nm line width using i-line<br />

lithography.<br />

II. EXPERIMENTS AND RESULTS<br />

A. Ashing <strong>of</strong> i-Line Resist<br />

Sample wafers were exposed with an i-line stepper. The thickness<br />

<strong>of</strong> the positive i-line resist was 1.1 m <strong>and</strong> baked at 90 C for 1 min<br />

before exposure <strong>and</strong> 120 C for 1 min after exposure, respectively. The<br />

resist patterns after a development were ashed in an oxygen-plasma<br />

asher, Technics PE II. Oxygen pressure was 260 mTorr with a flow rate<br />

<strong>of</strong> 51.1 sccm.<br />

The ashing rate <strong>of</strong> the i-line resist without hard baking (120 C) is<br />

shown in Fig. 1. The vertical ashing rate is the rate <strong>of</strong> reduction <strong>of</strong> the<br />

resist thickness, while the horizontal ashing rate is the rate <strong>of</strong> reduction<br />

<strong>of</strong> the line width. Both ashing rates change linearly with the ashing<br />

power <strong>and</strong> are independent <strong>of</strong> the initial line width.<br />

The ratio <strong>of</strong> the horizontal ashing rate to the vertical ashing rate is<br />

about 1.2:1, which produces isotropic pr<strong>of</strong>ile. Ashing does not change<br />

the edge roughness <strong>of</strong> the resist as shown in Fig. 2(a). The smoothness<br />

<strong>of</strong> the initial lines is very important for good ashing results. In the case<br />

<strong>of</strong> i-line lithography, line smoothness depends strongly on the mask<br />

quality.<br />

The taper angle <strong>of</strong> the narrow resist pr<strong>of</strong>ile at the top corner increases<br />

slightly after ashing. The top <strong>of</strong> the resist may be rounded in the end.<br />

This can happen earlier in narrow lines than in wide patterns. Even if<br />

the top <strong>of</strong> the resist is rounded <strong>of</strong>f, etching does not present a problem<br />

as long as the resist is thick enough.<br />

B. Ashing e-Beam Resist<br />

Two chemically amplified resists, SNR-2000 <strong>and</strong> SAL601, were<br />

evaluated. Ashing <strong>of</strong> the e-beam resists was done in the same asher,<br />

Technics PE II.<br />

In the case <strong>of</strong> e-beam resist patterns, only a small amount <strong>of</strong> ashing<br />

compared to i-line patterns is needed because the initial line width is<br />

100 nm or less. We fixed the ashing power at 5 W, which was the lowest<br />

power to sustain stable plasma. The ashing rates <strong>of</strong> the e-beam resists<br />

are 22–30 nm/min at 5 W power. For SAL <strong>and</strong> SNR, the ashing rates<br />

were almost the same.<br />

One interesting phenomenon is resist hardening caused by SEM.<br />

Since SAL <strong>and</strong> SNR are negative resists, they are hardened by the exposure<br />

to e-beam (energy is less than 1 KeV) during SEM. After SEM,<br />

ashing rate <strong>of</strong> the resist patterns exposed to the e-beam decreased to<br />

two-thirds <strong>of</strong> those not exposed.<br />

In Fig. 3(a), the SEM picture <strong>of</strong> a 17-nm ashed SNR-2000 resist line<br />

is shown. This line was originally 80-nm wide after e-beam lithography.<br />

C. Oxide Hard Mask Trimming<br />

The concept <strong>of</strong> oxide hard mask trimming is similar to the resist<br />

ashing. After the ashing-down <strong>of</strong> the gate resist patterns, an oxide<br />

hard mask pattern is anisotropically etched. A Lam research model<br />

0018–9383/01$10.00 © 2001 IEEE