DTX-360 Maintenance Manual - Salvex

DTX-360 Maintenance Manual - Salvex

DTX-360 Maintenance Manual - Salvex

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>DTX</strong>-<strong>360</strong><br />

DIGITAL CIRCUIT<br />

MULTIPLICATION EQUIPMENT<br />

<strong>Maintenance</strong> <strong>Manual</strong><br />

Copyright © ECI Telecom Ltd.1998. All Rights Reserved.<br />

This manual may contain minor flaws, omissions, or typesetting errors. Information contained herein is<br />

periodically updated and changes will be incorporated into subsequent editions. If you have encountered an<br />

error, please notify ECI Telecom. All specifications are subject to change without prior notice.

REVISION RECORD<br />

REVISION<br />

01 Preliminary<br />

January 1994<br />

02 First edition and printing<br />

June 1997<br />

03<br />

December 1997<br />

DESCRIPTION<br />

Addition of pages 1-8 to1-11 - Card replacement and card<br />

malfunction detection<br />

04<br />

March 1998 Changes and additions to pages: 5-6, 5-25, 5-35, 1-11-1-14<br />

Publ n No.<br />

92050003

CE MARK COMPLIANCE<br />

The <strong>DTX</strong>-<strong>360</strong> is marked with a CE Mark (see below). This mark has been affixed to<br />

demonstrate full product compliance with the following European directives:<br />

a) Directive 73/23/EEC - Council Directive of 19/02/1973 on the harmonization of the laws<br />

of Member States relating to electrical equipment designed for use within certain voltage<br />

limits.<br />

b) Directive 89/336/EEC - Council Directive of 3/05/1989 on the approximation of laws of<br />

the Member States relating to Electro-Magnetic Compatibility (EMC).<br />

Issue date: 6 February 1996<br />

This document contains proprietary information. It may not, in whole or in part, be published, used, or<br />

reproduced, nor may be disclosed to third parties without the express written permission of ECI Telecom.<br />

© Copyright by ECI Telecom Ltd., 1997<br />

All rights reserved worldwide<br />

ECI Telecom reserves the right, without notice, to make changes in equipment design or<br />

specifications.<br />

Information supplied by ECI Telecom is believed to be accurate and reliable. However, no<br />

responsibility is assumed by ECI Telecom for its use nor for rights of third parties which may<br />

result from its use.<br />

Any representations in this document concerning performance are for informational purposes only<br />

and are not warranties of future performance, either express or implied. ECI Telecom’s standard<br />

limited warranty, stated in its sales contract or order confirmation form, is the only warranty<br />

offered by ECI Telecom.

<strong>DTX</strong>-<strong>360</strong><br />

<strong>Maintenance</strong> <strong>Manual</strong><br />

Table of Contents<br />

Section Description Page<br />

1 GENERAL INFORMATION ..........................................................................1-1<br />

1.1 INTRODUCTION............................................................................................... 1-1<br />

1.2 STATIC AWARENESS ..................................................................................... 1-1<br />

1.3 REPAIR AND RETURN .................................................................................... 1-2<br />

1.3.1 Order Entry (normal shipping time).................................................................... 1-2<br />

1.3.2 Terminal Malfunction Report ............................................................................. 1-2<br />

1.3.3 Order Entry (Emergency Order) ......................................................................... 1-4<br />

1.3.4 Insurance Policy.................................................................................................. 1-4<br />

1.3.5 Substitutions and Modifications ......................................................................... 1-4<br />

1.3.6 Limitations of Liability ....................................................................................... 1-4<br />

1.4 OPS REPAIR ...................................................................................................... 1-5<br />

1.5 TASKS AUTHORIZED FOR THE USER......................................................... 1-5<br />

1.6 HANDLING OF ELECTROSTATICALLY SENSITIVE COMPONENTS ..... 1-5<br />

1.7 HANDLING PRINTED CIRCUIT BOARDS .................................................... 1-6<br />

1.8 HANDLING PERIPHERAL EQUIPMENT AND TERMINALS ..................... 1-6<br />

1.9 HANDLING THE OPERATOR STATION....................................................... 1-7<br />

1.10 AC POWER OUTLETS ..................................................................................... 1-7<br />

1.11 DETECTING CARD MALFUNCTIONS .......................................................... 1-8<br />

1.12 DETECTING THE SOURCE OF A CARD MALFUNCTION......................... 1-8<br />

1.13 CARD REMOVAL UNDER POWER ............................................................. 1-10<br />

1.14 OMCP/COCP CARD REPLACEMENT.......................................................... 1-11<br />

1.14.1 Modifying the ethers file................................................................................... 1-11<br />

1.14.2 Modifying the hosts file .................................................................................... 1-12<br />

1.14.3 Modifying the config file .................................................................................. 1-12<br />

1.14.4 Modifying the pofInfo_am file.......................................................................... 1-12<br />

1.14.5 Resuming Operation.......................................................................................... 1-12<br />

1.15 TO TURN A TERMINAL OFF........................................................................ 1-13<br />

1.15.1 Stand Alone Configuration ............................................................................... 1-13<br />

1.15.2 Cluster configuration......................................................................................... 1-13<br />

2 INTERNAL AND CLUSTER CABLE CONNECTIONS.............................2-1<br />

2.1 GENERAL .......................................................................................................... 2-1<br />

2.2 TERMINAL - LCOM CONNECTIONS ............................................................ 2-2<br />

2.2.1 Bitstream Connection.......................................................................................... 2-2<br />

2.3 LCOM - CCOM CONNECTIONS (FIGURES 2-2 AND 2-3)........................... 2-4<br />

2.3.1 DLC Connections................................................................................................ 2-4<br />

2.3.2 BitstreamConnections ......................................................................................... 2-4<br />

2.4 CCOM - REDUNDANT TERMINAL CONNECTIONS (FIGURES 2-4, 2-5). 2-7<br />

2.4.1 Bitstream Connections ........................................................................................ 2-7<br />

2.4.2 DLC Connections................................................................................................ 2-7<br />

2.4.3 LCOM - Four (4) Compact Terminals Connections (<strong>DTX</strong>-<strong>360</strong>C ) ................. 2-10<br />

2.4.3.1 Bitstream Connections ...................................................................................... 2-10<br />

2.4.3.2 DLC Connections.............................................................................................. 2-10<br />

92050003-03 i

Table of Contents<br />

Section Description Page<br />

2.4.4 SCOM - Three (3) Compact Terminals + Redundant Terminal<br />

Connections (<strong>DTX</strong>-<strong>360</strong>C)................................................................................. 2-12<br />

2.4.4.1 Bitstream Connections ...................................................................................... 2-12<br />

2.4.4.2 DLC Connections.............................................................................................. 2-12<br />

2.4.5 SCOM + Two (2) Terminals + Redundant Terminal Connections................... 2-14<br />

2.4.5.1 Bitstream Connections ...................................................................................... 2-14<br />

2.4.5.2 DLC Connections.............................................................................................. 2-14<br />

3 TRANSMISSION ALARMS............................................................................3-1<br />

3.1 2.048 MBIT/S E1 TRANSMISSION ALARMS DESCRIPTION ..................... 3-1<br />

3.1.1 Loss of Incoming Signal (LOS) .......................................................................... 3-1<br />

3.1.2 Alarm Indication Signal (AIS) ............................................................................ 3-1<br />

3.1.3 Loss of Alignment (LOF) Alarm ........................................................................ 3-2<br />

3.1.4 CRC Multiframe (CRC MFR) ............................................................................ 3-2<br />

3.1.5 High CRC Error .................................................................................................. 3-2<br />

3.1.6 High Bit Error Rate (H.BER).............................................................................. 3-3<br />

3.1.6.1 H.BER, Bitstream with the CRC Format ............................................................ 3-3<br />

3.1.6.2 H.BER, Bitstream without CRC Format............................................................. 3-3<br />

3.1.7 Low Bit Error Rate (L.BER)............................................................................... 3-3<br />

3.1.7.1 L.BER, Bitstream without CRC Format ............................................................. 3-3<br />

3.1.7.2 L.BER, Bitstream with the CRC Format ............................................................ 3-3<br />

3.1.8 Remote (Far-end) Alarm Indication (RAI) ......................................................... 3-3<br />

3.1.9 Multiframe Alignment (MFR) ............................................................................ 3-4<br />

3.1.10 Remote Multiframe Alarm Indication (RMFR).................................................. 3-4<br />

3.1.11 High Slip Rate (H.SLIP) ..................................................................................... 3-4<br />

3.1.12 Low Slip Rate (L.SLIP) ...................................................................................... 3-4<br />

3.1.13 No External Clock Alarm.................................................................................... 3-4<br />

3.1.14 Bitstream or External Clock Fail ........................................................................ 3-5<br />

3.1.15 DCME Frame Alarm (DFA) ............................................................................... 3-5<br />

3.1.16 CC-HBER............................................................................................................ 3-5<br />

3.1.16.1 Activation Criteria............................................................................................... 3-5<br />

3.1.16.2 Deactivation Criteria........................................................................................... 3-5<br />

3.1.17 CC-LBER............................................................................................................ 3-5<br />

3.1.17.1 Activation Criteria............................................................................................... 3-5<br />

3.1.17.2 Deactivation Criteria........................................................................................... 3-6<br />

3.1.18 CC-AIS................................................................................................................ 3-6<br />

3.1.19 Bearer Backward Alarm...................................................................................... 3-6<br />

3.1.20 Far-End (Remote) Trunk Alarm.......................................................................... 3-6<br />

3.2 1.544 MBIT/S T1 TRANSMISSION ALARMS DESCRIPTION ..................... 3-7<br />

3.2.1 Loss Of Frame alignment (LOF - CFA)............................................................ 3-7<br />

3.2.2 Loss Of incoming Signal (LOS) ........................................................................ 3-7<br />

3.2.3 Alarm Indication Signal (AIS-CFA) ................................................................... 3-7<br />

3.2.4 High Bit Error Rate (HBER).............................................................................. 3-8<br />

3.2.5 Remote (Far-end, Distant) Alarm Indication (RAI) - (Yellow)............................ 3-8<br />

3.2.6 Low Bit Error Rate (LBER).............................................................................. 3-9<br />

3.3 MAINTENANCE LEVELS OF TRANSMISSION ALARMS AND<br />

EVENTS (E1 SYSTEM) .................................................................................. 3-10<br />

ii 92050003-02

Table of Contents<br />

Section Description Page<br />

3.4 <strong>Maintenance</strong> Levels of Transmission<br />

Alarms (T1 System) .......................................................................................... 3-13<br />

3.4.1 Change Clock Alarm Severity........................................................................... 3-13<br />

3.5 TRANSMISSION ALARM HANDLING ........................................................ 3-14<br />

4 SYSTEM ALARMS AND EVENTS................................................................4-1<br />

4.1 SYSTEM EVENTS............................................................................................. 4-1<br />

4.2 CCOM EVENTS................................................................................................. 4-3<br />

4.3 OPS ACTIONS ................................................................................................... 4-4<br />

4.4 <strong>DTX</strong>-<strong>360</strong> RESPONSES TO OPS ACTIONS ..................................................... 4-6<br />

4.5 ONLINE BIT TESTS.......................................................................................... 4-9<br />

4.5.1 SIGN Hardware Online Test Options ................................................................. 4-9<br />

4.5.1.1 MFR Trunk (0:15)............................................................................................... 4-9<br />

4.5.1.2 TRUNK OUT Path Test...................................................................................... 4-9<br />

4.5.1.3 CLEAR CHANNEL TRANSMITTER (transparent signaling)......................... 4-9<br />

4.5.1.4 CLEAR CHANNEL RECEIVER ....................................................................... 4-9<br />

4.5.1.5 TRUNK IN Path Test.......................................................................................... 4-9<br />

4.5.1.6 SIGN Loop Back Test......................................................................................... 4-9<br />

4.5.2 AUXC ONLINE BIT ........................................................................................ 4-10<br />

4.5.2.1 DSP TEST......................................................................................................... 4-10<br />

4.5.2.2 PPI TEST .......................................................................................................... 4-10<br />

4.5.2.3 PEB TX TEST .................................................................................................. 4-10<br />

4.5.2.4 PEB RX TEST .................................................................................................. 4-10<br />

4.5.2.5 AUXC 188EC ONLINE EPROM CHECK SUM............................................. 4-10<br />

4.5.2.6 AUXC 188EC ONLINE FLASH CHECK SUM.............................................. 4-10<br />

4.5.2.7 AUXC 188EC ONLINE RAM CHECK........................................................... 4-10<br />

4.5.2.8 AUXC ONLINE INTERRUPT TEST .............................................................. 4-10<br />

4.5.2.9 AUXC 188EC ONLINE TIMER TEST............................................................ 4-10<br />

4.5.3 AUXC 188EC ONLINE HDLC TEST ............................................................. 4-11<br />

4.5.3.1 AUXC 188EC ONLINE DMA TEST............................................................... 4-11<br />

4.5.3.2 AUXC 188C ONLINE PORT TEST ................................................................ 4-11<br />

4.5.4 SCPU 188EC ONLINE BIT.............................................................................. 4-12<br />

4.5.4.1 SCPU ONLINE EPROM CHECK SUM .......................................................... 4-12<br />

4.5.4.2 SCPU ONLINE FLASH CHECK SUM ........................................................... 4-12<br />

4.5.4.3 SCPU ONLINE RAM CHECK ........................................................................ 4-12<br />

4.5.4.4 SCPU ONLINE INTERRUPT TEST................................................................ 4-12<br />

4.5.4.5 SCPU ONLINE TIMER TEST ......................................................................... 4-12<br />

4.5.4.6 SCPU ONLINE HDLC TEST........................................................................... 4-12<br />

4.5.4.7 SCPU ONLINE DMA TEST ............................................................................ 4-12<br />

4.5.4.8 SCPU ONLINE PORT TEST ........................................................................... 4-12<br />

4.5.5 BMCT ONLINE BIT ........................................................................................ 4-13<br />

4.5.5.1 GENERAL ........................................................................................................ 4-13<br />

4.5.5.2 TEST CIRCUIT ................................................................................................ 4-13<br />

4.5.5.3 CONTROL MEMORIES WRITE READ: ....................................................... 4-13<br />

4.5.5.4 BRT BMCT TS0:.............................................................................................. 4-13<br />

4.5.5.5 BMRT BMCT BARKER:................................................................................. 4-13<br />

4.5.5.6 FAX OUT & VBR CONTROL MEMORY: .................................................... 4-13<br />

92050003-02 iii

Table of Contents<br />

Section Description Page<br />

4.5.5.7 BCMODT#N TS0 ............................................................................................. 4-13<br />

4.5.5.8 BMCT ONLINE EPROM CHECK SUM......................................................... 4-13<br />

4.5.5.9 BMCT ONLINE RAM CHECK ....................................................................... 4-13<br />

4.5.5.10 BMCT ONLINE FLASH CHECK SUM.......................................................... 4-13<br />

4.5.5.11 BMCT ONLINE INTERRUPT TEST .............................................................. 4-14<br />

4.5.5.12 BMCT ONLINE TIMER TEST........................................................................ 4-14<br />

4.5.5.13 BMCT ONLINE HDLC TEST ......................................................................... 4-14<br />

4.5.5.14 BMCT ONLINE DMA TEST........................................................................... 4-14<br />

4.5.5.15 BMCT ONLINE PORT TEST.......................................................................... 4-14<br />

4.5.6 BMCR CPU ONLINE TEST ............................................................................ 4-15<br />

4.5.6.1 GENERAL ........................................................................................................ 4-15<br />

4.5.6.2 CONTROL MEMORIES WRITE READ ........................................................ 4-15<br />

4.5.6.3 BCBSR#N TS0 ................................................................................................. 4-15<br />

4.5.6.4 BCMDR#N TS0................................................................................................ 4-15<br />

4.5.6.5 FAXBSR#N TS0............................................................................................... 4-15<br />

4.5.6.6 BMCR ONLINE EPROM CHECK SUM......................................................... 4-15<br />

4.5.6.7 BMCR ONLINE RAM CHECK....................................................................... 4-15<br />

4.5.6.8 BMCR ONLINE FLASH CHECK SUM.......................................................... 4-15<br />

4.5.6.9 BMCR ONLINE INTERRUPT TEST.............................................................. 4-15<br />

4.5.6.10 BMCR ONLINE TIMER TEST ....................................................................... 4-16<br />

4.5.6.11 BMCR ONLINE HDLC TEST ......................................................................... 4-16<br />

4.5.6.12 BMCR ONLINE DMA TEST........................................................................... 4-16<br />

4.5.6.13 BMCR ONLINE PORT TEST.......................................................................... 4-16<br />

4.5.7 CKSL ONLINE BIT SPECIFICATIONS......................................................... 4-17<br />

4.5.7.1 PPI DATA BUS TEST...................................................................................... 4-17<br />

4.5.7.2 CKSL 12V TEST.............................................................................................. 4-17<br />

4.5.7.3 PLL LOCK TEST ............................................................................................. 4-17<br />

4.5.7.4 TIMING TEST.................................................................................................. 4-17<br />

4.5.8 XDSP ONLINE BIT (SDSP/TDSP/RDSP) ...................................................... 4-18<br />

4.5.8.1 GENERAL ........................................................................................................ 4-18<br />

4.5.8.2 SDSP ODD CELL TEST .................................................................................. 4-18<br />

4.5.8.3 XDSP HDLC PORT ......................................................................................... 4-18<br />

4.5.8.4 XDSP DSP_RES1 PORT.................................................................................. 4-18<br />

4.5.8.5 XDSP DSP_RES2 PORT.................................................................................. 4-18<br />

4.5.8.6 XDSP BS CM DATA TEST............................................................................. 4-18<br />

4.5.8.7 XDSP DSP CELL 0-15 TEST .......................................................................... 4-18<br />

4.5.8.8 188EC ONLINE EPROM CHECK SUM......................................................... 4-18<br />

4.5.8.9 188EC ONLINE FLASH CHECK SUM .......................................................... 4-18<br />

4.5.8.10 188EC ONLINE RAM CHECK ....................................................................... 4-19<br />

4.5.8.11 188EC ONLINE INTERRUPT TEST .............................................................. 4-19<br />

4.5.8.12 188EC ONLINE TIMER TEST........................................................................ 4-19<br />

4.5.8.13 188EC ONLINE HDLC TEST ......................................................................... 4-19<br />

4.5.8.14 188EC ONLINE DMA TEST........................................................................... 4-19<br />

4.5.8.15 188C ONLINE PORT TEST............................................................................. 4-19<br />

4.5.8.16 TDSP CELL TEST ........................................................................................... 4-19<br />

4.5.8.17 FDSP CELL TEST............................................................................................ 4-19<br />

4.5.8.18 RDSP ODD CELLS TEST ............................................................................... 4-20<br />

iv 92050003-02

Table of Contents<br />

Section Description Page<br />

4.5.9 XCPU ONLINE TEST...................................................................................... 4-21<br />

4.5.9.1 XCPU ONLINE EPROM CHECK SUM ......................................................... 4-21<br />

4.5.9.2 XCPU ONLINE RAM CHECK........................................................................ 4-21<br />

4.5.9.3 XCPU ONLINE FLASH CHECK SUM........................................................... 4-21<br />

4.5.9.4 XCPU ONLINE INTERRUPT TEST............................................................... 4-21<br />

4.5.9.5 XCPU ONLINE TIMER TEST ........................................................................ 4-21<br />

4.5.9.6 XCPU ONLINE HDLC TEST.......................................................................... 4-21<br />

4.5.9.7 XCPU ONLINE DMA TEST ........................................................................... 4-21<br />

4.5.9.8 XCPU ONLINE PORT TEST........................................................................... 4-21<br />

4.5.10 OMCP ONLINE TEST ..................................................................................... 4-22<br />

4.5.10.1 OMCP ONLINE EPROM CHECK SUM......................................................... 4-22<br />

4.5.10.2 OMCP ONLINE RAM CHECK ....................................................................... 4-22<br />

4.5.10.3 OMCP ONLINE FLASH CHECK SUM.......................................................... 4-22<br />

4.5.10.4 OMCP ONLINE INTERRUPT TEST .............................................................. 4-22<br />

4.5.10.5 OMCP ONLINE TIMER TEST........................................................................ 4-22<br />

4.5.10.6 OMCP ONLINE HDLC TEST ......................................................................... 4-22<br />

4.5.10.7 OMCP ONLINE DMA TEST........................................................................... 4-22<br />

4.5.10.8 OMCP ONLINE LAN CONTROLLER TEST................................................. 4-22<br />

4.5.10.9 OMCP ONLINE REAL TIME CLOCK TEST ................................................ 4-22<br />

4.5.10.10 OMCP ONLINE POWER FAILURE TEST .................................................... 4-23<br />

4.5.10.11 OMCP ONLINE PORT TEST.......................................................................... 4-23<br />

4.5.11 DSIT TEST DESCRIPTION............................................................................. 4-24<br />

4.5.11.1 GENERAL ........................................................................................................ 4-24<br />

4.5.11.2 DSIT T_PPI TEST ............................................................................................ 4-24<br />

4.5.11.3 DSIT XILINX TEST......................................................................................... 4-24<br />

4.5.11.4 DSIT 12 TEST .................................................................................................. 4-24<br />

4.5.11.5 DSIT PLL TEST ............................................................................................... 4-24<br />

4.5.11.6 ACFA TEST (Alarm Simulation) ..................................................................... 4-24<br />

4.5.11.7 TS0 PATTERN GENERATOR TEST ............................................................. 4-24<br />

4.5.11.8 DSIT INPUT BITSTREAMS TEST................................................................. 4-24<br />

4.5.11.9 DSIT ENC2BC MATRIX TEST ...................................................................... 4-24<br />

4.5.12 DSIT ENC2BC MATRIX INPUT BITSTREAMS BIT................................... 4-25<br />

4.5.12.1 DSIT MODE MATRIX TEST.......................................................................... 4-25<br />

4.5.12.2 DSIT MODE MATRIX INPUT BS TEST (TS0 TEST) .................................. 4-25<br />

4.5.12.3 DSIT DMUX CM TEST................................................................................... 4-25<br />

4.5.12.4 DSIT TDSI1 MATRIX TEST........................................................................... 4-25<br />

4.5.12.5 DSIT TDSI2 MATRIX TEST........................................................................... 4-25<br />

4.5.12.6 DSIT SHORT DELAY MEMORY TEST........................................................ 4-25<br />

4.5.12.7 DSIT LONG DELAY MEMORY TEST.......................................................... 4-25<br />

4.5.12.8 DSIT SIGNAL GENERATOR TEST............................................................... 4-25<br />

4.5.12.9 DSIT FPD (FAX PATTERN DETECTOR) TEST .......................................... 4-25<br />

4.5.12.10 DSIT SMAT TS0 TEST ................................................................................... 4-25<br />

4.5.13 ADPC ONLINE GENERIC DESCRIPTION ................................................... 4-26<br />

4.5.13.1 DPR Test ........................................................................................................... 4-26<br />

4.5.13.2 Output Ports Test .............................................................................................. 4-26<br />

4.5.13.3 PLL Lock Test................................................................................................... 4-26<br />

4.5.13.4 Test For The Codecs BIT Machine................................................................... 4-26<br />

92050003-02 v

Table of Contents<br />

Section Description Page<br />

4.5.13.5 Codecs Built-in Test.......................................................................................... 4-26<br />

4.5.13.6 ADPC Bitstream Test (TS0 Test) ..................................................................... 4-27<br />

4.5.14 QDLI ONLINE BIT DESCRIPTION ............................................................... 4-28<br />

4.5.14.1 GENERAL ........................................................................................................ 4-28<br />

4.5.14.2 PPI TEST .......................................................................................................... 4-28<br />

4.5.14.3 QDLI ACFA DATA BUS TEST ...................................................................... 4-28<br />

4.5.14.4 QDLI Xilinx REGISTERS TEST ..................................................................... 4-28<br />

4.5.14.5 QDLI LIU OSL TEST....................................................................................... 4-28<br />

4.5.14.6 QDLI ACFA PARITY CHECK........................................................................ 4-28<br />

4.5.14.7 QDLI LOCAL TS0 PATTERN GENERATOR TEST..................................... 4-28<br />

4.5.14.8 QDLI OUTPUT BITSTREAM TESTS ............................................................ 4-28<br />

4.5.14.9 QDLI INPUT BITSTREAM TEST .................................................................. 4-28<br />

4.5.14.10 QDLI LOOP BACK TEST ............................................................................... 4-28<br />

4.5.15 RDSW TEST..................................................................................................... 4-30<br />

4.5.16 TSDF ONLINE BIT DESCRIPTION ............................................................... 4-31<br />

4.5.16.1 GENERAL ........................................................................................................ 4-31<br />

4.5.16.2 TSDF PPI TEST................................................................................................ 4-31<br />

4.5.16.3 TSDF ACFA TEST (ALARM SIMULATION)............................................... 4-31<br />

4.5.16.4 TSDF LOCAL TS0 GENERATOR TEST ....................................................... 4-31<br />

4.5.16.5 TSDF MATRIX TEST DESCRIPTION........................................................... 4-32<br />

4.5.16.6 TSDF MATRIX SYNC TEST.......................................................................... 4-32<br />

4.5.16.7 TSDF MATRIX CM TEST .............................................................................. 4-32<br />

4.5.16.8 TSDF MATRIX SWITCH TEST ..................................................................... 4-32<br />

4.5.16.9 TSDF MATRIX INPUT BS TEST ................................................................... 4-32<br />

4.5.16.10 TSDF MATRIX DEVICES .............................................................................. 4-32<br />

4.5.17 DSIR ONLINE BIT DESCRIPTION................................................................ 4-33<br />

4.5.17.1 GENERAL ........................................................................................................ 4-33<br />

4.5.17.2 DSIR R_PPI TEST............................................................................................ 4-33<br />

4.5.17.3 DSIR XILINX TEST ........................................................................................ 4-33<br />

4.5.17.4 DSIR 12 TEST .................................................................................................. 4-33<br />

4.5.17.5 DSIR PLL TEST ............................................................................................... 4-33<br />

4.5.17.6 ACFA TEST (Alarm Simulation) ..................................................................... 4-33<br />

4.5.17.7 TS0 PATTERN GENERATOR TEST ............................................................. 4-33<br />

4.5.17.8 DSIR INPUT BITSTREAMS TEST................................................................. 4-33<br />

4.5.17.9 DSIR RDSI MATRIX TEST ............................................................................ 4-33<br />

4.5.17.10 DSIR MDSW MATRIX TEST......................................................................... 4-33<br />

4.5.17.11 DSIR MDSW MATRIX TEST INPUT BITSTREAMS TEST........................ 4-34<br />

4.5.17.12 DSIR INLV MATRIX TEST............................................................................ 4-34<br />

4.5.17.13 DSIR INLV MATRIX INPUT BS TEST (TS0 TEST) .................................... 4-34<br />

4.5.17.14 DSIR RDSP INPUT BS TEST (RDSP EVEN CELL TEST)........................... 4-34<br />

4.5.17.15 DSIR ADPC-RX INPUT BITSTREAMS TEST .............................................. 4-34<br />

4.5.17.16 DSIR TSDF INPUT BITSTREAMS TEST...................................................... 4-34<br />

4.5.17.17 DSIR “TEST-DSP” TEST ................................................................................ 4-34<br />

4.6 BUILT-IN TEST DIAGNOSTICS.................................................................... 4-35<br />

vi 92050003-02

Table of Contents<br />

Section Description Page<br />

5 JUMPER SETTINGS .......................................................................................5-1<br />

5.1 <strong>DTX</strong> - <strong>360</strong> TERMINAL, CARD LAYOUT ....................................................... 5-1<br />

5.2 <strong>DTX</strong> - <strong>360</strong>C COMPACT TERMINAL, CARD LAYOUT ................................ 5-1<br />

5.3 <strong>DTX</strong> - <strong>360</strong> TERMINAL, LIST OF CARD JUMPER SETTINGS..................... 5-2<br />

5.4 AUXC ................................................................................................................. 5-3<br />

5.4.1 AUXC Jumper Settings....................................................................................... 5-3<br />

5.4.2 AUXC Hard Wired ............................................................................................. 5-3<br />

5.4.3 AUXC Location of Jumpers ............................................................................... 5-3<br />

5.5 ADPC & ADPX .................................................................................................. 5-4<br />

5.5.1 ADPC & ADPX Jumper Settings - None............................................................ 5-4<br />

5.5.2 ADPC & ADPX Hard Wired .............................................................................. 5-4<br />

5.5.3 ADPC & ADPX Location of Jumpers ................................................................ 5-4<br />

5.6 CPU..................................................................................................................... 5-5<br />

5.6.1 CPU Jumper Settings .......................................................................................... 5-5<br />

5.6.2 CPU Hard Wired................................................................................................. 5-5<br />

5.6.3 CPU DIP Switch (U72) Settings ......................................................................... 5-5<br />

5.6.4 CPU Location of Jumpers and DIP Switches ..................................................... 5-5<br />

5.7 OMCP ................................................................................................................. 5-6<br />

5.7.1 OMCP Jumper Settings....................................................................................... 5-6<br />

5.7.2 OMCP Hard Wired ............................................................................................. 5-6<br />

5.7.3 OMCP DIP Switch (U51) Settings ..................................................................... 5-6<br />

5.7.4 OMCP Location of Jumpers and DIP Switches.................................................. 5-6<br />

5.8 BPIF/1 ................................................................................................................. 5-7<br />

5.8.1 BPIF /1 Jumper Settings...................................................................................... 5-7<br />

5.8.2 BPIF /1 Hard Wired - None ................................................................................ 5-7<br />

5.8.3 BPIF /1 Location of Jumpers and DIP Switches................................................. 5-7<br />

5.8.4 BMCT ................................................................................................................. 5-7<br />

5.8.5 BMCT Jumper Settings....................................................................................... 5-7<br />

5.8.6 BMCT Hard Wired - None ................................................................................. 5-8<br />

5.8.7 BMCT DIP Switch SW1 Settings....................................................................... 5-8<br />

5.8.8 BMCT Location of Jumpers and DIP Switches.................................................. 5-8<br />

5.8.9 DSP ..................................................................................................................... 5-8<br />

5.8.10 DSP Jumper Settings........................................................................................... 5-8<br />

5.8.11 DSP Hard Wired - None ..................................................................................... 5-8<br />

5.8.12 DSP DIP Switch (U102) Settings ....................................................................... 5-9<br />

5.8.13 DSP Location of Jumpers and DIP Switches...................................................... 5-9<br />

5.9 RDSW ............................................................................................................... 5-10<br />

5.9.1 RDSW Jumper Settings..................................................................................... 5-10<br />

5.9.2 RDSW Hard Wired - None ............................................................................... 5-10<br />

5.9.3 RDSW Location of Jumpers and DIP Switches................................................ 5-10<br />

5.10 QDLI ................................................................................................................. 5-11<br />

5.10.1 QDLI Jumper Settings....................................................................................... 5-11<br />

5.10.2 QDLI Hard Wired - None ................................................................................. 5-12<br />

5.10.3 QDLI DIP Switch (U43) Settings ..................................................................... 5-12<br />

5.10.4 QDLI Location of Jumpers and DIP Switches.................................................. 5-12<br />

5.10.5 QDLI Rev. E Jumper Settings........................................................................... 5-13<br />

92050003-02 vii

Table of Contents<br />

Section Description Page<br />

5.10.6 QDLI REV. E Hard Wired................................................................................ 5-14<br />

5.10.7 QDLI REV.-E DIP Switch (U75) Settings........................................................ 5-14<br />

5.10.8 QDLI REV.-E Location of Jumpers and DIP Switches .................................... 5-14<br />

5.11 CKSL................................................................................................................. 5-15<br />

5.11.1 CKSL Jumper Settings...................................................................................... 5-15<br />

5.11.2 CKSL Hard Wired ............................................................................................ 5-15<br />

5.11.3 CKSL Location of Jumpers............................................................................... 5-15<br />

5.12 BPIF/0 ............................................................................................................... 5-16<br />

5.12.1 BPIF /0 Jumper Settings.................................................................................... 5-16<br />

5.12.2 BPIF /0 Hard Wired - None .............................................................................. 5-16<br />

5.12.3 BPIF /0 Location of Jumpers ............................................................................ 5-16<br />

5.13 SIGN & SIGN/L *............................................................................................. 5-17<br />

5.13.1 SIGN Jumper Settings....................................................................................... 5-17<br />

5.13.2 SIGN Hard Wired - None.................................................................................. 5-17<br />

5.13.3 SIGN Location of Jumpers................................................................................ 5-17<br />

5.14 TSDF................................................................................................................. 5-18<br />

5.14.1 TSDF Jumper Settings - None .......................................................................... 5-18<br />

5.14.2 TSDF Hard Wired............................................................................................. 5-18<br />

5.14.3 TSDF Location of Jumpers............................................................................... 5-18<br />

5.15 BPIF/2 ............................................................................................................... 5-19<br />

5.15.1 BPIF /2 Jumper Settings.................................................................................... 5-19<br />

5.15.2 BPIF /2 Hard Wired - None .............................................................................. 5-19<br />

5.15.3 BPIF /2 Location of Jumpers ............................................................................ 5-19<br />

5.16 BMCR ............................................................................................................... 5-20<br />

5.16.1 BMCR Jumper Settings..................................................................................... 5-20<br />

5.16.2 BMCR Hard Wired - None ............................................................................... 5-20<br />

5.16.3 BMCR DIP Switch (SW1) Settings .................................................................. 5-20<br />

5.16.4 BMCR Location of Jumpers and DIP Switches................................................ 5-20<br />

5.17 BPIF/3 ............................................................................................................... 5-21<br />

5.17.1 BPIF /3 Jumper Settings.................................................................................... 5-21<br />

5.17.2 BPIF /3 Hard Wired - None .............................................................................. 5-21<br />

5.17.3 BPIF /3 Location of Jumpers and DIP Switches............................................... 5-21<br />

5.18 GDSP................................................................................................................. 5-22<br />

5.18.1 GDSP Jumper Settings...................................................................................... 5-22<br />

5.18.2 GDSP Hard Wired - None................................................................................ 5-22<br />

5.18.3 GDSP DIP Switch (U102) Settings................................................................... 5-22<br />

5.18.4 GDSP Location of Jumpers and DIP Switches................................................. 5-22<br />

5.19 DSIR /L ............................................................................................................. 5-23<br />

5.19.1 DSIR /L Jumper Settings .................................................................................. 5-23<br />

5.19.2 DSIR /L Hard Wired - None ............................................................................. 5-23<br />

5.19.3 DSIR /L Location of Jumpers ........................................................................... 5-23<br />

5.20 CPU /L .............................................................................................................. 5-24<br />

5.20.1 CPU /L Jumper Settings.................................................................................... 5-24<br />

5.20.2 CPU /L DIP Switch (U61) Settings .................................................................. 5-24<br />

5.20.3 CPU /L Location of Jumpers and DIP Switches............................................... 5-24<br />

5.21 OMCP /L........................................................................................................... 5-25<br />

5.21.1 OMCP /L Jumper Settings ................................................................................ 5-25<br />

viii 92050003-02

Table of Contents<br />

Section Description Page<br />

5.21.2 OMCP /L Hard Wired....................................................................................... 5-25<br />

5.21.3 OMCP /L DIP Switch (S2) Settings.................................................................. 5-25<br />

5.21.4 OMCP /L Location of Jumpers and DIP Switches ........................................... 5-25<br />

5.22 BMCT /L........................................................................................................... 5-26<br />

5.22.1 BMCT /L Jumper Settings ................................................................................ 5-26<br />

5.22.2 BMCT /L Hard Wired - None........................................................................... 5-26<br />

5.22.3 BMCT /L DIP Switch (SW2) Settings.............................................................. 5-27<br />

5.22.4 BMCT /L Location of Jumpers and DIP Switches ........................................... 5-27<br />

5.23 TSDF /L ............................................................................................................ 5-28<br />

5.23.1 TSDF /L On Circuit Wired (Hard Wired)......................................................... 5-28<br />

5.23.2 TSDF /L Location of Jumpers .......................................................................... 5-28<br />

5.24 BMCR /L........................................................................................................... 5-29<br />

5.24.1 BMCR /L Jumper Settings................................................................................ 5-29<br />

5.24.2 BMCR /L Hard Wired - None........................................................................... 5-29<br />

5.24.3 BMCR /L DIP Switch (SW2) Settings.............................................................. 5-29<br />

5.24.4 BMCR /L Location of Jumpers and DIP Switches ........................................... 5-29<br />

5.25 DSIT /L ............................................................................................................. 5-30<br />

5.25.1 DSIT /L Jumper Settings................................................................................... 5-30<br />

5.25.2 DSIT /L Hard Wired - None ............................................................................. 5-30<br />

5.25.3 DSIT /L Location of Jumpers ........................................................................... 5-30<br />

5.26 LDCH REV A ................................................................................................... 5-31<br />

5.26.1 LDCH Jumper Settings ..................................................................................... 5-31<br />

5.26.2 LDCH Hard Wired - None............................................................................... 5-31<br />

5.26.3 LDCH DIP Switch (S2) Settings....................................................................... 5-31<br />

5.26.4 LDCH Location of Jumpers............................................................................. 5-31<br />

5.27 LDCH REV B ................................................................................................... 5-32<br />

5.27.1 LDCH Jumper Settings ..................................................................................... 5-32<br />

5.27.2 LDCH Hard Wired - None................................................................................ 5-32<br />

5.27.3 LDCH DIP Switch (S2) Settings- None............................................................ 5-32<br />

5.27.4 LDCH Location of Jumpers.............................................................................. 5-32<br />

5.28 CCOM............................................................................................................... 5-33<br />

5.28.1 CCOM Cards Layout ........................................................................................ 5-33<br />

5.28.2 CCOM List of Card Jumper Settings............................................................... 5-33<br />

5.29 CRIO JUMPER SETTINGS ............................................................................. 5-34<br />

5.29.1 CRIO Hard Wired - None ................................................................................. 5-34<br />

5.29.2 CRIO Location of Jumpers ............................................................................... 5-34<br />

5.30 COCP ................................................................................................................ 5-35<br />

5.30.1 COCP Jumper Settings...................................................................................... 5-35<br />

5.30.2 COCP Hard Wired - None ................................................................................ 5-35<br />

5.30.3 COCP DIP Switch (SW2) Settings ................................................................... 5-35<br />

5.30.4 COCP Location of Jumpers and DIP Switches................................................. 5-35<br />

5.31 LCOM ............................................................................................................... 5-36<br />

5.31.1 LCOM Cards Layout......................................................................................... 5-36<br />

5.31.2 LCOM List of Card Jumper Settings ................................................................ 5-36<br />

5.32 SCOM ............................................................................................................... 5-36<br />

5.32.1 SCOM Cards Layout......................................................................................... 5-36<br />

5.33 LCMB ............................................................................................................... 5-37<br />

92050003-02 ix

Table of Contents<br />

Section Description Page<br />

5.33.1 LCMB Jumper Settings - None......................................................................... 5-37<br />

5.33.2 LCMB Hard Wired - None ............................................................................... 5-37<br />

5.33.3 LCMB DIP Switches (SW2 to SW6) Settings.................................................. 5-37<br />

5.34 LRMX ............................................................................................................... 5-38<br />

5.34.1 LRMX Jumper Settings (for 75Ω or 100Ω) ..................................................... 5-38<br />

5.34.2 LRMX Hard Wired - None ............................................................................... 5-38<br />

5.35 LRMX ............................................................................................................... 5-39<br />

5.35.1 LRMX Jumper Settings - None......................................................................... 5-39<br />

5.35.2 LRMX Hard Wired - for 120Ω ......................................................................... 5-39<br />

5.36 POWER SUPPLY............................................................................................. 5-40<br />

5.36.1 Power Supply Front Panel................................................................................. 5-40<br />

5.36.2 Power Supply Shelf........................................................................................... 5-40<br />

5.37 MBPU ............................................................................................................... 5-41<br />

5.37.1 MBPU Jumper Settings..................................................................................... 5-41<br />

5.37.2 MBPU Hard Wired - None ............................................................................... 5-41<br />

5.37.3 MBPU DIP Switch Settings .............................................................................. 5-41<br />

5.38 SUMMARY OF JUMPER AND SWITCH SETTINGS.................................. 5-42<br />

5.38.1 <strong>DTX</strong>-<strong>360</strong> Cards................................................................................................. 5-42<br />

5.38.2 Trunk & Bearer Impedance Configuration ....................................................... 5-44<br />

5.39 CCOM CARDS................................................................................................. 5-45<br />

5.40 LCOM CARDS................................................................................................. 5-46<br />

5.40.1 Trunk & Bearer Impedance Configuration ....................................................... 5-46<br />

5.41 POWER SUPPLY SHELF CARDS.................................................................. 5-47<br />

x 92050003-02

1<br />

GENERAL INFORMATION<br />

1.1 Introduction<br />

This manual identifies and explains maintenance concepts and features with regard to<br />

the <strong>DTX</strong>-<strong>360</strong> system. It outlines procedures to aid maintenance personnel with<br />

troubleshooting diagnosis, fault isolation, analysis, location, and correction.<br />

1.2 Static Awareness<br />

The <strong>DTX</strong>-<strong>360</strong> is designed for easy maintenance. Prior to maintenance, however, it<br />

should be noted that there are SPECIAL PRECAUTIONS that should be followed. It<br />

must be remembered that electronic devices are easily damaged by accidental<br />

introduction of ground or foreign voltages. Therefore, certain tools and test equipment<br />

commonly used on electro-mechanical systems should never be used on an electronic<br />

system. These include: battery buzzers, AC wire-wrap guns, electric soldering irons,<br />

guns, test picks, and test lamps. The following precautions must be observed:<br />

a. The <strong>DTX</strong>-<strong>360</strong> uses various metal oxide semiconductor (MOS) devices. Special<br />

handling of circuit cards which contain these devices is required. All personal<br />

tools, test equipment, and metal objects that come in contact with MOS devices<br />

must be electrically grounded. Any static or foreign voltage that is introduced<br />

into these devices may damage them permanently.<br />

b. DO NOT use tools or test equipment that draw an appreciable amount of current<br />

when attached to the system, such as test lamps and picks.<br />

c. DO NOT use tools or test equipment that could introduce foreign voltages into<br />

the system. For example, a battery-powered buzzer operates on only six or nine<br />

volts, but the voltage introduced across the buzzer coil when the magnetic field<br />

collapsed, can reach a momentary peak in excess of 100 volts, which can<br />

destroy solid- state devices.<br />

92050003-02 1-1

Section 1<br />

General<br />

<strong>DTX</strong>-<strong>360</strong><br />

<strong>Maintenance</strong><br />

1.3 Repair and Return<br />

Repair and return orders are issued to fix customer-owned material where service<br />

conditions do not require advance replacement or when least- costly service is desired.<br />

Generally, repair and return orders are mailed into the Material Service Center (MSC).<br />

The MSC will repair or replace (with repaired equipment) at our option, materials<br />

returned to our facilities.<br />

Note: If the system ceases to respond and/or operate (freezes), perform a Power Up Reset, verify<br />

return to proper operation and report immediately to ECI Telecom Field Engineering<br />

Department, specifying all relevant information, including History Report etc.<br />

1.3.1 Order Entry (normal shipping time)<br />

Repair of defective materials is handled by calling your MSC representative. You will be issued<br />

an Order Control Number that will serve as your Return Authorization (RA). Each package<br />

returned should be clearly identified with the RA number. A complete description of failure<br />

symptoms should be enclosed for each returned part (Fig. 1-1). Shipment to the MSC must be<br />

complete; do not send parts separately - some at one time and others at a later date. The MSC<br />

representative will prepare an order and file it in our receiving area pending arrival of the parts.<br />

Send the materials when the Return Authorization number is received.<br />

a) Typical Delivery Interval<br />

Thirty days should be allowed for our repair time starting from when your<br />

materials are received by the MSC and when the materials are shipped back.<br />

b) Invoicing Policy<br />

In-warranty repair service is done at no charge. You pay the freight inbound<br />

and we will pay the outbound freight. A "no charge" invoice will be sent to you<br />

to close your purchase order. Premium freight service, if requested, will be<br />

invoiced to the customer. All terms are net 30 days.<br />

Out-of-warranty invoices on repaired parts will generally be at 40% of full list<br />

price plus freight and taxes for equipment manufactured by ECI Telecom.<br />

However, major repairs will require cost estimates prior to completion of work.<br />

In this case, a price quotation will be supplied with the repair order confirmation<br />

prior to the start of repair work. All terms are net 30 days.<br />

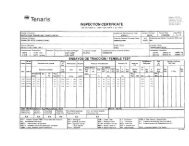

1.3.2 Terminal Malfunction Report<br />

In the rare event that a terminal ceases to operate, and is “stuck”, please do the<br />

following:<br />

• Perform a Power Up Reset<br />

• Verify return (of the terminal) to proper operation<br />

• Report to ECI Telecom as soon as possible - Please attach to your report all relevant<br />

information, such as History Reports.<br />

1-2 92050003-04

<strong>DTX</strong>-<strong>360</strong> Section 1<br />

<strong>Maintenance</strong><br />

General<br />

MSC LOCATIONS<br />

ECI Telecom Inc.<br />

927 Fern Street<br />

Altamonte Springs, FL 32701<br />

USA<br />

Tel: +1-407-331-5500<br />

Fax: +1-407-260-7136<br />

ECI Telecom GmbH<br />

Büropark Oberursel<br />

In der Au 27<br />

61440 Oberursel/Taunus<br />

Germany<br />

Tel: +49-6171-6209-0<br />

Fax: +49-6171-6209-88<br />

ECI Telecom (UK) Ltd.<br />

ISIS House, Reading Road<br />

Basingstoke<br />

Hampshire RG24 8TW England<br />

Tel: +44-1256-388000<br />

Fax: +44-1256-388180<br />

ECI Telecom (HK) Ltd.<br />

2806 China Resources Building<br />

26 Harbour Road, Wanchai<br />

Hong Kong<br />

Tel: +852-2824-4128<br />

Fax: +852-2802-4411<br />

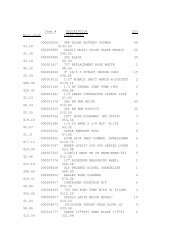

Description Serial No. Revision<br />

Descripción No. de serie Revisión<br />

Déscription Numéro de serie Révision<br />

Beschreibung Serial No. Revision<br />

Company Country City<br />

Compania Pais Ciudad<br />

Compagnie Pays Ville<br />

Gesellschaft Land Stadt<br />

System No. Site Date<br />

Sistema No. Ubicación Fecha<br />

Numéro de système Site Date<br />

Anlage Stelle Datum<br />

-------------------------------------------------------<br />

Description of Fault<br />

Descripción de la falla<br />

Déscription de panne<br />

Beschreibung der Fehler<br />

Name<br />

Nombre<br />

Nom<br />

Name<br />

Signature<br />

Firma<br />

Signature<br />

Unterschrift<br />

Figure 1-1. Malfunction Report<br />

92050003-04 1-3

Section 1<br />

General<br />

<strong>DTX</strong>-<strong>360</strong><br />

<strong>Maintenance</strong><br />

1.3.3 Order Entry (Emergency Order)<br />

Enter your emergency service orders by calling the MSC and providing us with your<br />

materials requirements; warranty status, air express shipping instructions, purchase<br />

order number and name of the person authorizing the purchase order.<br />

For service call your local agent.<br />

a) Method of Shipment<br />

High priority orders must be shipped via express/traceable means; regular orders<br />

may be shipped via any standard available carrier as directed by the customer.<br />

Shipment number and other delivery information may be obtained by calling the<br />

MSC. A return authorization and pre-addressed return labels are sent with all inwarranty<br />

shipments to facilitate your immediate return of the defective<br />

equipment.<br />

b) Invoicing Policy/Payment Terms<br />

1.3.4 Insurance Policy<br />

In-warranty shipments are not invoiced immediately to allow you 30 days from<br />

date of shipment to return the defective equipment. Out-of-warranty shipments<br />

are invoiced immediately.<br />

ECI Telecom will insure, at its own expense, materials shipped from ECI to customers.<br />

However, materials shipped from a customer's location to the MSC by the customer<br />

must be insured by the customer at his own expense.<br />

1.3.5 Substitutions and Modifications<br />

ECI reserves the right to make substitutions and modifications in the specifications of<br />

equipment designed by ECI that do not materially and adversely affect the performance<br />

of the equipment.<br />

1.3.6 Limitations of Liability<br />

Except as described under "Warranty", ECI shall not be liable for any liability, loss,<br />

damage, or expense relating to, arising out of, or in connection with the purchase,<br />

operation, use of licensing of equipment, software, and services. In no event shall ECI<br />

be liable for any SPECIAL, indirect, accidental, or consequential damages of any nature,<br />

regardless of whether ECI has been advised of the possibility of such damages.<br />

1-4 92050003-04

<strong>DTX</strong>-<strong>360</strong> Section 1<br />

<strong>Maintenance</strong><br />

General<br />

1.4 OPS Repair<br />

Repair of the "SUN" workstation used in the <strong>DTX</strong>-<strong>360</strong> system as an OPS is provided by<br />

your local "SUN" service office. Repair of defective OPS is handled by calling your<br />

MSC representative who will, in turn, arrange all the necessary procedures with the<br />

SUN service office.<br />

When all the procedures are arranged, your MSC representative will inform you about<br />

his arrangements. He also will inform you whether the repair is an in-warranty or out-ofwarranty<br />

service. After all the procedures have been done, you may send your defective<br />

OPS to the service center, following your MSC representative`s instructions.<br />

During the warranty period the OPS will be repaired at no charge by the local service<br />

office. During the out-of-warranty period you will be charged by the "SUN" service<br />

office for the OPS repair.<br />

1.5 Tasks Authorized for the User<br />

The user may perform the following repair and testing actions:<br />

❑ Connecting/disconnecting plug-in cables in the <strong>DTX</strong>-<strong>360</strong> system.<br />

❑ Extracting and inserting any PCB in the <strong>DTX</strong>-<strong>360</strong> card cage. With the exception of<br />

the line-interface cards, power supply units, and the redundant cards in the changeover<br />

matrix, all other cards should be removed only with the power switched OFF.<br />

Note: Use of a grounding strap is obligatory when a PCB is being extracted or<br />

inserted into the card cage.<br />

❑ Connecting and disconnecting DC-power (or AC) cable(s) (if applicable), to the<br />

<strong>DTX</strong>-<strong>360</strong> system and its peripheral equipment and/or operator station<br />

❑ Performing all test procedures described in this <strong>Manual</strong><br />

1.6 Handling of Electrostatically Sensitive Components<br />

The <strong>DTX</strong>-<strong>360</strong> uses MOS Semiconductor devices. Special handling precautions must be<br />

observed when handling PCBs. All personal tools, test equipment, and metal objects that<br />

come in contact with MOS devices must be electrically grounded. Any static and/or<br />

external voltage that is introduced into these devices can damage them permanently.<br />

Personnel handling PCBs should be grounded, using a grounding strap.<br />

92050003-04 1-5

Section 1<br />

General<br />

<strong>DTX</strong>-<strong>360</strong><br />

<strong>Maintenance</strong><br />

1.7 Handling Printed Circuit Boards<br />

❑ Do not rub, scratch, or scrape the printed wiring side with a sharp or abrasive object.<br />

❑ Do not expose to excessive heat or humidity.<br />

❑ Do not make any unauthorized modifications, repairs, or adjustments.<br />

❑ Do not use abrasive cleaners.<br />

❑ Do not mark the cards with any writing instrument that leaves a conductive deposit,<br />

such as lead pencil.<br />

❑ Do not stack PCBs on top of each other.<br />

❑ Do not store PCBs in an area that contains air pollutants (gas, smoke, dust, etc.) that<br />

may contain harmful agents. Store PCBs in anti-static conductive bags.<br />

1.8 Handling Peripheral Equipment and Terminals<br />

Several external devices may be connected to the <strong>DTX</strong>-<strong>360</strong> terminal:<br />

• An operator station (and printer)<br />

• A modem (for remote operation of the OPS)<br />

• An RS232 multiplexer (in a cluster configuration)<br />

All of the devices listed above are powered from the AC mains, and should not be<br />

handled with the cover removed.<br />

Use only lint-free cloth to clean the surfaces (cover or keyboard) of the devices.<br />

When servicing a <strong>DTX</strong>-<strong>360</strong> terminal, make sure that no tools are placed on the top of the<br />

terminal.<br />

Each cabinet may house several terminals. Special precautions must be taken when the<br />

top terminal is serviced in order to prevent tools, screws, washers, etc., from falling into<br />

the lower terminals.<br />

1-6 92050003-04

<strong>DTX</strong>-<strong>360</strong> Section 1<br />

<strong>Maintenance</strong><br />

General<br />

1.9 Handling the Operator Station<br />

The operator station is a fully featured workstation containing delicate peripherals and<br />

the following precautions should be observed:<br />

a) The system should be connected to a grounded (earthed) power outlet. Work<br />

stations which are not grounded do not work properly and can be a safety<br />

hazard. If the system is not properly grounded, abnormal program execution<br />

and problems in reading disks/diskettes may occur.<br />

b) The system should be isolated from sources of electrical noise and from devices<br />

that can cause excessive voltage variations. Some common sources of electrical<br />

noise are:<br />

• Air conditioners, fans, and large blowers<br />

• Transformers and alternators<br />

• Large electric motors<br />

• Radio and TV transmitters, and HF security devices<br />

c) The system should be placed in a relatively dust-free place.<br />

d) Air inlets should be kept clear of paper or other materials that may<br />

obstruct air flow.<br />

1.10 AC Power Outlets<br />

AC outlets are provided for the ETHERNET HUB and Modem. These power outlets are<br />

not provided with overload protection and appropriate care should be taken (external<br />

fusing or other overload protection procedures).<br />

92050003-04 1-7

Section 1<br />

General<br />

<strong>DTX</strong>-<strong>360</strong><br />

<strong>Maintenance</strong><br />

1.11 Detecting Card Malfunctions<br />

When a card malfunctions, the terminal’s self diagnostic process detects the malfunction<br />

and an indication is displayed on the AUXC Card Display LEDs.<br />

The indication contains the number of the malfunctioning card (1-52), according to its<br />

slot location in the terminal.<br />

For additional information regarding card malfunctions, please refer to report # 15 in the<br />

OMCP Monitor (in the OPS). Appendix A in the OPS-<strong>360</strong> User’s <strong>Manual</strong><br />

(Cat. # 92050005) contains detailed information about an OMCP Monitor session.<br />

In the Built-In Test Report Window, select option 3 (Online BIT) to view details of card<br />

malfunction.<br />

Note: In some cases, the cause of the malfunction may be a card other than the card that<br />

reports the problem, e.g., the TSDF card is indicated as malfunctioning when in fact it is<br />

the DSIR card. See next section for additional information.<br />

1.12 Detecting the Source of a Card Malfunction<br />

In some cases the card that announces a malfunction (on the AUXC LED panel) is not<br />

malfunctioning itself, but is affected by another card, that is actually the source of the<br />

problem.<br />

The following table contains a list of cards that announce malfunctions, the test that is<br />

performed on the cards and a list of cards which may be connected to the malfunction.<br />

Test Number Test Subject Testing Card Source of Indication<br />

0309-0316 PCMITR (0:7) TSDF DSIR<br />

0322-0329 PCMITR (0:7) TSDF DSIR<br />

0317 BRR (0:1) TSDF QDLI-BR<br />

0334 BRTBMCT (0:1) TSDF BMCT<br />

0335 BRTBMCT (0:1) TSDF BMCT<br />

0336 LVDSIT TSDF DSIT<br />

0337 VBR_DIS TSDF DSIT<br />

0338 PCMTCT0 TSDF QDLI-TR0<br />

0343-0344 PCMTCT(0:1) TSDF QDLI-TR0<br />

0345-0346 PCMTCT(2:3) TSDF QDLI-TR1<br />

0347-0348 PCMTCT(4:5) TSDF QDLI-TR2<br />

0349-0350 PCMTCT(6:7) TSDF QDLI-TR3<br />

1-8 92050003-04

<strong>DTX</strong>-<strong>360</strong> Section 1<br />

<strong>Maintenance</strong><br />

General<br />

Test Number Test Subject Testing Card Source of Indication<br />

0353 SIGT TSDF SIGN<br />

0354 CCTSTT TSDF DSIT<br />

0355 ORWT TSDF AUXC<br />

0359-0<strong>360</strong> PCMTCT(0:1) TSDF QDLI-TR0<br />

0359-0<strong>360</strong> PCMTCT(0:1) TSDF QDLI-TR0<br />

0361-0362 PCMTCT(2:3) TSDF QDLI-TR1<br />

0363-0364 PCMTCT(4:5) TSDF QDLI-TR2<br />

0365-0366 PCMTCT(6:7) TSDF QDLI-TR3<br />

0373-0374 BRR (0:1) TSDF QDLI-BR<br />

0383-0390 SIGTO (0:7) TSDF SIGN<br />

0607 PCMITT (0:7) DSIT TSDF<br />

0609 LDCT (0:2) DSIT LDCT (0-3)<br />

0617 LRET (0:3) DSIT TDSP0<br />

0612 BCMODT (0:3) DSIT BMCT<br />

0614 PCMITE (0:7) DSIT DSIR<br />

0709 BCBS(D)R (0:3)<br />

D (0:1)<br />

0710 BCBS(D)R (0:3)<br />

D (0:1)<br />

DSIR<br />

DSIR<br />

BMCR0<br />

BMCR1<br />

0711 FAXBSR (0:7) DSIR BMCR0,1<br />

0714 PCMDECR (0:2) DSIR ADPCR<br />

0715 PCMDECR (0:3) DSIR LDCR (0-3)<br />

1210-1225 Card 0 CELLS TDSP0 DSIT<br />

1210-1225 Card 1 CELLS TDSP1 DSIT<br />

1404 PCMENCT (0:1) ADPCT DSIT<br />

1405 ENCMODT (0:1) ADPCT DSIT<br />

1501-1515 card 0 CELLS LDCT0 DSIT<br />

1501-1515 card 1 CELLS LDCT1 DSIT<br />

1501-1515 card 2 CELLS LDCT2 DSIT<br />

92050003-04 1-9

Section 1<br />

General<br />

<strong>DTX</strong>-<strong>360</strong><br />

<strong>Maintenance</strong><br />

Test Number Test Subject Testing Card Source of Indication<br />

1501-1515 card 3 CELLS LDCT3 DSIT<br />

2208-2223 LREBSR (0:15) RDSP DSIR<br />

2401-2415 card 0 CELLS LDCR0 DSIR<br />

2401-2415 card 1 CELLS LDCR1 DSIR<br />

2401-2415 card 2 CELLS LDCR2 DSIR<br />

2401-2415 card 3 CELLS LDCR3 DSIR<br />

3208-3228-3223 card 0 CELLS SDSP0 DSIT<br />

3208-3228-3223 card 1 CELLS SDSP1 DSIT<br />

4015-4018 BCBST (0:3) BMCT TDSP<br />

4023-4026 LRET (0:3) BMCT TDSP0<br />

4023-4026 LRET (0:3) BMCT TDSP1<br />

5004-5011 PCMST (0:7) SIGN TSDF<br />

6035-6036 card 0 PCMTCR (0:1) QDLI-TR0 TSDF<br />

6035-6036 card 1 PCMTCR (2:3) QDLI-TR1 TSDF<br />

6035-6036 card 2 PCMTCR (4:5) QDLI-TR2 TSDF<br />

6035-6036 card 3 PCMTCR (6:7) QDLI-TR3 TSDF<br />

8027 card 0 BRTSDF0 BMCR0 TSDF<br />

8027 card 1 BRTSDF0 BMCR1 TSDF<br />

1.13 Card Removal Under Power<br />

Important: Before handling cards, make sure that you are connected to a proper antistatic<br />

device<br />

Before starting a procedure which might affect traffic, make sure that the terminal does<br />

not carry live traffic.<br />

The QDLI cards may be removed and replaced while the terminal is powered (ON).<br />

Before removing/replacing all other cards, please turn the terminal OFF.<br />

Note: Before turning a terminal OFF, make sure that it does not carry live traffic.<br />

1-10 92050003-04

<strong>DTX</strong>-<strong>360</strong> Section 1<br />

<strong>Maintenance</strong><br />

General<br />

1.14 OMCP/COCP Card Replacement<br />

Each OMCP/COCP card contains an Ethernet Chip with a unique MAC address.<br />

If you replace an OMCP card, you must make sure that the correct MAC and IP address<br />

are entered in the appropriate locations (files).<br />

The files are:<br />

❑ ethers<br />

❑ hosts<br />

❑ config<br />

❑ pofInfo_am<br />

Note: If the replacement OMCP/COCP card is an original Spare card, it is most likely<br />

that its MAC address is already in the /etc/ethers file.<br />

1.14.1 Modifying the ethers file<br />

Before you replace an OPMC/COCP card, do the following:<br />

1. In the OPS, open an xterm window.<br />