moving from system to circuit level in the design of digitial signal ...

moving from system to circuit level in the design of digitial signal ...

moving from system to circuit level in the design of digitial signal ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

OUTLINE<br />

MOVING FROM SYSTEM TO CIRCUIT LEVEL<br />

IN THE DESIGN OF DIGITIAL SIGNAL<br />

PROCESSING ALGORITHMS<br />

Sabih H. Gerez<br />

University <strong>of</strong> Twente & Bibix<br />

• Problem statement<br />

• Top-down <strong>design</strong><br />

• Models <strong>of</strong> computation<br />

• Data flow<br />

• Register-transfer <strong>level</strong> (RTL)<br />

• C-based hardware <strong>design</strong><br />

• Text-based and graphical <strong>design</strong> entry<br />

• Doma<strong>in</strong>-specific <strong>design</strong> languages<br />

• Arx, a doma<strong>in</strong>-specifid <strong>design</strong> language for RTL<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 2<br />

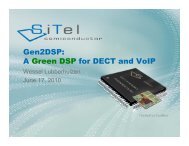

PROBLEM STATEMENT<br />

COMPLEXITY: DIVIDE AND CONQUER<br />

• We need <strong>to</strong> build a digital <strong>signal</strong> process<strong>in</strong>g (DSP)<br />

(sub)<strong>system</strong>.<br />

• The DSP algorithm is under development.<br />

• Fast <strong>system</strong>-<strong>level</strong> simulations are essential.<br />

• The DSP <strong>system</strong> will not be realized on programmable<br />

processors, but us<strong>in</strong>g dedicated hardware <strong>in</strong> an FPGA or<br />

ASIC technology.<br />

• How should <strong>the</strong> <strong>design</strong> be tackled?<br />

• Goal is <strong>to</strong> optimize:<br />

• Design time;<br />

• Design quality.<br />

abstract<br />

Abstraction <strong>level</strong>s<br />

concrete<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 3<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 4

MODELS OF COMPUTATION<br />

• Each abstraction <strong>level</strong> has a correspond<strong>in</strong>g model <strong>of</strong><br />

computation (MoC).<br />

• Examples <strong>of</strong> <strong>of</strong>ten encountered MoCs:<br />

• Synchronous data flow (SDF) for DSP algorithms.<br />

• Register transfers for synchronous logic.<br />

• Differential equations for currents and voltages <strong>in</strong> <strong>circuit</strong>s.<br />

SYNCHRONOUS DATA FLOW<br />

• Tokens carry data along edges <strong>of</strong> a graph.<br />

• Nodes perform computations and have fixed consumption<br />

and production rates.<br />

• “Untimed”, i.e. no direct relation <strong>to</strong> <strong>system</strong> clock <strong>in</strong><br />

implementation.<br />

• Suitable for <strong>the</strong> specification <strong>of</strong> multi-rate DSP algorithms.<br />

3<br />

3<br />

2<br />

2<br />

4<br />

4<br />

Lee, E.A. and D.G. Messerschmitt, ”Synchronous Data Flow”,<br />

Proceed<strong>in</strong>gs <strong>of</strong> <strong>the</strong> IEEE, Vol. 75(9), pp 1235–1245, (September 1987).<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 5<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 6<br />

DATA-FLOW GRAPH EXAMPLE<br />

REGISTER-TRANSFER LEVEL DESIGN<br />

T 0 T 0<br />

T 0<br />

= delay element<br />

= FIFO with length 1<br />

• Characterized by state<br />

updates only on clock edge.<br />

• Descriptions are called clockcycle<br />

true.<br />

• Often coded <strong>in</strong> VHDL (or<br />

Verilog).<br />

• Specification <strong>of</strong> RTL <strong>in</strong> VHDL<br />

requires identification <strong>of</strong><br />

language subset and cod<strong>in</strong>g<br />

style.<br />

• VHDL slow <strong>to</strong> simulate (eventdriven<br />

model).<br />

Primary<br />

<strong>in</strong>puts<br />

registers<br />

Comb.<br />

logic<br />

Primary<br />

outputs<br />

Second-order IIR filter<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 7<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 8

IMPLEMENTATION IN TOOLS: TEXT OR GRAPHICS?<br />

GENERIC VS. DOMAIN-SPECIFIC LANGUAGES<br />

T 0<br />

• Consider SDF:<br />

• It is possible <strong>to</strong> use a general language as C for cod<strong>in</strong>g <strong>in</strong><br />

• Tool based on graphical <strong>design</strong> entry is e.g. Synopsys System Studio.<br />

“data flow style” or “register-transfer style.<br />

• Example <strong>of</strong> doma<strong>in</strong>-specific language for data flow is Silage:<br />

• Example <strong>of</strong> RTL <strong>in</strong> C:<br />

• Voluntarily stick <strong>to</strong> s<strong>in</strong>gle-assignment code.<br />

y = b0*x + z2@1<br />

• Use static variables for registers and read <strong>the</strong>se values before writ<strong>in</strong>g<br />

z2 = a1*y + b1*x + z1@1<br />

<strong>the</strong>m.<br />

T_out sec(T_<strong>in</strong> x) {<br />

T 0<br />

z1 = a2*y + b2*x<br />

static T_reg z1 = 0; static T_reg z2 = 0; ...<br />

y = b0*x + z2;<br />

z2_nxt = a1*y + b1*x + z1; z1_nxt = a2*y + b2*x;<br />

z2 = z2_nxt; z1 = z1_nxt; // register update<br />

return(y);<br />

Hilf<strong>in</strong>ger, P.N., "A High-Level Language and Silicon Compiler for Digital Signal<br />

Process<strong>in</strong>g", Cus<strong>to</strong>m Integrated Circuit Conference, pp. 213-216, (1985).<br />

}<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 9<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 10<br />

PRACTICE IN SYSTEM-LEVEL-TO-RTL TRANSITION<br />

C-BASED HARDWARE DESIGN<br />

System<br />

Level<br />

RT Level<br />

abstract<br />

concrete<br />

System models<br />

<strong>of</strong>ten described <strong>in</strong><br />

C or Matlab<br />

Costly manual<br />

translation<br />

(months)<br />

Hardware models<br />

<strong>in</strong> VHDL<br />

• Arguments <strong>in</strong> favor <strong>of</strong> C-based <strong>design</strong>:<br />

• Everybody knows C; we don’t want <strong>to</strong> teach new languages.<br />

• Lots <strong>of</strong> legacy C code.<br />

• High execution speed.<br />

• Many commerical products based on translation <strong>from</strong><br />

C/C++/SystemC <strong>in</strong>clud<strong>in</strong>g:<br />

• Catapult (Men<strong>to</strong>r Graphics)<br />

• C-<strong>to</strong>-Silicon (Cadence)<br />

• Cyn<strong>the</strong>sizer (Forte Design Systems)<br />

• Synphony C Compiler (Synopsys, formerly Synfora PICO)<br />

• Au<strong>to</strong>Pilot (Xil<strong>in</strong>x, formerly Au<strong>to</strong>ESL)<br />

• CyberWorkBench (NEC System Technologies)<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 11<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 12

DISADVANTAGES OF C-BASED DESIGN<br />

• Arguments aga<strong>in</strong>st C-based <strong>design</strong>:<br />

• Hardware <strong>design</strong> requires a different style <strong>of</strong> th<strong>in</strong>k<strong>in</strong>g than s<strong>of</strong>tware<br />

<strong>design</strong>.<br />

• It takes time <strong>to</strong> learn <strong>the</strong> hardware-style <strong>of</strong> th<strong>in</strong>k<strong>in</strong>g, far longer than it<br />

takes <strong>to</strong> learn a new language.<br />

• It is an illusion <strong>to</strong> th<strong>in</strong>k that s<strong>of</strong>tware eng<strong>in</strong>eers will become good<br />

hardware eng<strong>in</strong>eers by <strong>the</strong> availability <strong>of</strong> a C-<strong>to</strong>-HDL converter.<br />

• C was never <strong>in</strong>vented with hardware <strong>in</strong> m<strong>in</strong>d:<br />

• C cannot express parallelism.<br />

• Many language constructs do not make sense <strong>in</strong> hardware.<br />

• One needs <strong>to</strong> stick <strong>to</strong> a specific language subset and cod<strong>in</strong>g style.<br />

Edwards, S.A., The Challenges <strong>of</strong> Syn<strong>the</strong>siz<strong>in</strong>g Hardware <strong>from</strong> C-Like<br />

Languages, IEEE Design and Test <strong>of</strong> Computers, pp. 375-385,<br />

(September/Oc<strong>to</strong>ber 2006).<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 13<br />

GRAPHICAL DESIGN ENTRY<br />

• Many solutions based on dedicated blocksets <strong>to</strong> be used <strong>in</strong><br />

Simul<strong>in</strong>k:<br />

• Mathwork’s own FPGA flow<br />

• Synphony Model Compiler (Synopsys)<br />

• Xil<strong>in</strong>x System Genera<strong>to</strong>r for DSP<br />

• Altera DSP Builder<br />

• Graphical <strong>design</strong> entry can be cumbersome compared <strong>to</strong><br />

text-based entry:<br />

• One does not always want <strong>to</strong> <strong>in</strong>stantiate an adder for every addition, a<br />

multiplexer for every if-statement, etc.<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 14<br />

DOMAIN-SPECIFIC DESIGN LANGUAGES<br />

ARX: A DOMAIN-SPECIFIC RTL LANGUAGE<br />

• All language constructs make sense <strong>in</strong> doma<strong>in</strong>:<br />

• Entire language is syn<strong>the</strong>sizable.<br />

• Designer does not need <strong>to</strong> bo<strong>the</strong>r about allowed subsets.<br />

• Straightforward language constructions:<br />

• Improve <strong>design</strong>er efficiency.<br />

• Lead <strong>to</strong> elegant <strong>design</strong>s.<br />

• Examples:<br />

• Bluespec<br />

• GEZEL<br />

Doma<strong>in</strong>-specific<br />

RTL language:<br />

Arx<br />

Functional<br />

Bit-true<br />

Bit-true and<br />

clock-cycle-true<br />

• One language (Arx) for multiple<br />

<strong>level</strong>s.<br />

• Developed at University <strong>of</strong> Twente.<br />

• Arx elim<strong>in</strong>ates manual translation<br />

<strong>from</strong> C <strong>to</strong> VHDL!<br />

• Correct by construction.<br />

C++<br />

genera<strong>to</strong>r<br />

VHDL<br />

genera<strong>to</strong>r<br />

Verification<br />

with C-based<br />

simulation<br />

RTL syn<strong>the</strong>sis<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 15<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 16

ARX DOMAIN<br />

ARX EXAMPLE<br />

• Design <strong>of</strong> ICs or FPGAs for <strong>signal</strong> process<strong>in</strong>g as e.g. found<br />

<strong>in</strong>:<br />

• Telecom<br />

• Image process<strong>in</strong>g<br />

• Multimedia<br />

• Defense<br />

• Space, astronomy<br />

Clock and reset are<br />

implicit.<br />

sum<br />

r<br />

• Key is <strong>to</strong> descend <strong>to</strong> RTL <strong>from</strong> <strong>system</strong>-<strong>level</strong> <strong>design</strong> and<br />

necessity for fast cycle-true and bit-true simulations:<br />

• C++ code generated by Arx is based on zero-delay simulation.<br />

• Event-driven simulation (with fac<strong>to</strong>r 100 overhead!) does not make<br />

sense when almost all <strong>signal</strong>s change <strong>in</strong> every clock cycle.<br />

data_<strong>in</strong><br />

clear<br />

data_out<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 17<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 18<br />

LANGAUGE FEATURES<br />

• Explicit dist<strong>in</strong>ction between wires and registers.<br />

• Implicit clock and reset.<br />

• Generic data types allow<strong>in</strong>g propagation <strong>of</strong> data types down<br />

hierarchy (e.g. float<strong>in</strong>g-po<strong>in</strong>t <strong>to</strong> fixed-po<strong>in</strong>t ref<strong>in</strong>ement).<br />

• Data types for DSP, especially fixed-po<strong>in</strong>t data types.<br />

• Support for overflow and quantization modes.<br />

• Efficient simulation <strong>of</strong> fixed-po<strong>in</strong>t data types.<br />

• Simple: can be learned <strong>in</strong> one day!<br />

ABOUT BIBIX<br />

• University <strong>of</strong> Twente (UT) sp<strong>in</strong>-<strong>of</strong>f<br />

• Supported by <strong>the</strong> UT Centre for Telematics and Information<br />

Technology (CTIT).<br />

• Received an STW Valorisation Grant Phase 1 for feasibility<br />

study and market research on Arx.<br />

• Received with HDL Works a Po<strong>in</strong>t-One Feasibility Project for<br />

research on <strong>the</strong> application <strong>of</strong> Arx <strong>to</strong> FPGA <strong>design</strong>.<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 19<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 20

ON-LINE FEATURES<br />

• Please visit:<br />

www.bibix.nl<br />

• The website gives access <strong>to</strong>:<br />

• On-l<strong>in</strong>e manual,<br />

• Web-based demonstration (upload Arx, download correspond<strong>in</strong>g C++<br />

and VHDL),<br />

• Questionnaire.<br />

• Feedback on Arx, requests for cooperation, very welcome.<br />

• Possibilities for free pilot <strong>design</strong>s.<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 21<br />

SUMMARY<br />

• Issues <strong>in</strong> <strong>mov<strong>in</strong>g</strong> <strong>from</strong> <strong>system</strong> <strong>level</strong> <strong>to</strong> RTL:<br />

• What MoC should be used when?<br />

• Generic or doma<strong>in</strong>-specific implementation language?<br />

• Textual or graphical <strong>design</strong> entry?<br />

• A doma<strong>in</strong>-specific language for <strong>the</strong> RTL MoC, e.g. Arx,<br />

bridges wall when descend<strong>in</strong>g <strong>from</strong> <strong>the</strong> <strong>system</strong> <strong>level</strong>.<br />

• Arx br<strong>in</strong>gs about that one source code generates:<br />

• C++-based simulation model optimized for simulation speed<br />

• VHDL code for syn<strong>the</strong>sis.<br />

• The Arx approach:<br />

• Saves manual recod<strong>in</strong>g time!<br />

• Is correct by construction!<br />

Bits & Chips Hardware Conference • June 9, 2011 • © Sabih H. Gerez 22