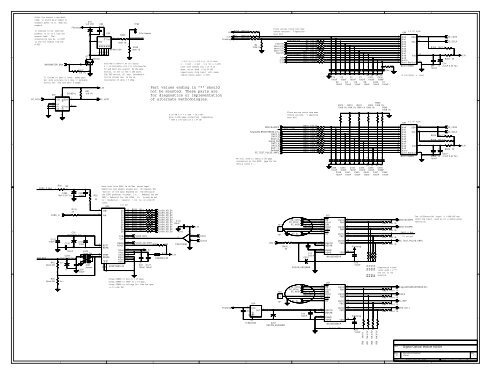

Schematic - Glacier - Lawrence Berkeley National Laboratory

Schematic - Glacier - Lawrence Berkeley National Laboratory

Schematic - Glacier - Lawrence Berkeley National Laboratory

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

1<br />

2<br />

1<br />

2<br />

A<br />

8<br />

4<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

S<br />

2<br />

2<br />

1<br />

5<br />

6<br />

7<br />

8<br />

1<br />

2<br />

1<br />

4<br />

2<br />

+<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

B<br />

C<br />

D<br />

E<br />

Since the sensor u ses about<br />

60mW, it would be p rudent to<br />

disable power to it when not<br />

C75<br />

1uF X7R C82<br />

TP60<br />

needed.<br />

5Vanalog<br />

110nF<br />

Place series resis tors near<br />

It remains to be seen how<br />

1<br />

R279 162K 1%<br />

remote sources. C apacitors<br />

0-2.5V span<br />

-5V<br />

prudent it is to f loat the<br />

U26<br />

2-Pin Header<br />

U68<br />

near ADC.<br />

R338<br />

ground lead. The<br />

3.3V<br />

R3 100K 1%<br />

1<br />

10<br />

alternative may be a P-FET<br />

BAROMETER<br />

Ain0<br />

SC_nCS5<br />

4 1 2<br />

R13 150K 1%<br />

5Vanalog<br />

2<br />

SDA<br />

Out<br />

3<br />

BAROMETER R5 10K 1%<br />

Ain1<br />

3<br />

9<br />

in the Vcc enable d by the<br />

Gnd<br />

SC_SCLK<br />

150K 1%<br />

R6 10K 1%<br />

N-FET.<br />

Imon+5V<br />

4<br />

Ain2 SCL<br />

R4<br />

R7 10K 1%<br />

5<br />

Ain3<br />

Imon+3.3V<br />

R339<br />

100K 1%<br />

R8 10K 1%<br />

Ain4<br />

Imon+2.5V<br />

6<br />

R104 10K 1%<br />

MPXA4115A 100K 1%<br />

R9 10K 1%<br />

Imon+1.8V<br />

7<br />

Ain5<br />

R10 10K 1%<br />

Imon-5V<br />

8<br />

Ain6<br />

DISC-OneSPE R11 10K 1%<br />

16<br />

Ain7<br />

12<br />

Q7<br />

R12 10K 1%<br />

Ain8 Vdd<br />

3.3V<br />

4 1.8V<br />

15<br />

4<br />

2N7002<br />

2.5V<br />

R142 10K 1%<br />

14<br />

Ain9<br />

R367 20<br />

-(-5/2.5)-(+3.3+2.5+1. 8)/4 =Vout<br />

R233 100K 1%<br />

13<br />

Ain10<br />

11<br />

3.3V<br />

Vout=Vs(0.009*P-0.09 5)+/-Error<br />

Ain11-RefGnd<br />

BAROMETER_ENA<br />

G<br />

2 - 0.825 - 0.625 - 0.4 50) = 0.100V<br />

C14<br />

P = 10.55555556+(111.111 1111*Vout/Vs)<br />

Lets just assume tha t if +5 is<br />

R1 MAX1139EEE<br />

C9 2.2uF 6.3V Tan<br />

5V and Baro are scaled by the same<br />

100nF<br />

R407<br />

gone, we're dead. T he 5V CPU<br />

100K 1%<br />

factor, so are in the s ame units.<br />

10K 1%<br />

supervisory chip input will cause<br />

The FET switch, Q7, may introduce a<br />

reboot below about 4.750V.<br />

(2.500/4096) x count<br />

TI claims to have a lower power part, little offset due to its on<br />

C10 C3 C5 C7 C373 C435<br />

but only accurate to 2 deg C (probably resistance of abou t 5 ohms.<br />

100nF 100nF 100nF 100nF 100nF 100NF<br />

within the -25C and abov e range)...<br />

C2 C4 C6 C8 C434 C1<br />

100nF 100nF 100nF 100nF 100nF 100nF<br />

SC_SCLK<br />

U55<br />

2<br />

7<br />

6<br />

5<br />

SCL<br />

A0<br />

A1<br />

A2<br />

Vdd<br />

GND<br />

SDA<br />

Tout<br />

DS1631U<br />

1<br />

3<br />

D<br />

R51<br />

10K 1%<br />

3.3V<br />

Vs<br />

NC<br />

NC<br />

NC<br />

NC<br />

NC<br />

SC_nCS7<br />

1 2<br />

Part values ending in "*" should<br />

not be mounted. These parts are<br />

for diagnostics or implementation<br />

of alternate methodologies.<br />

4.25 mW x 4 + 7.5mW = 24.5 mW<br />

plus 3.3mW when converting temperature<br />

+ 6mW x 10V/conv_ef f = 67 mW<br />

Place series resis tors near<br />

remote sources. C apacitors<br />

near ADC.<br />

R819 10K 1%<br />

DISC-MultiSPE<br />

1<br />

10<br />

FADC_0_Ref<br />

SC_nCS6<br />

R820 10K 1%<br />

2<br />

Ain0 SDA<br />

R821 150K 1%<br />

SingleLED-BRIGHTNESS-CTL<br />

3<br />

Ain1<br />

9<br />

R822 10K 1%<br />

Ain2 SCL<br />

SC_SCLK<br />

DAC0_A<br />

4<br />

DAC0_B<br />

R823 150K 1%<br />

5<br />

Ain3<br />

R824 10K 1%<br />

R825 10K 1%<br />

DAC0_C<br />

6<br />

Ain4<br />

R826 150K 1%<br />

Ain5<br />

Analog_Ref<br />

7<br />

R105 10K 1%<br />

DAC1_A<br />

R827 10K 1%<br />

8<br />

Ain6<br />

3 R828 150K 1%<br />

3<br />

DAC2_B<br />

16<br />

Ain7<br />

12<br />

3.3V<br />

R830 10K 1%<br />

DAC1_C<br />

15<br />

Ain8 Vdd<br />

R831 150K 1%<br />

Ain9<br />

Pedestal<br />

14<br />

R829 20<br />

FE_TEST_PULSE_AMPL<br />

R832 150K 1%<br />

13<br />

Ain10<br />

11<br />

Ain11-RefGnd<br />

C437<br />

MAX1139EEE<br />

C436 2.2uF 6.3V Tan<br />

We will need to assig n off page<br />

100nF<br />

connectors on the ATWD page for the<br />

DACx_y input s....<br />

R310<br />

100K 1%<br />

R313<br />

100K 1%<br />

R307<br />

100K 1%<br />

R314<br />

100K 1%<br />

R309<br />

100K 1%<br />

R308<br />

100K 1%<br />

C438 C440 C442 C444 C446 C448<br />

100nF 100nF 100nF 100nF 100nF 100NF<br />

C439 C441 C443 C445 C447 C449<br />

100nF 100nF 100nF 100nF 100nF 100nF<br />

U97<br />

0-2.5V span<br />

FADC_0_Ref<br />

R36 100<br />

1 2<br />

C385<br />

10uF 6.8V Tan<br />

C386<br />

100nF<br />

1 2<br />

R39<br />

20<br />

Note that this FADC is differ ential input.<br />

Amplifier and shaper stages are DC coupled. The<br />

'bottom' of the span depends on the setting of<br />

the ATWD pedestal voltage. I.e., Pedestal for the<br />

FADC = Pedestal for the ATWD. V+ in must be set<br />

to ( Vpedestal - (span/2) ) vol ts, or a few mV<br />

lower.<br />

100 mW<br />

U30<br />

R132<br />

9<br />

17 R436 100 1 2<br />

FLASH_AD_D0<br />

20<br />

VIN+<br />

D0<br />

18 R437 100 1 2<br />

FLASH_AD_D1<br />

FADC_In<br />

10<br />

D1<br />

19 R438 100 1 2<br />

VIN-<br />

D2<br />

FLASH_AD_D2<br />

20 R439 100 1 2<br />

U23<br />

The (differential input) 4 0 MHz ADC non<br />

D3<br />

FLASH_AD_D3<br />

21 R440 100 1 2<br />

FLASH_AD_D4<br />

SC_nCS2<br />

8<br />

3<br />

DISC-MultiSPE<br />

inverting input, used as th e center-scale<br />

D4<br />

22 R441 100 1 2<br />

FLASH_AD_D5<br />

C121<br />

SC_SCLK<br />

10<br />

CS OUTA<br />

2<br />

D5<br />

reference.<br />

25 R442 100 1 2<br />

100nF<br />

FLASH_AD_D6<br />

SC_MOSI<br />

9<br />

SCLK FBA<br />

R14 10K 1%<br />

D6<br />

26 R443 100 TP1<br />

DAC-DO0<br />

DIN<br />

1 2<br />

D7<br />

FLASH_AD_D7<br />

1 2<br />

3.3V<br />

12<br />

4<br />

DAC-UP0<br />

DISC-OneSPE<br />

27 R444 100 1 2<br />

D8<br />

FLASH_AD_D8<br />

13<br />

DOUT OUTB<br />

5<br />

2 28 R445 100 1 2<br />

1<br />

D9<br />

FLASH_AD_D9<br />

14<br />

UPO FBB<br />

R15 10K 1%<br />

2<br />

C26<br />

U12<br />

PDL<br />

FADC_0_Ref<br />

SC_CL<br />

7<br />

17<br />

10uF 6.8V Tan<br />

1<br />

OTR FLASH_NCO<br />

7<br />

CLKx2<br />

TP*<br />

CL OUTC<br />

16<br />

13<br />

2<br />

FBC<br />

R16 10K 1%<br />

5V output<br />

C125<br />

CLK<br />

8<br />

18<br />

100nF<br />

C124<br />

nCLKx2<br />

OUTD<br />

FE_TEST_PULSE_AMPL<br />

14<br />

C126<br />

FLASH_AD_STBY<br />

VR2.5<br />

15<br />

19<br />

100nF<br />

6<br />

PDWN<br />

2<br />

R262 39K FIN1018K8X<br />

REFCD FBD<br />

6<br />

R17 10K 1%<br />

REFT MODE<br />

5<br />

R405<br />

REFAB<br />

5Vanalog<br />

REFB<br />

24<br />

20<br />

DVdd<br />

2.5V<br />

11<br />

100nF JU28<br />

DGND<br />

7<br />

1<br />

20<br />

Open Ckt 4<br />

AVdd<br />

12<br />

B18<br />

C13<br />

AGND VDD<br />

C294<br />

VREF AVdd<br />

3.3V<br />

1 2 3<br />

23<br />

100nF<br />

ADC-REF<br />

1 2<br />

SENSE DGnd<br />

8<br />

LI0805D121R<br />

C270<br />

MAX5250BEAP<br />

10uF 6.8V Tan<br />

1 2<br />

AGnd<br />

11<br />

R45 Ra*<br />

1 2<br />

AGnd<br />

C15<br />

Open Ckt<br />

JU27<br />

C29 C127<br />

100nF<br />

AD9215BRU-65<br />

Jumper<br />

100nF 100nF<br />

OSCON_6SC6R8M<br />

Components w hose<br />

C295<br />

value ends i n "*"<br />

100nF<br />

are not to be<br />

mounted.<br />

NC<br />

NC<br />

15<br />

16<br />

R46<br />

Strap SENSE to Gnd fo r 2V Span.<br />

Open Ckt Ra*<br />

Strap SENSE to VREF fo r 1V span.<br />

U28<br />

Strap SENSE to Voltage Div ider for span<br />

=1.0(1+Ra/ Rb).<br />

SC_nCS3<br />

8<br />

3<br />

CS OUTA<br />

SingleLED-BRIGHTNESS-CTL<br />

SC_SCLK<br />

10<br />

2<br />

SC_MOSI<br />

9<br />

SCLK FBA<br />

R22 10K 0.1%<br />

TP2<br />

DAC-DO1 12<br />

DIN<br />

4<br />

DAC-UP1<br />

DOUT OUTB<br />

Clamp<br />

13<br />

5<br />

1<br />

14<br />

UPO FBB<br />

R23 10K 0.1%<br />

TP*<br />

SC_CL<br />

7<br />

PDL<br />

17<br />

CL OUTC<br />

FL_REF<br />

U24<br />

16<br />

FBC<br />

R24 10K 0.1%<br />

5Vanalog<br />

3<br />

18<br />

VCC<br />

OUTD<br />

DAC_Out_1<br />

1<br />

15<br />

19<br />

C12<br />

OUT<br />

REFCD FBD<br />

6<br />

R25 10K 0.1%<br />

REFAB<br />

+<br />

C16<br />

100nF*<br />

100nF<br />

11<br />

5Vanalog<br />

1 DGND<br />

1<br />

20<br />

1<br />

AGND VDD<br />

GND<br />

TLE2425ID<br />

C451<br />

OSCON_6SC6R8M<br />

MAX5250BEAP<br />

10 bit DAC<br />

C17<br />

100nF<br />

R26 10K 1%<br />

R18 10K 1%<br />

R19 10K 1%<br />

R20 10K 1%<br />

R21 10K 1%<br />

R27 10K 0.1%*<br />

R28 10K 0.1%*<br />

R29 10K 0.1%*<br />

Title<br />

Digital Optical Module AD/DA<br />

Size Document Number Rev<br />

C 1.1<br />

A<br />

B<br />

C<br />

D<br />

Friday, May 16, 2003<br />

Date: Sheet of 4 15<br />

E

1<br />

2<br />

1<br />

2<br />

5<br />

3<br />

5<br />

4<br />

3<br />

2<br />

7<br />

8<br />

4<br />

1<br />

A<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

5<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

5<br />

2<br />

1<br />

1<br />

2<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

5<br />

2<br />

5<br />

2<br />

1<br />

2<br />

1<br />

2<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

6<br />

1<br />

6<br />

1<br />

2<br />

7<br />

4<br />

5<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

5<br />

2<br />

S<br />

S<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

5<br />

2<br />

5<br />

2<br />

B<br />

C<br />

D<br />

E<br />

Nov 25, '0 2 GTP<br />

R278 20<br />

Name chang e to<br />

1 2<br />

5Vanalog<br />

eliminate<br />

C83<br />

naming con flict<br />

1 2<br />

Caution: The comparato rs are 5V<br />

Vref1 2<br />

C151<br />

parts that cannot be op erated from<br />

Per criterion established July 2002 (gtp&drn) the design goal for the<br />

10uF 6.8V Tan<br />

3.3V. Care must be take n to protect<br />

IceCube DOM is 200 PE = 1V into the ATWD dic tated by PMT saturation<br />

33pF NPO<br />

1 2<br />

TP70 the driven 3.3 V part.<br />

5Vanalog<br />

behavior. Namely, the PMT NEVER delivers mor e than about 2V, and is<br />

C154<br />

1<br />

2-Pin Header<br />

linear to about 1V into a 50 ohm load (100 oh m || back-termination).<br />

R348<br />

100nF<br />

U1<br />

R35 2400 51<br />

R351 2.2K<br />

R40<br />

DISC-MultiSPE<br />

1 2<br />

U2 MAX9013EUA<br />

2<br />

C409<br />

MSPE_Q<br />

5Vanalog<br />

1 2<br />

2<br />

7<br />

1 2<br />

R390 10uF 6.8V Tan<br />

C323<br />

R38 C355 + C371<br />

MSPE_QBar 3<br />

4 R352 51<br />

MSPE_QBar<br />

MultiSPE-C<br />

1 21 2<br />

10 10uF 6.8V Tan<br />

1 2<br />

3<br />

5Vanalog<br />

5<br />

-<br />

8<br />

47pF NPO<br />

1100nF<br />

5<br />

1 2<br />

Open Ckt<br />

Latch 5<br />

10<br />

Vref<br />

MSPE_Q<br />

5<br />

6<br />

7 R322 2 151<br />

MultiSPE<br />

C410<br />

1 2<br />

12<br />

1 2<br />

R75<br />

1 2<br />

C20<br />

Q8<br />

100<br />

SPE_QBar<br />

R353 51<br />

5Vanalog<br />

2 1<br />

10uF 6.8V Tan<br />

2N7002<br />

11<br />

10<br />

OneSPE-C<br />

Locate these amplifiers --><br />

100nF<br />

R47<br />

C25<br />

1 2<br />

G<br />

MultiSPE-nL<br />

15<br />

51 U43 100nF<br />

R32 20<br />

C21<br />

TP71<br />

close to the PMT signal<br />

U66<br />

1 2<br />

R349<br />

U3<br />

1<br />

3<br />

100nF<br />

2-Pin Header 2 1<br />

SPE_Q 14<br />

13 R354 51<br />

+<br />

input.<br />

Transmission line<br />

SPE_Q<br />

OneSPE<br />

3<br />

1 1 2<br />

2<br />

7<br />

R371<br />

+<br />

1<br />

1 2 4<br />

+ R355 10K 1%<br />

-<br />

FSTD3125M<br />

1 2 4<br />

51<br />

Vref<br />

3 -<br />

8 SPE_QBar<br />

2.2K<br />

R391<br />

-<br />

1 2<br />

R42<br />

AD8014RT<br />

100nF<br />

Latch 5<br />

169<br />

AD8014RT<br />

205<br />

C281 R41 243 1%<br />

C372<br />

47pF NPO<br />

R43<br />

R392<br />

Vref<br />

2 1<br />

R44 2.2K<br />

499 1%<br />

2 1<br />

1 2 MAX9013EUA<br />

Q14<br />

C282<br />

R48 x2.5<br />

2N7002<br />

Vref x4 499 1% C358 100nF<br />

499 1%<br />

C356<br />

DISC-OneSPE<br />

G<br />

OneSPE-nL<br />

10uF 6.8V Tan<br />

100nF<br />

1*1.3*5 + 2*1.3*5 + 6.8*10 + 2* 1.15*10+2*1.1*5+<br />

C412<br />

Vref<br />

2 1<br />

3*0.4*10=13 4 mW<br />

C411 100nF<br />

R370<br />

opamp comparator, 1135 80 14 8014 8005<br />

10uF 6.8V Tan<br />

10K 1%<br />

B19 10uF 6.8V Tan<br />

5Vanalog<br />

1 2<br />

AD advertises that these (400 MHz) amplifiers re cover in 60 ns. At 5 mW<br />

C32<br />

per stage, they give slightly less performance than an HA1135 at 1/10th<br />

the current. Saturation is not a big issue for t he (latching) comparator<br />

LI0805D121R 1 2<br />

R49<br />

Calibration input<br />

input, since latch recovery is contr olled by the FPGA<br />

C30<br />

2 1<br />

5Vanalog<br />

100nF<br />

test-point. Drive<br />

2 1<br />

4 Analog_Ref<br />

1 2<br />

10<br />

4<br />

with 5V square<br />

If we have power to burn, once all revisions are taken into account, the<br />

R57 100<br />

Clamp<br />

C31 100nF<br />

TP67<br />

850 MHz bandwidth HA1135 may prove to be a bett er choice as comparator<br />

X5.33<br />

C33 10uF 6.8V Tan<br />

wave to generate<br />

R52<br />

input amplifier, as one stage should hav e less delay than 2.<br />

33 U44<br />

X3 1 2<br />

1 2 3<br />

R53<br />

U48<br />

1<br />

fixed amplitude<br />

+<br />

6<br />

1 2<br />

3<br />

R325 20<br />

2-Pin Header<br />

The comparators exhibit less trigger delay i f driven by a positive<br />

+<br />

test pulses.<br />

2<br />

-<br />

1<br />

1 2<br />

ATWD_IN_0<br />

signal, so the second gain stage inverts. The first one buffers<br />

HFA1135IB<br />

20<br />

4<br />

to minimize load on the PMT signal.<br />

B30 X 5.36 R58<br />

-<br />

AD8014RT<br />

LI0805D121R<br />

-5V X 3.0 optimized for 200 MHz BW<br />

FE_TEST_PULSE_AMPL<br />

If test pulser, U52, injects too much power supply noise, it will<br />

100<br />

-5V<br />

C35 100nF Also try observi ng the<br />

FE_TEST_PULSE<br />

have to go, in favor of something that is quieter.<br />

1 2<br />

5Vanalog<br />

performance of this<br />

R56<br />

stage with 499 a nd 249<br />

R59<br />

C34 100nF<br />

R62 10<br />

A<br />

C<br />

C122<br />

1 2<br />

1 2<br />

C38 10uF 6.8V Tan ohm feedback div ider.<br />

1nF NPO<br />

C408<br />

499<br />

2 1 See if it is st ill as<br />

JP6 R106<br />

C37<br />

100nF<br />

CR1<br />

41.2 1%<br />

stable. It shoul d have<br />

C360<br />

2 1<br />

R61<br />

1<br />

more bandwi dth.<br />

1 2<br />

BAS70-04<br />

2<br />

16.8<br />

R107<br />

C42<br />

10uF 6.8V Tan<br />

1K 1%<br />

R326 1K 1% 3.3V<br />

Vref 100nF<br />

R60<br />

2 Pin Header 33<br />

1 2<br />

C285 10uF 6.8V Tan<br />

180 1% optimized for 200 MHz BW 100nF C361<br />

R100 20<br />

Vref<br />

R108 R99<br />

SamTec SMM-102 -01-S-D<br />

3.3V<br />

Open Ckt 10K 1%*<br />

Thru-Hole 2x2 2m m socket<br />

C220<br />

mates with S amTec<br />

100nF<br />

U52<br />

TW-02-01-S-D-120-08 0 2x2 2mm<br />

3 R408 C265<br />

break-away h eader<br />

JU12<br />

3<br />

5Vanalog<br />

1 2<br />

NC7SZ126M52<br />

4<br />

1 2 TP69<br />

In Out<br />

1<br />

2-Pin Header<br />

Open Ckt<br />

C227 100nF<br />

499<br />

60 ns coax d elay<br />

TP68<br />

C228 10uF 6.8V Tan<br />

R815 5pF NPO<br />

JU11<br />

1<br />

assembly<br />

2-Pin Header<br />

X4.33 1 2<br />

Open Ckt<br />

R273<br />

U41<br />

TP65<br />

2.7K*<br />

1 2<br />

R323 20<br />

1<br />

3<br />

2-Pin Header<br />

R324<br />

+<br />

1<br />

1 2<br />

ATWD_IN_1<br />

300<br />

1 2 4<br />

-<br />

JP5<br />

JP19<br />

AD8014RT<br />

5Vanalog<br />

300 1% X4.33<br />

JP4<br />

1 2<br />

2 1<br />

C359<br />

C229 100nF<br />

A<br />

C<br />

3 4<br />

4 3<br />

C341<br />

1 2<br />

1<br />

Dly_Line_In<br />

SMM-102-01-S-D<br />

SMM-102-01-S-D<br />

Dly_Line_Out<br />

Vref 100nF<br />

Vref<br />

CR3<br />

-5V<br />

C383 10uF 6.8V Tan<br />

C230<br />

BAS70-04<br />

5Vanalog<br />

1 2<br />

2 1<br />

OE<br />

1 2<br />

1 2<br />

1 2<br />

CA<br />

1 2<br />

1 2<br />

1 2<br />

1 2<br />

10uF 6.8V Tan<br />

1 2<br />

Coax_SMB_75_ohm<br />

C<br />

A<br />

C40<br />

10uF 6.8V Tan<br />

EAP 2709-1511-00 1 or the<br />

1 2<br />

R186<br />

2709-7511-001 PCB or<br />

BAS70-04<br />

JU40<br />

R54<br />

100nF<br />

1 2<br />

equivalent<br />

CR8<br />

1 2<br />

Test pulse inj ection<br />

1 2<br />

63.4 1%<br />

TP72<br />

1K 1%<br />

eapconnectors.co m, e.g.<br />

C36<br />

Vref<br />

(if it doesn't work,<br />

Open Ckt R30<br />

U53<br />

1<br />

2-Pin Header<br />

AMP 414244-1<br />

JP13<br />

1 2 remove transf ormer, Inject-<br />

1 2<br />

3<br />

R101 10<br />

+<br />

and use jum per.)<br />

1 1 2<br />

2<br />

100nF<br />

31.6 1%<br />

ATWD_IN_2<br />

4<br />

1<br />

-<br />

C41<br />

AD8014RT<br />

1 2<br />

If the PMT delivers 3V into a 50 ohm load, then change<br />

HEADER 2<br />

the divider resistors to R30=31.6 a nd R54=63.4 Leave<br />

2 -5V<br />

10uF 6.8V Tan<br />

2<br />

the gain of the amplifier unchanged. The design goal<br />

R64<br />

C384 C39<br />

is to have the PMT saturation volta ge within the span<br />

10K 1%<br />

of the ATWD.<br />

10uF 6.8V Tan 100nF<br />

0.47uF Y5V<br />

Samsung CL31F4 74ZBNC<br />

(0.12)<br />

R34<br />

1 2 1 2<br />

3.3V<br />

1K 1% R31 1K 1%<br />

C58<br />

C54<br />

100nF Vref<br />

10uF 6.8V Tan<br />

1 2<br />

10uF 6.8V Tan<br />

5 8<br />

D<br />

D<br />

1 2<br />

CA<br />

8 16<br />

CA<br />

C46 10uF 6.8V Tan<br />

C44 100nF<br />

C45 100nF<br />

R65 10 1 2<br />

5Vanalog<br />

1 2<br />

1 2<br />

5Vanalog<br />

1 2<br />

5Vanalog<br />

C43 100nF<br />

C47 10uF 6.8V Tan<br />

C48 10uF 6.8V Tan<br />

1 2<br />

1 2<br />

1 2<br />

TP66 The shaped signal path design was from<br />

R69 511<br />

U54<br />

U15<br />

U16<br />

1<br />

2-Pin Header<br />

Harold Yaver of the Engineering Department.<br />

1 2 3<br />

R70 205 R71 205<br />

3<br />

R72 205 R73 205<br />

3<br />

R74<br />

+<br />

+<br />

+<br />

1 1 2 1 2<br />

1<br />

1 2 1 2<br />

1<br />

1 2<br />

-Modifications added to insure stable offset behavior,<br />

FADC_In<br />

4<br />

4<br />

4<br />

and to offset the output to match the input range of<br />

5Vanalog<br />

-<br />

AD8005RT<br />

-<br />

AD8005RT<br />

-<br />

AD8005RT Jumper<br />

-5V<br />

C52<br />

C53<br />

the ADC<br />

C49 100nF<br />

C50 100nF<br />

C51 100nF<br />

MAX4166ESA<br />

1 2<br />

1 2<br />

1 2 Jan 19, 2003 Correct reversed polarized<br />

1 1<br />

-5V -5V<br />

U74<br />

Distribute capacitors around th e island of Vref.<br />

R76<br />

C24<br />

C56<br />

C27<br />

capacitors on analog stages. gtp<br />

3<br />

R264 24.9 1% If some are not needed, they ma y not be mounted.<br />

C23 100nF<br />

10 C55<br />

100nF<br />

2 1<br />

100nF<br />

C57<br />

PEDESTAL<br />

+<br />

6<br />

1 2<br />

Vref<br />

1 2<br />

2 1<br />

1 2<br />

1 2<br />

2 1<br />

2<br />

10uF 6.8V Tan<br />

-<br />

C283<br />

+ + + +<br />

R79 10uF 6.8V Tan<br />

R81 1.5K 1% R82<br />

R83 1.5K 1% R84 10uF 6.8V Tan<br />

C284<br />

Vref 1 2 2 1 1 2<br />

2 1 1 2 1 2<br />

2 1 1 2 1 2<br />

3K 1%<br />

3K 1%<br />

<strong>Lawrence</strong> <strong>Berkeley</strong> <strong>National</strong> <strong>Laboratory</strong><br />

GTP/JL/DRN/HY<br />

C422 C428<br />

1.5K 1% R80 2.49K 1%<br />

C60 33pF NPO<br />

C22<br />

C61 33pF NPO<br />

Title<br />

C272 C420 C273 C419 C418 10uF 6.8V Tan 10uF 6.8V Tan C18<br />

C19<br />

1 2<br />

1 2<br />

Digital Optical Module Analog Front End<br />

R265 10K 1%<br />

100nF 100nF 100nF 100nF 100nF<br />

10uF 6.8V Tan<br />

10uF 6.8V Tan<br />

10uF 6.8V Tan<br />

1 2<br />

C423 C421<br />

Size Document Number Rev<br />

10uF 6.8V Tan 10uF 6.8V Tan<br />

C 0<br />

to... Martin Keste l 3/30/03<br />

Date: Friday, May 16, 2003<br />

Sheet 5 of 15<br />

A<br />

B<br />

C<br />

D<br />

E<br />

SDW N<br />

Vcc<br />

Vee<br />

100nF<br />

1 2<br />

10uF 6.8V Tan<br />

Vref<br />

110pF NPO<br />

1 2<br />

Vref<br />

110pF NPO<br />

1 2

A<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

U82B<br />

B<br />

COINC_UP_A<br />

R393 100 C413 22pF NPO<br />

1 2 COINC_UP_ABAR<br />

C<br />

D<br />

EB_nCS0<br />

R3944.7K<br />

E<br />

IO_Bank 12<br />

EB_nCS1<br />

R3954.7K<br />

not includi ng<br />

R396 100 C414 22pF NPO<br />

multi_purpo se<br />

COINC_UP_B<br />

1 2 COINC_UP_BBAR<br />

EB_nCS2<br />

R3974.7K<br />

pins<br />

EB_nCS3<br />

R3984.7K<br />

K2<br />

R86 100 C415 22pF NPO<br />

IO-*LVDSOUT05n<br />

FL_TRIGGER<br />

COINC_DOWN_A 1 2 COINC_DOWN_ABAR<br />

3.3V<br />

L1<br />

U82F<br />

Flash Chip Select routed throu gh PLD<br />

U82K<br />

IO-*LVDSOUT06p L2<br />

COM_DB6<br />

U82H<br />

IO-*LVDSOUT06n<br />

COM_DB7<br />

R400 100 C416 22pF NPO<br />

IO_Bank_8<br />

IO_Bank_2<br />

B5<br />

M1<br />

COINC_DOWN_B 1 2 COINC_DOWN_BBAR<br />

EB_nCS0<br />

EB_nCS[0..3]<br />

SD_CLK<br />

IO_Bank_6<br />

K17<br />

SD_CLK G7<br />

SD_nCLK<br />

IO-*LVDSOUT07p<br />

M2<br />

COM_DB8<br />

EBI_CS0<br />

H20 EB_nCS1<br />

SD_CLK_N<br />

IO-*LVDSOUT07n<br />

COM_DB9<br />

FA[0..17]<br />

FA0<br />

EBI_CS1<br />

SD RAM<br />

F7<br />

EB_nCS2<br />

SD_CLKE<br />

AB26<br />

L21<br />

Extension<br />

J19<br />

SD_CLKE<br />

FA1 AB25 IO-*RXINCLK1p_LVDSIO-L21<br />

EBI_CS2<br />

Bus<br />

R1<br />

M22<br />

G20 EB_nCS3<br />

D6 SD_CS_N1<br />

SD_CS_N[0..1]<br />

IO-*LVDSOUT08p<br />

COM_DB10<br />

Bus<br />

R2<br />

IO-*RXINCLK1n_LVDSIO-M22<br />

M24<br />

EBI_CS3<br />

SD_CS_N1<br />

E7 SD_CS_N0<br />

IO-*LVDSOUT08n<br />

COM_DB11<br />

FA2 Y26<br />

IO-M24 M21<br />

FL_ATTN<br />

EBA[0..24] Interface<br />

C22<br />

SD_CS_N0 J9<br />

T1<br />

FA3 Y25<br />

IO-*LVDSIN01 IO-M21<br />

L20<br />

FL_TCK<br />

EBI_OE_N<br />

E21<br />

EB_nOE<br />

SD_RAS_N<br />

F8<br />

nRAS<br />

IO-*LVDSOUT09p<br />

COM_DB12<br />

FL_TDO<br />

EB_nWE<br />

nCAS<br />

T2<br />

IO-*LVDSIN01A IO-L20<br />

M19<br />

EBI_WE_N<br />

SD_CAS_N<br />

A5<br />

See HW Ref Manu al<br />

IO-*LVDSOUT09n<br />

COM_DB13<br />

FA4 AA26<br />

IO-M19 L19<br />

FL_TDI<br />

EBA0 F20<br />

D22<br />

SD_WE_N nWE<br />

FL_Trigger_bar<br />

FA5<br />

FL_TMS<br />

U1<br />

AA25<br />

IO-*LVDSIN02p IO-L19<br />

N25<br />

EBA1 C21<br />

EBI_A0<br />

EBI_BE0<br />

K18<br />

F12<br />

IO-*LVDSOUT10p U2<br />

IO-*LVDSIN02n IO-N25 M23<br />

FL_PRE_TRIG<br />

EBA2 E20 EBI_A1<br />

EBI_BE1<br />

SD_DQS0 H11<br />

IO-*LVDSOUT10n<br />

COM_TX_SLEEP<br />

U82A<br />

FA6 W26<br />

IO-M23<br />

N23<br />

FL_Trigger<br />

EBA3 H18<br />

EBI_A2<br />

C17 EBD0 EBD[0..15]<br />

SD_DQS1<br />

J10<br />

4 FA7<br />

FL_Trigger_bar<br />

W1<br />

W25<br />

IO-*LVDSIN03p IO-N23<br />

K24<br />

EBA4 G19<br />

EBI_A3<br />

EBI_DQ0<br />

G16 EBD1<br />

SD_DQS2<br />

K10<br />

4<br />

IO-*LVDSOUT11p W2<br />

FPGA_D0<br />

E4<br />

IO-*LVDSIN03n IO-K24 L24<br />

nFOE<br />

EBA5 J18 EBI_A4<br />

EBI_DQ1 D17 EBD2<br />

SD_DQS3<br />

IO-*LVDSOUT11n<br />

FPGA_D1<br />

A_nB<br />

FA8<br />

nFWE<br />

EBA6<br />

EBD3<br />

SD_DQM0<br />

SD_DQM[0..3]<br />

I/O Bank 13<br />

IO-E4_R1<br />

E3<br />

V26<br />

IO-L24<br />

K22<br />

J17<br />

EBI_A5<br />

EBI_DQ2<br />

E16<br />

H12<br />

V1<br />

IO-E3_R1<br />

FPGA_DA<br />

FA9 V25 IO-*LVDSIN04p IO-K22 L23<br />

nFLB<br />

EBA7 G18 EBI_A6<br />

EBI_DQ3 J15 EBD4<br />

SD_DQM1<br />

IO-*LVDSOUT12p<br />

FPGA_D2<br />

not includi ng<br />

F3<br />

SD_DQM0 G11<br />

V2<br />

IO-F3_R3<br />

FPGA_CE<br />

IO-*LVDSIN04n IO-L23<br />

L22<br />

nFUB<br />

EBA8 D20<br />

EBI_A7<br />

EBI_DQ4<br />

F16 EBD5<br />

SD_DQM2<br />

IO-*LVDSOUT12n<br />

FPGA_D3<br />

multi-purpo se<br />

F4<br />

SD_DQM1<br />

F9<br />

IO-F4_R1<br />

HVD_IN<br />

FA10<br />

nFCS3<br />

EBA9<br />

EBD6<br />

A[0..14]<br />

U26<br />

IO-L22<br />

F19<br />

EBI_A8<br />

EBI_DQ5<br />

SD_DQM3<br />

pins<br />

G3<br />

K19<br />

G15<br />

SD_DQM2<br />

C6<br />

Y1<br />

IO-G3_R2 G4<br />

HVD_TxENA<br />

FA11 U25 IO-*LVDSIN05p IO-K19 K21<br />

nFCS2<br />

EBA10 H17 EBI_A9<br />

EBI_DQ6 F15 EBD7<br />

SD_DQM3<br />

IO-*LVDSOUT13p<br />

FPGA_D4<br />

HVD_RxENA<br />

nFCS1<br />

EBA11<br />

EBD8<br />

A0<br />

D0<br />

D[0..31]<br />

Y2<br />

IO-G4_R2<br />

H3R399 100<br />

IO-*LVDSIN05n IO-K21<br />

K20<br />

E19<br />

EBI_A10<br />

EBI_DQ7<br />

H15<br />

K9<br />

J13<br />

IO-*LVDSOUT13n<br />

FPGA_D5<br />

IO-H3_R2 H4<br />

HVD_Rx<br />

FA12 T26<br />

IO-K20<br />

nFCS0<br />

EBA12 C20 EBI_A11<br />

EBI_DQ8 E15 EBD9<br />

A1 C5 SD_A0<br />

SD_DQ0 H13 D1<br />

AA1<br />

SingleLED-TRIGGER<br />

IO-H4_R2<br />

H5<br />

COM_AD_OTR<br />

FA13 T25<br />

IO-*LVDSIN06p<br />

EBA13 D19<br />

EBI_A12<br />

EBI_DQ9<br />

J14 EBD10<br />

A2 E6<br />

SD_A1<br />

SD_DQ1<br />

F13 D2<br />

IO-*LVDSOUT14p<br />

COM_AD_D9<br />

AA2<br />

IO-H5_R1<br />

J3<br />

IO-*LVDSIN06n<br />

EBA14 F18<br />

EBI_A13<br />

EBI_DQ10<br />

E14 EBD11<br />

A3 G6<br />

SD_A2<br />

SD_DQ2<br />

G13 D3<br />

IO-*LVDSOUT14n<br />

FPGA_D6<br />

IO-J3_R3 J4<br />

COM_AD_D8<br />

FA14 R26<br />

EBA15 C19 EBI_A14<br />

EBI_DQ11 K14 EBD12<br />

A4 K8 SD_A3<br />

SD_DQ3 E13 D4<br />

IO-J4_R3<br />

COM_AD_D7<br />

J5<br />

FA15 R25<br />

IO-*LVDSIN07p<br />

EBA16 G17<br />

EBI_A15<br />

EBI_DQ12<br />

G14 EBD13<br />

A5 A4<br />

SD_A4<br />

SD_DQ4<br />

D13 D5<br />

AC2<br />

IO-J5_R2 K3<br />

COM_AD_D6<br />

IO-*LVDSIN07n<br />

EBA17 K15 EBI_A16<br />

EBI_DQ13 F14 EBD14<br />

A6 B4 SD_A5<br />

SD_DQ5 C13 D6<br />

IO-*LVDSOUT15n<br />

FPGA_D7<br />

IO-K3_R4<br />

K4<br />

COM_AD_D5<br />

FA16 M26<br />

3.3V<br />

EBA18 D18<br />

EBI_A17<br />

EBI_DQ14<br />

H14 EBD15<br />

A7 F5<br />

SD_A6<br />

SD_DQ6<br />

B12 D7<br />

COM_AD_D4<br />

AB1<br />

IO-K4_R3<br />

K5<br />

FA17 M25<br />

IO-*LVDSIN08p<br />

EBA19 E18<br />

EBI_A18<br />

EBI_DQ15<br />

A8 D5<br />

SD_A7<br />

SD_DQ7<br />

E12 D8<br />

IO-*LVDSOUT16p AB2<br />

COINCIDENCE_OUT_UP<br />

IO-K5_R4 L3<br />

COM_AD_D3<br />

IO-*LVDSIN08n<br />

EBA20 H16 EBI_A19<br />

D21<br />

A9 G5 SD_A8<br />

SD_DQ8 G12 D9<br />

IO-*LVDSOUT16n<br />

COINCIDENCE_OUT_DOWN<br />

IO-L3_R5<br />

COM_AD_D2<br />

FD[0..15] FD0<br />

EB_CLK<br />

L4<br />

L26<br />

EBA21 F17<br />

EBI_A20<br />

EBI_CLK<br />

A10 K11<br />

SD_A9<br />

SD_DQ9<br />

J12 D10<br />

IO-L4_R4 L5<br />

COM_AD_D1<br />

FD1 L25 IO-*LVDSIN09p<br />

EBA22 C18 EBI_A21<br />

H19<br />

A11 E5 SD_A10 SD_DQ10 A12 D11<br />

IO-L5_R4<br />

COM_AD_D0<br />

IO-*LVDSIN09n<br />

EBA23 J16<br />

EBI_A22 INT_EXT_PIN_N INT_EXT_PIN_N<br />

A12<br />

D12<br />

EPXA1F672I2<br />

R5<br />

H8<br />

SD_A11 SD_DQ11<br />

C12<br />

IO-R5_R5<br />

R6<br />

FD2 K26<br />

EBA24 E17<br />

EBI_A23<br />

K16<br />

A13 J8<br />

SD_A12 SD_DQ12<br />

B11 D13<br />

IO-R6_R6<br />

FPGA_RW<br />

FD3 K25 IO-*LVDSIN10p<br />

EBI_A24See Errata- > EBI_ACK<br />

A14 F6 SD_A13 SD_DQ13 K13 D14<br />

IO-*LVDSIN10n<br />

SD_A14 SD_DQ14<br />

A11 D15<br />

FD4 J26<br />

SD_DQ15 A9 D16<br />

EPXA1F672I2<br />

FD5<br />

EPXA1F672I2<br />

J25<br />

IO-*LVDSIN11p<br />

SD_DQ16<br />

H10 D17<br />

This is a 2.5V I/O ban k...<br />

IO-*LVDSIN11n<br />

SD_DQ17<br />

B9 D18<br />

FD6H26<br />

SD_DQ18 C9 D19<br />

DO NOT CHANGE PIN<br />

FD7H25<br />

IO-*LVDSIN12p<br />

SD_DQ19<br />

E9 D20<br />

IO-*LVDSIN12n<br />

SD_DQ20<br />

ASSIGNMENTS OF AC8, AD7,<br />

K12 D21<br />

FD8<br />

AD8, AE7. These pin<br />

G26<br />

SD_DQ21<br />

D9 D22<br />

FD9<br />

D23<br />

assignments chosen to<br />

G25<br />

IO-*LVDSIN13p<br />

SD_DQ22<br />

G9<br />

IO-*LVDSIN13n<br />

SD_DQ23 D8 D24<br />

optimize speed. gtp<br />

FD10F26<br />

SD_DQ24<br />

H9 D25<br />

9/11/02<br />

FD11F25<br />

IO-*LVDSIN14p<br />

SD_DQ25 A7 D26<br />

IO-*LVDSIN14n<br />

SD_DQ26<br />

B7 D27<br />

FD12E26<br />

SD_DQ27<br />

E8 D28<br />

FD13E25<br />

IO-*LVDSIN15p<br />

SD_DQ28 G8 D29<br />

U82C<br />

IO-*LVDSIN15n<br />

SD_DQ29<br />

C7 D30<br />

FD14D26<br />

SD_DQ30 D7 D31<br />

FD15D25<br />

IO-*LVDSIN16p<br />

SD_DQ31<br />

ATWD1VDD-SUP<br />

If the FE_TEST_PULSE --><br />

AB8 IO_Bank 11<br />

IO-*LVDSIN16n<br />

G10<br />

ATWDTrigger_0<br />

line injec ts<br />

AC8 IO-AB8_C1<br />

OneSPE<br />

R369 10K 1%<br />

nc-SD_DQ_ECC0 J11<br />

AD7<br />

IO-AC8_C2<br />

nc-SD_DQ_ECC1<br />

objectionable noise into<br />

ATWDTrigger_1<br />

ATWD0VDD-SUP<br />

EPXA1F672I2<br />

C10<br />

AE7 IO-AD7_C2<br />

nc-SD_DQ_ECC2 C11<br />

the front, then per haps<br />

MultiSPE<br />

AD8<br />

IO-AE7_C3<br />

U62E<br />

R368 10K 1%<br />

nc-SD_DQ_ECC3<br />

E10<br />

MultiSPE-nL<br />

that could be mitig ated<br />

AC9<br />

IO-AD8_C3<br />

AD22<br />

R2BUS0<br />

nc-SD_DQ_ECC4<br />

D11<br />

COINC_DOWN_ALATCH<br />

by making it dr ive<br />

AE9 IO-AC9_C4<br />

IO-AD22 AC22<br />

nc-SD_DQ_ECC5 F11<br />

COINC_DOWN_ABAR<br />

FE_TEST_PULSE<br />

AA10<br />

IO-AE9_C4<br />

IO-AC22<br />

AC25<br />

nc-SD_DQ_ECC6<br />

differentiall y.<br />

COINC_DOWN_A<br />

AD9 IO-AA10_C5<br />

IO-AC25 AC26<br />

F10<br />

COINC_DOWN_BLATCH<br />

AB9<br />

IO-AD9_C5<br />

IO-AC26<br />

AB19<br />

nc-SD_DQS_ECC<br />

D10<br />

3 COINC_DOWN_BBAR<br />

OneSPE-nL<br />

AC10<br />

IO-AB9_C6<br />

IO-AB19<br />

AB20<br />

R2BUS2<br />

nc-SD_DQM_ECC<br />

3<br />

COINC_DOWN_B<br />

AF9 IO-AC10_C6<br />

R2BUS1<br />

COINC_UP_ALATCH<br />

IO_Bank 9<br />

IO-AB20 AB21<br />

D12<br />

AB10<br />

IO-AF9_C7<br />

IO-AB21<br />

COINC_UP_A<br />

not includi ng<br />

AB22<br />

DDR_VS0<br />

E11<br />

AE10 IO-AB10_C7<br />

IO-AB22<br />

COINC_UP_ABAR<br />

multi_purpo se<br />

AB23<br />

DDR_VS1 C8<br />

AA11<br />

IO-AE10_C8<br />

IO-AB23<br />

AB24<br />

DDR_VS2<br />

COINC_UP_BLATCH<br />

pins<br />

AF10<br />

IO-AA11_C8<br />

IO-AB24<br />

AA19<br />

COINC_UP_BBAR<br />

AD10 IO-AF10_C9<br />

IO-AA19 AA20<br />

COINC_UP_B<br />

R2BUS3<br />

AB11<br />

IO-AD10_C9<br />

IO-AA20<br />

EPXA1F672I2<br />

AA21<br />

R2BUS4<br />

FLASH_AD_D0<br />

AC11 IO-AB11_C10<br />

IO-AA21 AA22<br />

FLASH_AD_D1<br />

AD11<br />

IO-AC11_C10<br />

IO-AA22<br />

AA23<br />

FLASH_AD_D2<br />

AF11<br />

IO-AD11_C11<br />

IO-AA23<br />

AA24<br />

FLASH_AD_D3<br />

AA12 IO-AF11_C11<br />

IO-AA24 Y19<br />

FLASH_AD_D4<br />

AB12<br />

IO-AA12_C12<br />

IO-Y19<br />

Y20<br />

R2BUS5<br />

FLASH_AD_D5<br />

AE11 IO-AB12_C12<br />

IO-Y20 Y21<br />

R2BUS6<br />

FLASH_AD_D6<br />

AC12<br />

IO-AE11_C13<br />

IO-Y21<br />

Y22<br />

R2BUS7<br />

FLASH_AD_D7<br />

AD12<br />

IO-AC12_C13<br />

IO-Y22<br />

Y23<br />

FLASH_AD_D8<br />

AC13 IO-AD12_C14<br />

IO-Y23 Y24<br />

FLASH_AD_D9<br />

IO-Y24<br />

R2BUS[0..7]<br />

AB14<br />

IO-AC13_C14<br />

W20<br />

FLASH_NCO<br />

AA13 IO-AB14_C15<br />

IO-W20 W21<br />

U82L<br />

AB13<br />

IO-AA13_C15<br />

IO-W21<br />

W22<br />

FLASH_AD_STBY<br />

IO-AB13_C16<br />

IO-W22<br />

W23 FE_PULSER0n<br />

A2<br />

A3<br />

IO-W23 W24 FE_PULSER0p<br />

A8 GND<br />

VccInt A24<br />

1.8V<br />

IO-W24<br />

EPXA1F672I2<br />

V19<br />

A10<br />

GND<br />

VccInt<br />

B3<br />

R363<br />

IO-V19 V20<br />

A14 GND<br />

VccInt B8<br />

IO-V20<br />

V21<br />

PLD_FPGA_nOE<br />

A17<br />

GND<br />

VccInt<br />

B10<br />

10K<br />

IO-V21<br />

PLD_FPGA_nWE<br />

V22<br />

A19<br />

GND<br />

VccInt<br />

B17<br />

IO-V22 V23 FE_PULSER1p<br />

PLD_FPGA_BUSY<br />

A25 GND<br />

VccInt B19<br />

IO-V23 FE_PULSER1n<br />

PLD_FPGA[0..7]<br />

V24<br />

B1<br />

GND<br />

VccInt<br />

B24<br />

IO-V24 U20<br />

PLD_FPGA7<br />

B2 GND<br />

VccInt C1<br />

IO-U20<br />

U21<br />

PLD_FPGA6<br />

B6<br />

GND<br />

VccInt<br />

C2<br />

IO-U21<br />

U22 FE_PULSER2p<br />

PLD_FPGA5 Feb 6, 2003 g tp<br />

B13<br />

GND<br />

VccInt<br />

C4<br />

IO-U22 U23 FE_PULSER2n<br />

PLD_FPGA4<br />

IO-U23<br />

Feb 20, 2003 gtp net name<br />

B21 GND<br />

VccInt C23<br />

T20<br />

PLD_FPGA3<br />

IO-T20<br />

changes<br />

B25<br />

GND<br />

VccInt<br />

C25<br />

C91<br />

T21<br />

PLD_FPGA2<br />

B26 GND<br />

VccInt C26 OSCON 6SC47M<br />

IO-T21<br />

T22 FE_PULSER3p<br />

PLD_FPGA1<br />

C3<br />

GND<br />

VccInt<br />

D3 From Sanyo Vi deo C92<br />

IO-T22<br />

T24 FE_PULSER3n<br />

PLD_FPGA0<br />

C24<br />

GND<br />

VccInt<br />

D24<br />

OSCON 6SC47M<br />

IO-T24 R20<br />

D4 GND<br />

VccInt L13<br />

IO-R20<br />

D23<br />

GND<br />

VccInt<br />

L15<br />

L11 GND<br />

VccInt M13<br />

EPXA1F672I2<br />

L16<br />

GND<br />

VccInt<br />

M16<br />

M12<br />

GND<br />

VccInt<br />

N2<br />

M15 GND<br />

gtp<br />

VccInt N10<br />

M17<br />

GND<br />

LBNL<br />

VccInt<br />

N12<br />

C93 C94<br />

N1 GND<br />

9/3/2002<br />

VccInt P15<br />

470pF NPO 470pF NPO<br />

N4<br />

GND<br />

VccInt<br />

P18<br />

N11<br />

GND<br />

VccInt<br />

P24<br />

N13 GND<br />

VccInt P25<br />

MEMVIO<br />

N14<br />

GND<br />

VccInt<br />

R10<br />

10K 1% 10K 1% 10K 1% 10K 1% 10K 1% 10K 1% 10K 1%<br />

N16 GND<br />

VccInt R11<br />

R207 R204 R201 R198 R195 R192 R189<br />

N18<br />

GND<br />

VccInt<br />

R14<br />

C95 C101<br />

2 10K 1% 10K 1% 10K 1% 10K 1% 10K 1%<br />

Connect all the NO_CONNECT pins<br />

N26<br />

GND<br />

VccInt<br />

T12<br />

100nF 100nF<br />

2<br />

R206 R203 R200 R194 R191<br />

to an obstacle on a plane that<br />

P1 GND<br />

VccInt T17<br />

3.3V<br />

R263 Open Ckt<br />

10K 1% 10K 1% 10K 1% 10K 1% 10K 1% 10K 1%<br />

WILL NOT map to a gerber l ayer.<br />

P2<br />

GND<br />

VccInt<br />

U9<br />

R205 R202 R196 R193 R190 R187<br />

P3 GND<br />

VccInt U14<br />

This insures that all the pins<br />

R258 Open CktI/O bank used by SDR AM.<br />

3.3V<br />

P13<br />

GND<br />

VccInt<br />

U16<br />

2.5V<br />

Support optional I/O volta ges.<br />

are connected to pads, s o are<br />

P14<br />

GND<br />

VccInt<br />

AC3<br />

R259 Jumper<br />

accessable .<br />

P16 GND<br />

VccInt AC24<br />

1.8V<br />

P23<br />

GND<br />

VccInt<br />

AD1<br />

P26 GND<br />

VccInt AD2 C417 C379 C380<br />

U82D<br />

NC<br />

R12<br />

GND<br />

VccInt<br />

AD4 470pF NPO100nF<br />

OSCON 6SC47M<br />

IO_Bank 10<br />

R15<br />

GND<br />

VccInt<br />

AD23<br />

3.3V<br />

not includi ng AA14<br />

U82M<br />

R17 GND<br />

VccInt AD25<br />

IO-AA14<br />

TriggerComplete_0<br />

multi_purpo se W14<br />

R18051<br />

R19924.9<br />

T11<br />

GND<br />

VccInt<br />

AD26<br />

IO-W14 W15<br />

OutputEnable_0<br />

FE_PULSER0p<br />

D1<br />

T13 GND<br />

VccInt AE3<br />

pins IO-W15<br />

Y15<br />

ATWD0_D0 CounterClock_0<br />

D2<br />

NC<br />

U3<br />

T14<br />

GND<br />

VccInt<br />

AE8<br />

IO-Y15<br />

AC14<br />

R115<br />

E1<br />

NC NC<br />

U4<br />

T16<br />

GND<br />

VccInt<br />

AE19<br />

C345 C346<br />

IO-AC14 V15<br />

ATWD0_D1<br />

ShiftClock_0<br />

12.4<br />

E2 NC NC U5<br />

T18 GND<br />

VccInt AE24 C315 100nF OSCON 6SC47M<br />

IO-V15<br />

AD15<br />

R21651<br />

R275 24.9<br />

F1<br />

NC NC<br />

U6<br />

U10<br />

GND<br />

VccInt<br />

AF3 470pF NPO<br />

IO-AD15 AC15<br />

ATWD0_D2<br />

RampSet_0<br />

FE_PULSER1p<br />

F2 NC NC U7<br />

U12 GND<br />

VccInt AF24<br />

3.3V<br />

IO-AC15<br />

AB15<br />

G1<br />

NC NC<br />

U19<br />

U17<br />

GND<br />

VccInt<br />

IO-AB15<br />

ATWD0_D3<br />

ChannelSelectMSB_0<br />

AA15<br />

R117<br />

G2<br />

NC NC<br />

V4<br />

V9<br />

GND<br />

B14<br />

IO-AA15 AF16<br />

H1 NC NC V6<br />

V18 I/O bank used by<br />

IO-AF16<br />

ATWD0_D4<br />

CHannelSelectLSB_0<br />

12.4<br />

GND<br />

VccIO_2 P11<br />

B8<br />

AE16<br />

R21851<br />

R248 24.9<br />

H2<br />

NC NC<br />

V11<br />

W8<br />

GND<br />

SDRAM memor y.<br />

VccIO_2<br />

U15<br />

C347 C348 C349<br />

1812K121R Bead<br />

IO-AE16 AD16<br />

FE_PULSER2p<br />

H6 NC NC V12<br />

W19 GND<br />

VccIO_2<br />

470pF NPO100nF<br />

OSCON 6SC47M<br />

VddC0<br />

1 2<br />

IO-AD16<br />

AB16<br />

ATWD0_D5 ReadWrite_0<br />

H7<br />

NC NC<br />

V13<br />

AC4<br />

GND<br />

P17<br />

1.8V<br />

IO-AB16<br />

3.3V<br />

AC16<br />

R181<br />

J1<br />

NC NC<br />

V14<br />

AC23<br />

GND<br />

VccIO_3<br />

R18<br />

IO-AC16 AA16<br />

ATWD0_D6<br />

AnalogReset_0<br />

12.4<br />

J2 NC NC W3<br />

AD3 GND<br />

VccIO_3 U13<br />

IO-AA16<br />

V16<br />

R18251<br />

R255 24.9<br />

R18424.9 T8<br />

J6<br />

NC NC<br />

W4<br />

AD24<br />

GND<br />

VccIO_3<br />

IO-V16 W16<br />

ATWD0_D7<br />

DigitalReset_0<br />

FE_PULSER3p<br />

J7 NC NC W9<br />

AE1 GND<br />

A6<br />

C357<br />

IO-W16<br />

Mini-Circuit s<br />

C155<br />

C369<br />

Y16<br />

4<br />

3<br />

K1<br />

NC NC<br />

W10<br />

AE2<br />

GND<br />

I/O bank used b y<br />

VccIO_6<br />

L12<br />

C370 C299 C300<br />

10nF 100nF C368 2.2uF 6.3V Tan B11<br />

IO-Y16<br />

ATWD0_D8<br />

DigitalSet_0<br />

VRef<br />

AF17<br />

K6<br />

NC NC<br />

W11<br />

AE6<br />

GND<br />

Flash memory .<br />

VccIO_6<br />

L14<br />

470pF 100nF NPO OSCON 6SC47M<br />

10uF 6.8V Tan<br />

1812K121R Bead<br />

IO-AF17 AE17<br />

R249 R185<br />

K7 NC NC W12<br />

AE13 GND<br />

VccIO_6<br />

VddC1<br />

1 2<br />

IO-AE17<br />

ATWD0_D9<br />

3.3V<br />

AD17<br />

R18851<br />

R254 24.9 24.9 1<br />

K23<br />

NC NC<br />

W13<br />

AE21<br />

GND<br />

A13<br />

IO-AD17 AC17<br />

FE_PULSER3n<br />

6<br />

1<br />

L6 NC NC Y7<br />

AE25 GND<br />

VccIO_7 M14<br />

IO-AC17<br />

W17<br />

TriggerComplete_1<br />

Inject-<br />

L7<br />

NC NC<br />

Y8<br />

AE26<br />

GND<br />

VccIO_7<br />

N17<br />

IO-W17<br />

OutputEnable_1<br />

ATWD0_D[0..9]<br />

AB17<br />

R447 Mini-Circuits TCM1-1<br />

L8<br />

NC NC<br />

Y9<br />

AF2<br />

GND<br />

VccIO_7<br />

IO-AB17 AA17<br />

ATWD1_D0<br />

CounterClock_1<br />

12.4<br />

TP8<br />

L9 NC NC Y10<br />

AF8 GND<br />

A21<br />

C204 C207 C301<br />

C158 C302<br />

C304<br />

IO-AA17<br />

Y17<br />

R16251<br />

R252 24.9<br />

L10<br />

NC NC<br />

Y11<br />

AF14<br />

GND<br />

VccIO_8<br />

L17<br />

470pF 100nF NPO OSCON 6SC47M<br />

10nF 100nF C303 2.2uF 6.3V Tan B12<br />

IO-Y17 AF18<br />

ATWD1_D1<br />

ShiftClock_1<br />

FE_PULSER2n<br />

1<br />

L18 NC NC Y12<br />

AF19 GND<br />

VccIO_8 N15<br />

10uF 6.8V Tan<br />

1812K121R Bead<br />

IO-AF18<br />

AE18<br />

M6<br />

NC NC<br />

Y13<br />

AF25<br />

GND<br />

VccIO_8<br />

N24<br />

3.3V<br />

VddC2<br />

1 2<br />

IO-AE18<br />

ATWD1_D2<br />

RampSet_1<br />

AB18<br />

R163<br />

TP*<br />

M7<br />

NC NC<br />

Y14<br />

GND<br />

VccIO_9<br />

IO-AB18 Y18<br />

IO-Y18<br />

ATWD1_D3<br />

ChannelSelectMSB_1<br />

12.4<br />

M8 NC NC AA4<br />

R16<br />

AD18<br />

R16451<br />

R251 24.9<br />

M9<br />

NC NC<br />

AA5<br />

VccIO_9<br />

U18<br />

IO-AD18 AD19<br />

FE_PULSER1n<br />

M10 NC NC AA6<br />

VccIO_9<br />

C213 C214 C305<br />

IO-AD19<br />

AC20<br />

ATWD1_D4 CHannelSelectLSB_1<br />

M18<br />

NC NC<br />

AA7<br />

T15<br />

470pF NPO 100nF OSCON 6SC47M<br />

C159 C307<br />

C309<br />

IO-AC20<br />

AD20<br />

R165<br />

N6<br />

NC NC<br />

AA8<br />

VccIO_10<br />

V17<br />

10nF 100nF C308 2.2uF 6.3V Tan B14<br />

IO-AD20 AC19<br />

ATWD1_D5<br />

ReadWrite_1<br />

3.3V<br />

3.3V<br />

12.4<br />

N7 NC NC AA9<br />

VccIO_10 AE14<br />

10uF 6.8V Tan<br />

1812K121R Bead<br />

IO-AC19<br />

AC18<br />

R16651<br />

R250 24.9<br />

N8<br />

NC NC<br />

AB5<br />

VccIO_10<br />

AF21<br />

VddC3<br />

1 2<br />

IO-AC18 AE22<br />

ATWD1_D6<br />

AnalogReset_1<br />

FE_PULSER0n<br />

N9 NC NC AB6<br />

VccIO_10<br />

IO-AE22<br />

W18<br />

N19<br />

NC NC<br />

AB7<br />

R13<br />

1 IO-W18<br />

ATWD1_D7<br />

DigitalReset_1<br />

AA18<br />

P4<br />

NC NC<br />

AC1<br />

VccIO_11<br />

U11 C223 C310<br />

C226 C297<br />

1<br />

IO-AA18 AE23<br />

P7 NC NC AC5<br />

VccIO_11 V10<br />

IO-AE23<br />

ATWD1_D8<br />

DigitalSet_1<br />

C217 100nF OSCON 6SC47M C224 100nF OSCON 6SC47M<br />

AD21<br />

P8<br />

NC NC<br />

AC6<br />

VccIO_11<br />

AF13470pF NPO<br />

470pF NPO<br />

C206 C311<br />

C298<br />

IO-AD21 AE20<br />

ATWD1_D9<br />

P9 NC NC AC7<br />

VccIO_11<br />

10nF 100nF C312 2.2uF 6.3V Tan<br />

IO-AE20<br />

AF20<br />

P10<br />

NC NC<br />

AD5<br />

T10<br />

10uF 6.8V Tan<br />

B17<br />

IO-AF20<br />

3.3V<br />

AC21<br />

P19<br />

NC NC<br />

AD6<br />

VccIO_12<br />

AF6<br />

1812K121R Bead<br />

IO-AC21<br />

ATWD1_D[0..9]<br />

P22 NC NC AE4<br />

VccIO_12 M11<br />

VddC4<br />

1 2<br />

R3<br />

NC NC<br />

AE5<br />

VccIO_13<br />

N3<br />

R4 NC NC AF4<br />

VccIO_13 P12<br />

EPXA1F672I2<br />

R19<br />

NC NC<br />

AF5<br />

VccIO_13<br />

C237 C263 C296<br />

T3<br />

NC NC<br />

AF7<br />

R8<br />

R9<br />

470pF NPO100nF<br />

OSCON 6SC47M<br />

T4 NC NC AF22<br />

GND_CKLK4<br />

Vcc_CKLK4<br />

VddC0<br />

C280 C286<br />

C129<br />

T5<br />

NC NC<br />

AF23<br />

T9<br />

T8 VddC1<br />

JU5<br />

10nF 100nF C128 2.2uF 6.3V Tan<br />

T19 NC NC<br />

GND_CKLK2<br />

Vcc_CKLK2<br />

1 2<br />

10uF 6.8V Tan<br />

T23<br />

NC<br />

F23<br />

E23 VddC2<br />

3.3V 1 2 2.5V<br />

NC<br />

GND_CKLK6<br />

Vcc_CKLK6<br />

4/11/03 GT P Jumper<br />

F22<br />

E22 VddC3<br />

GND_CKLK5<br />

Vcc_CKLK5<br />

JU6<br />

V8<br />

U8 VddC4 C424 C425<br />

1 2 Title<br />

EPXA1F672I2<br />

GND_CKOUT2 VccCKOUT2<br />

470pF NPO100nF<br />

C426<br />

1 2 3.3V<br />

<br />

EPXA1F672I2<br />

OSCON 6SC47M Open Ckt<br />

Size Document Number Rev<br />

D <br />

<br />

IO_Bank_12<br />

R209 10K 1%<br />

R21 0 10K 1%<br />

R211 10K 1%<br />

R21 2 10K 1%<br />

R213 10K 1%<br />

R277 10K 1%<br />

R21 4 10K 1%<br />

R219 10K 1%<br />

A<br />

B<br />

C<br />

D<br />

E<br />

Friday, May 16, 2003<br />

Date: Sheet of 6 15

5<br />

4<br />

3<br />

2<br />

1<br />

2<br />

2<br />

A<br />

1<br />

2<br />

1<br />

6<br />

1<br />

2<br />

1<br />

2<br />

1<br />

6<br />

D<br />

S<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

1<br />

2<br />

7<br />

8<br />

4<br />

7<br />

8<br />

4<br />

Vee<br />

Vee<br />

1<br />

2<br />

8<br />

5<br />

2<br />

1<br />

2<br />

1<br />

2<br />

D<br />

S<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

1<br />

2<br />

EAP 2009-1511-000 or<br />

2009-1511-000 or equiva lent<br />

eapconnectors.c om<br />

Coax_50_ohm_SMB<br />

AMP 413990-1 or<br />

AMP 413990-2 or<br />

1 ICE_LED_PULSER<br />

AMP 415590-1 o r<br />

JP16<br />

AMP 413990-3 or<br />

AMP 414612-1 or<br />

AMP 414612- 2<br />

AMP 414612-1 or<br />

R362 1K 1%<br />

C319<br />

FL_REF<br />

R177<br />

100nF<br />

100<br />

R178<br />

C320<br />

Open Ckt 100nF<br />

ICE-LED-IN<br />

Multiplexed Calibration In puts:<br />

Toyocom Osc for capture rate calibration, and absolute ph ase reference<br />

CLK Osc 40 MHz system clock<br />

Flash current waveform for LED on DOM M ain Board<br />

Flash current waveform for LED daught er board<br />

Local Coincidence Signal from upper neighbor<br />

Local Coincidence Signal from lower neighbor<br />

Communications Signal for relative phase of time ticks<br />

Communications Signal for relative phase of time ticks<br />

For best integrity of calibration, mount the two<br />

MAX4141 chips such that the 20 ohm resisto r outputs<br />

abut, and pin 11 to the 20 ohm resistor is the same<br />

length, and leads to inputs are kept short s ince they<br />

are high frequency carri ers.<br />

B<br />

C<br />

ATWD_IN_2<br />

5Vanalog<br />

PMT_LED_PULSER<br />

ATWD_IN_2<br />

ATWD_IN_1<br />

C317<br />

5Vanalog<br />

ATWD_IN_1<br />

ATWD_IN_0<br />

R123<br />

PMT-LED-IN<br />

ATWD_IN_0<br />

R274<br />

100nF<br />

24.9K 1%<br />

100<br />

AnalogRef1<br />

R168 C318<br />

AnalogRef0<br />

C266<br />

4 1K 1% 100nF<br />

C267<br />

100nF<br />

C205<br />

4<br />

50mW/15mW<br />

100nF<br />

C63<br />

C288<br />

5Vanalog<br />

R401<br />

100nF<br />

R124<br />

100nF<br />

10uF 6.8V Tan<br />

4.7K<br />

U14<br />

R33<br />

U17<br />

4.7K<br />

U13<br />

U95A<br />

Jumper<br />

1<br />

8<br />

C287<br />

5Vanalog<br />

TOYOCOM_OSC<br />

SEL_A0<br />

ATWD_B_TC<br />

OutputEnable_1<br />

3<br />

IN1 A0<br />

Vdd<br />

8<br />

46<br />

9<br />

R327<br />

8<br />

46<br />

ATWD_A_TC 2<br />

54<br />

9<br />

Vdd<br />

Vdd<br />

45<br />

10uF 6.8V Tan<br />

CLKx2<br />

PMT-LED-IN 5 IN2 A1 10<br />

SEL_A1<br />

ATWD_A_TC<br />

OutputEnable_0<br />

TriggerComplete_0<br />

ATWD_B_CC<br />

ATWD_B0<br />

ICE-LED-IN<br />

MUX_EN0<br />

Jumper<br />

9 Vdd<br />

Vdd 45<br />

10 Trigger Complete<br />

OE 44<br />

U95B<br />

R2<br />

7<br />

IN3 EN<br />

ATWD_A_CC 10<br />

Trigger Complete<br />

OE<br />

44<br />

ATWD_A0<br />

ATWD_A0 3<br />

53 ATWD0_D0<br />

11<br />

Counter Clock<br />

D0<br />

43<br />

ATWD_B1<br />

ATWD_A1<br />

ShiftClock_1<br />

100 R257<br />

IN4<br />

13<br />

12 Shift Clock<br />

For KAMLAN D<br />

D1<br />

Vdd<br />

11 Counter Clock<br />

D0 43<br />

42<br />

ATWD_B2<br />

ATWD_B_TC 15<br />

41<br />

Open Ckt<br />

OUT<br />

12<br />

R365<br />

ShiftClock_0<br />

12<br />

Shift Clock<br />

For KAMLAN D<br />

D1<br />

42<br />

ATWD_A2<br />

ATWD_A1 4<br />

52 ATWD0_D1<br />

RampSet_1<br />

13<br />

Ramp Reset<br />

D2<br />

41<br />

ATWD_B3<br />

TriggerComplete_1<br />

In-<br />

RampSet_0<br />

ATWD_A3<br />

ChannelSelectMSB_1<br />

1K 1%<br />

13<br />

Ramp Reset<br />

D2<br />

41<br />

14<br />

Chnl MSB<br />

D3<br />

40<br />

ATWD_B4<br />

ATWD_B0 16<br />

40 ATWD1_D0<br />

nCLKx2<br />

2<br />

11<br />

ChannelSelectMSB_0<br />

ATWD_A4<br />

ATWD_A2<br />

ATWD0_D2<br />

CHannelSelectLSB_1<br />

MUX_EN0<br />

B1 LI0805D121R<br />

14 Chnl MSB<br />

D3 40<br />

5<br />

51<br />

15 Chnl LSB<br />

D4 39<br />

CHannelSelectLSB_0<br />

ATWD_B5<br />

Locate R2 a t<br />

ATWD_A5<br />

ReadWrite_1<br />

C382<br />

4<br />

GND1 SD<br />

14<br />

15<br />

Chnl LSB<br />

D4<br />

39<br />

16<br />

Read-Write<br />

D5<br />

38<br />

ATWD_B6<br />

ATWD_B1 18<br />

39 ATWD1_D1<br />

GND2 Vcc<br />

ReadWrite_0<br />

farthest end of<br />

6<br />

16 Read-Write<br />

D5 38<br />

ATWD_A6<br />

ATWD_A3 6<br />

50 ATWD0_D3<br />

AnalogReset_1<br />

17 Analog Reset<br />

D6 37<br />

ATWD_B7<br />

Open Ckt<br />

Vee<br />

AnalogReset_0<br />

transmissio n<br />

C64<br />

17<br />

Analog Reset<br />

D6<br />

37<br />

ATWD_A7<br />

DigitalReset_1<br />

18<br />

Digital ReSet<br />

D7<br />

36<br />

ATWD_B8<br />

ATWD_B2 20<br />

37 ATWD1_D2<br />

DigitalReset_0<br />

ATWD_A8<br />

ATWD_A4<br />

ATWD0_D4<br />

DigitalSet_1<br />

ATWD_B_TR<br />

line.<br />

AD8174AR<br />

100nF<br />

18<br />

Digital ReSet<br />

D7<br />

36<br />

7<br />

48<br />

19<br />

Digital Set<br />

D8<br />

35<br />

ATWD_B9<br />

DigitalSet_0<br />

R257,C382 used to<br />

ATWD_A_TR 19 Digital Set<br />

D8 35<br />

ATWD_A9<br />

20 Trigger Input<br />

D9 34<br />

ATWD_B3 21<br />

36 ATWD1_D3<br />

match U17-3 to m ake<br />

C65 B2<br />

20<br />

Trigger Input<br />

D9<br />

34<br />

ATWD_A5 9<br />

47 ATWD0_D5<br />

Vdd<br />

Vdd<br />

CLKx2 and nCLK x2<br />

100nF LI0805D121R<br />

Vdd<br />

Vdd<br />

ATWD_B4 22<br />

35 ATWD1_D4<br />

ATWD_A6 10<br />

46 ATWD0_D6<br />

C268<br />

ATWD<br />

symmetric.<br />

5Vanalog<br />

C269<br />

ATWD<br />

100nF<br />

B43<br />

ATWD_B5 23<br />

34 ATWD1_D5<br />

-5V<br />

100nF<br />

B50<br />

R197<br />

ATWD_A7 11<br />

45 ATWD0_D7<br />

LI0805D121R<br />

C208 C209<br />

LI0805D121R<br />

C66 C67<br />

10K 1%<br />

100nF 100nF<br />

ATWD_B6 24<br />

33 ATWD1_D6<br />

50mW/15mW<br />

ATWD_A8<br />

ATWD0_D8<br />

5Vanalog<br />

100nF 100nF<br />

12<br />

44<br />

C210<br />

U19<br />

C68<br />

5Vanalog<br />

100nF<br />

R208 ATWD_B7 25<br />

32 ATWD1_D7<br />

5Vanalog<br />

1<br />

8<br />

100nF<br />

ATWD_A_TR<br />

13<br />

43<br />

10K 1%<br />

R335 C381 LOCAL_COINCIDENCE_Upper<br />

3 IN1 A0 9<br />

SEL_A0<br />

ATWDTrigger_0<br />

ATWD_B8<br />

ATWD1_D8<br />

LOCAL_COINCIDENCE_Lower<br />

SEL_A1<br />

R329<br />

R217 R118<br />

C211<br />

C212<br />

26<br />

31<br />

1 2<br />

5<br />

IN2 A1<br />

10<br />

Jumper<br />

R111 R113<br />

C69<br />

C70<br />

TP61 ATWD_A9 14<br />

42 ATWD0_D9<br />

1K 1% 1K 1%<br />

100nF<br />

100nF<br />

COM_IN<br />

PULSE 7 IN3 EN MUX_EN1<br />

1K 1% 1K 1%<br />

100nF<br />

100nF<br />

ATWD_B_TR<br />

27<br />

30<br />

249<br />

IN4<br />

13<br />

5.1mW<br />

ATWD0_D[0..9]<br />

ATWDTrigger_1<br />

100nF<br />

OUT<br />

12<br />

1<br />

__<br />

R366<br />

Q9 Q10<br />

TP62 ATWD_B9<br />

ATWD1_D9<br />

In-<br />

OE 56<br />

28<br />

29<br />

1K 1%<br />

Q11 Q12<br />

MAX4166ESA<br />

2-Pin Header<br />

1<br />

ATWD1_D[0..9]<br />

2<br />

11<br />

B3 LI0805D121R<br />

1<br />

FSTD16211MTD<br />

MUX_EN1<br />

5Vanalog<br />

R260<br />

4 GND1 SD 14<br />

MMBTH81<br />

MMBTH81<br />

1<br />

__<br />

GND2 Vcc<br />

6<br />

5Vanalog<br />

OE<br />

55<br />

MMBTH81<br />

MMBTH81<br />

U75<br />

2-Pin Header<br />

100 1%<br />

Vee<br />

C71 Can use 2SB7 09<br />

3<br />

R266<br />

R330 R169 R170<br />

R331<br />

FSTD16211MTD<br />

R256 300<br />

100nF as current<br />

R88 R89<br />

+<br />

AD8174AR<br />

R332<br />

R333<br />

6<br />

AnalogRef0<br />

1M 100K 1% 100K 1% 1M<br />

C72 B4 mirror to<br />

1M 100K 1% 100K 1% 1M<br />

2<br />

100nF LI0805D121R<br />

-<br />

reduce packa ge<br />

C215<br />

C73<br />

24.9 1%<br />

100nF<br />

C377<br />

count.<br />

100nF<br />

C289<br />

DAC1_A<br />

100nF<br />

-5V<br />

100nF<br />

C216<br />

C74<br />

4.25mW<br />

Q15 100nF*<br />

DAC0_A<br />

4.25mW<br />

Q16 100nF*<br />

BCX70K<br />

2N7002<br />

2N7002<br />

U63<br />

Q3<br />

G<br />

U20<br />

ATWD1VDD-SUP<br />

Q1<br />

G<br />

R267 10K 1%<br />

8<br />

3<br />

8<br />

3<br />

BCX70K<br />

ATWD0VDD-SUP<br />

SC_nCS1<br />

10 CS OUTA 2<br />

SC_nCS0<br />

Analog_Ref<br />

SC_SCLK<br />

R171<br />

10<br />

CS OUTA<br />

2<br />

9<br />

SCLK FBA<br />

1.56K 1%<br />

SC_SCLK<br />

9 SCLK FBA<br />

TP4<br />

SC_MOSI<br />

DAC2_B<br />

R90 1.56K 1%<br />

DAC-DO4 12 DIN<br />

4<br />

TP5<br />

SC_MOSI<br />

DAC-DO3 12<br />

DIN<br />

4<br />

DAC0_B<br />

5.1mW<br />

DAC-UP4 13<br />

DOUT OUTB<br />

5<br />

3 DAC-UP3 13<br />

DOUT OUTB<br />

5<br />

1<br />

14<br />

UPO FBB<br />

R172 10K 1%<br />

Q4<br />

3<br />

DAC1_C<br />

1mW<br />

1<br />

14 UPO FBB<br />

R91 10K 1%<br />

7 PDL<br />

17<br />

BCX70K<br />

DAC0_C<br />

Q2<br />

MAX4166ESA<br />

SC_CL<br />

7<br />

PDL<br />

17<br />

BCX70K<br />

TP*<br />

CL OUTC<br />

16<br />

SC_CL<br />

5Vanalog<br />

5Vanalog<br />

TP*<br />

CL OUTC 16<br />

FBC<br />

U21<br />

FBC<br />

U76<br />

18<br />

PEDESTAL<br />

3<br />

TLE2425ID<br />

18<br />

3<br />

R268<br />

15<br />

OUTD<br />

19<br />

VCC 1<br />

15<br />

OUTD 19<br />

+ 6<br />

AnalogRef1<br />

6 REFCD FBD<br />

R173 10K 1%<br />

OUT<br />

6<br />

REFCD FBD<br />

R92 10K 1%<br />

2<br />

REFAB<br />

5Vanalog<br />

REFAB<br />

5Vanalog<br />

-<br />

+<br />

11<br />

11<br />

24.9 1%<br />

1<br />

DGND<br />

20<br />

1<br />

DGND<br />

20<br />

C290<br />

AGND VDD<br />

AGND VDD<br />

100nF<br />

C218<br />

MAX525BEAP<br />

C76<br />

C433 C77 C78<br />

MAX525BEAP<br />

100nF<br />

100nF<br />

OSCON_6SC6R8M 100nF 100nF<br />

GND<br />

5Vana log<br />

3 2<br />

3 2<br />

52<br />

51<br />

50<br />

49<br />

48<br />

47<br />

Gnd<br />

NC<br />

In0<br />

AnaRef0<br />

AnaRef1<br />

In1<br />

AnaRef2<br />

In2<br />

In3<br />

AnaRef3<br />

Ana Ref<br />

Op-Amp Ref<br />

Gnd<br />

Gnd<br />

Trigger Bias<br />

A-Gnd<br />

A-Gnd<br />

A-Vdd<br />

A-Vdd<br />

Op-Amp Bias Current<br />

Comparator Bias Current<br />

Ramp Top Voltage<br />

Ramp Bias Current<br />

A-Vdd<br />

A-Gnd<br />

Gnd<br />

21<br />

22<br />

23<br />

24<br />

25<br />

26<br />

27<br />

28<br />

29<br />

30<br />

31<br />

32<br />

33<br />

SDWN<br />

Vcc<br />

SDWN<br />

Vcc<br />

17<br />

49<br />

3 2<br />

3 2<br />

D<br />

52<br />

51<br />

50<br />

49<br />

48<br />

47<br />

Gnd<br />

NC<br />

In0<br />

AnaRef0<br />

In1<br />

AnaRef1<br />

AnaRef2<br />

In2<br />

In3<br />

AnaRef3<br />

Ana Ref<br />

Op-Amp Ref<br />

Gnd<br />

Gnd<br />

Trigger Bias<br />

A-Gnd<br />

A-Gnd<br />

A-Vdd<br />

A-Vdd<br />

Op-Amp Bias Current<br />

Comparator Bias Current<br />

Ramp Top Voltage<br />

Ramp Bias Current<br />

A-Vdd<br />

A-Gnd<br />

Gnd<br />

21<br />

22<br />

23<br />

24<br />

25<br />

26<br />

27<br />

28<br />

29<br />

30<br />

31<br />

32<br />

33<br />

19<br />

17<br />

38<br />

E<br />

C79 R93 R94<br />

100nF 10K 1% 10K 1%<br />

R95<br />

2K 1%<br />

R269 10K 1%<br />

C219 R174 R175<br />

100nF 10K 1% 10K 1%<br />

R176<br />

2K 1%<br />

VR2.5<br />

JU25<br />

1 2<br />

1 2<br />

If noise is bei ng<br />

coupled throug h,<br />

then put a<br />

resistor or be ad<br />

here.<br />

Jumper<br />

Power Budg et<br />

50 + 50 + 1 + 5.1 + 5.1 + 4.25 + 4.25 + 2xATWD mW<br />

R147<br />

2K 1%<br />

5Vanalog<br />

R276<br />

R2BUS7<br />

1<br />

16<br />

C278<br />

100nF<br />

Could be a lower power part with greater<br />

delay, like max998, if it is ne cessary<br />

to save 6mW .<br />

5Vanalog<br />

C173<br />

10nF<br />

5Vanalog<br />

C171<br />

10nF<br />

R2BUS6<br />

R2BUS5<br />

R2BUS4 4<br />

13<br />

VR2.5<br />

C277<br />

U71 MAX9013EUA<br />

U72 MAX9013EUA<br />

-5V<br />

100nF<br />

2<br />

7 ATWD_A_CC<br />

2<br />

7 ATWD_B_CC<br />

CounterClock_0 + CounterClock_1 + R2BUS3 5<br />

12<br />

3<br />

Use a low volta ge<br />

2<br />

-<br />

8<br />

3<br />

Latch 5<br />

-<br />

8<br />

Latch 5<br />

2<br />

driving standard. Wi red<br />

R2BUS2 6<br />

11 to a low voltage I /O<br />

bank of the FP GA<br />

1.65V<br />

C130<br />

10nF<br />

C131<br />

10nF<br />

R402<br />

5.11K 1%<br />

R403<br />

10K 1%<br />

R2BUS[0..7]<br />

R2BUS1<br />

R2BUS0<br />

2<br />

3<br />

7<br />

8 9<br />

R2R-LADDER-16<br />

15<br />

14<br />

10<br />

U57<br />

3<br />

4<br />

+<br />

-<br />

1<br />

AD8005RT<br />

R148<br />

20<br />

R150<br />

Open Ckt<br />

C279<br />

1 2<br />

100nF<br />

PULSE<br />

R149<br />

24.9K 1%<br />

CTS 766-16-7-10 1-D<br />

SEMICONWEL L<br />

2964-2966 Sco tt<br />

Blvd. Santa Cla ra,<br />

CA 95054<br />

Tel:(408)986-8 026<br />

Fax:(408)-850-19 11,<br />

or equivalen t.<br />

1 1<br />

Title<br />

Digital Optical Module ATWD<br />

Size Document Number Rev<br />

D <br />

<br />

A<br />

B<br />

C<br />

D<br />

E<br />

Friday, May 16, 2003<br />

Date: Sheet of 7 15

A<br />

7<br />

8<br />

4<br />

1<br />

2<br />

2<br />

1<br />

8<br />

1<br />

7<br />