Week 10: MOS Logic Circuits

Week 10: MOS Logic Circuits

Week 10: MOS Logic Circuits

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

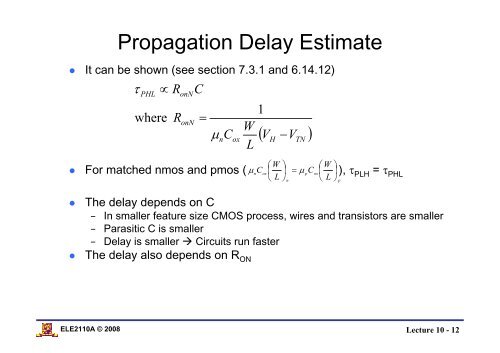

Propagation Delay Estimate<br />

• It can be shown (see section 7.3.1 and 6.14.12)<br />

τ<br />

PHL<br />

∝<br />

where<br />

R<br />

R<br />

onN<br />

onN<br />

µ<br />

nCox<br />

( VH<br />

−VTN<br />

)<br />

⎛W<br />

⎞<br />

µ C ⎜ ⎟ = µ<br />

⎝ L ⎠ n<br />

• The delay also depends on R ON<br />

C<br />

=<br />

• For matched nmos and pmos ( n ox<br />

p ox ), τ PLH = τ PHL<br />

W<br />

L<br />

• The delay depends on C<br />

– In smaller feature size C<strong>MOS</strong> process, wires and transistors are smaller<br />

– Parasitic C is smaller<br />

– Delay is smaller <strong>Circuits</strong> run faster<br />

1<br />

C<br />

⎛ W ⎞<br />

⎜ ⎟<br />

⎝ L ⎠<br />

p<br />

ELE21<strong>10</strong>A © 2008<br />

Lecture <strong>10</strong> - 12