制御応答の高速化による直流コンデンサ容量の最小 ... - 長岡技術科学大学

制御応答の高速化による直流コンデンサ容量の最小 ... - 長岡技術科学大学

制御応答の高速化による直流コンデンサ容量の最小 ... - 長岡技術科学大学

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

プではなく, 負 荷 抵 抗 ステップによる 模 擬 を 行 っているこ<br />

とによる 影 響 である。また,コンデンサの 等 価 直 列 抵 抗<br />

(ESR)の 影 響 , 変 換 器 の 損 失 によるダンピング 効 果 , 使 用<br />

したコンデンサ 容 量 の 誤 差 などがある。<br />

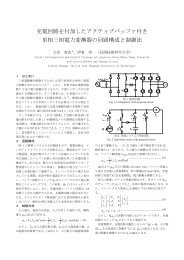

図 15 に 電 圧 変 動 V ou を 0.2p.u.と 設 定 したとき 負 荷 抵 抗 ス<br />

テップによる 電 圧 変 動 をグラフ 化 した 結 果 を 示 す。これよ<br />

り, 算 出 したV out は 計 算 式 に 対 し 低 い 値 となっていること<br />

がわかる。 誤 差 の 原 因 は 先 述 の 影 響 が 現 れているためであ<br />

る。<br />

6. まとめ<br />

本 論 文 では, 昇 圧 チョッパの 電 流 制 御 系 と 出 力 電 圧 制<br />

御 系 の 限 界 応 答 設 計 について 述 べた。 入 力 電 流 制 御 にデ<br />

ッドビート 制 御 器 を 用 いたとき, 目 標 とする 応 答 周 波 数<br />

f d の 3.15 倍 程 度 以 上 にサンプリング 周 波 数 (キャリア 周<br />

波 数 )を 設 定 すればよいことを 明 らかにした。<br />

また, 電 圧 制 御 系 において 負 荷 電 流 ステップ 入 力 時 に<br />

おける 出 力 電 圧 変 動 量 と 電 圧 制 御 固 有 角 周 波 数 ,コンデ<br />

ンサ C の 関 係 性 を 定 式 化 し,これらの 関 係 を 明 らかにし<br />

た。また,シミュレーションにより, 電 圧 制 御 固 有 角 周<br />

波 数 は 1000rad/sec 以 下 である 必 要 があることを 明 らかに<br />

した。さらに 検 証 実 験 を 行 い, 電 圧 変 動 値 を 0.2p.u., 固<br />

有 角 周 波 数 を 100rad/sec としたとき, 電 圧 変 動 誤 差 は 設 計<br />

値 に 対 して 8.53%であり,おおむね 理 論 と 一 致 している。<br />

以 上 より,これらの 設 計 指 針 の 有 効 性 を 確 認 した。<br />

文<br />

(1) K. Kouno, Y. Ishiyama, M. Yamamoto:“Optimum Design of Trans-linked<br />

method single phase interleaved PFC converter”, JIASC IEEJ,H23,1-74<br />

河 野 研 太 , 石 倉 祐 樹 , 山 本 真 義 :「トランスリンク 方 式 単 層 インター<br />

リーブ PFC コンバータの 最 適 設 計 方 法 」 平 成 23 年 産 業 応 用 部 門 大<br />

会 1-74<br />

(2) T. Fushimi, H. Haga, S. Kondo:“Control Method of Electrolytic Capacitor<br />

Less Buck-boost Converter for Single-phase UPS”, JIASC IEEJ,H23,<br />

1-82<br />

伏 見 高 明 , 芳 賀 仁 , 近 藤 正 示 :「 電 解 コンデンサレス 昇 降 圧 チョッパ<br />

を 用 いた 常 時 商 用 単 層 UPS の 小 型 化 への 検 討 」<br />

平 成 23 年 産 業 応 用 部 門 大 会 1-82<br />

(3) Y. Nakamura, M. Nakahama, M. Yamamoto:“Frequency Property Analysis<br />

of Multi-phase Boost Chopper Circuit”, IEEJ annual meeting,H22,<br />

4-009<br />

中 村 祐 太 , 中 浜 真 之 , 山 本 真 義 :「マルチフェーズ 昇 圧 チョッパ 回 路<br />

の 周 波 数 特 性 解 析 」 平 成 22 年 電 気 学 会 全 国 大 会 大 会 4-009<br />

(4) T. Mishima, M. Hattori, D. Tukiyama, Shuuji Miyake, M. Nakaoka:<br />

“Optimum Design of Trans-linked method single phase interleaved PFC<br />

converter”, IEEJ annual meeting,H22,4-014<br />

三 島 智 和 , 服 部 将 之 , 築 山 大 輔 , 三 宅 修 二 , 中 岡 睦 雄 :「トランスリン<br />

ク 方 式 単 層 インターリーブ PFC コンバータの 最 適 設 計 方 法 」 平 成 22<br />

年 電 気 学 会 全 国 大 会 大 会 4-014<br />

(5) K. Mathuura, J. Itoh:“A Loss Analysis of a 3-Level switched capacitor<br />

DC-DC Converter”, SPC-11-098<br />

松 浦 浩 一 , 伊 東 淳 一 :「 低 インダクタによる 高 昇 圧 比 向 け DC-DC コ<br />

ンバータの 基 礎 検 討 」, 半 導 体 電 力 変 換 研 究 会 ,SPC-10-104(2010)<br />

(6) T. Yokoyama, T. Komiyama, E. Shimada:Current Control for Utility<br />

Interactive Inverter Using Multisampling Method Based on FPGA” IEEJ<br />

Trans.1A, Vol.130, No.1, 2010, pp.51-59<br />

献<br />

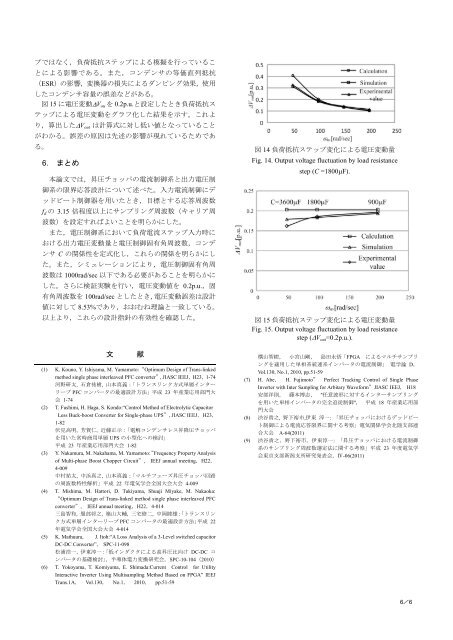

図 14 負 荷 抵 抗 ステップ 変 化 による 電 圧 変 動 量<br />

Fig. 14. Output voltage fluctuation by load resistance<br />

step (C =1800F).<br />

図 15 負 荷 抵 抗 ステップ 変 化 による 電 圧 変 動 量<br />

Fig. 15. Output voltage fluctuation by load resistance<br />

step (V out =0.2p.u.).<br />

横 山 智 樹 , 小 宮 山 剛 , 島 田 永 悟 「FPGA によるマルチサンプリ<br />

ングを 適 用 した 単 相 系 統 連 系 インバータの 電 流 制 御 」 電 学 論 D,<br />

Vol.130, No.1, 2010, pp.51-59<br />

(7) H. Abe, H. Fujimoto” Perfect Tracking Control of Single Phase<br />

Inverter with Inter Sampling for Arbitary Waveform”JIASC IEEJ, H18<br />

安 部 洋 則 , 藤 本 博 志 , " 任 意 波 形 に 対 するインターサンプリング<br />

を 用 いた 単 相 インバータの 完 全 追 従 制 御 ", 平 成 18 年 産 業 応 用 部<br />

門 大 会<br />

(8) 渋 谷 貴 之 , 野 下 裕 市 , 伊 東 淳 一 : 「 昇 圧 チョッパにおけるデッドビー<br />

ト 制 御 による 電 流 応 答 限 界 に 関 する 考 察 」 電 気 関 係 学 会 北 陸 支 部 連<br />

合 大 会 A-64(2011)<br />

(9) 渋 谷 貴 之 , 野 下 裕 市 , 伊 東 淳 一 : 「 昇 圧 チョッパにおける 電 流 制 御<br />

系 のサンプリング 周 波 数 選 定 法 に 関 する 考 察 」 平 成 23 年 度 電 気 学<br />

会 東 京 支 部 新 潟 支 所 研 究 発 表 会 ,Ⅳ-06(2011)<br />

6/6