制御応答の高速化による直流コンデンサ容量の最小 ... - 長岡技術科学大学

制御応答の高速化による直流コンデンサ容量の最小 ... - 長岡技術科学大学

制御応答の高速化による直流コンデンサ容量の最小 ... - 長岡技術科学大学

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

SPC-12-026<br />

制 御 応 答 の 高 速 化 による 直 流 コンデンサ 容 量 の 最 小 化 の 検 討<br />

渋 谷 貴 之 * 伊 東 淳 一 ( 長 岡 技 術 科 学 大 学 )<br />

An Evaluation of Optimal Design of Capacitance<br />

by High Speed of a Control Response.<br />

Takayuki Shibuya, Jun-ichi Itoh (Nagaoka University of Technology)<br />

This paper describes an optimal design method for a current regulator and an output voltage regulator with a DC link capacitor in a<br />

boost-up chopper. In order to reduce the DC link capacitor and boost-up reactor, high speed response of the current regulator and the output<br />

voltage regulator are required. In this paper, the current controller is designed based on dead-beat control with P, PI or IP structure. Then, it<br />

is confirmed that the control response of dead –beat controller becomes 1/3.15 of the sampling frequency, which is the switching frequency.<br />

The minimum output capacitor is calculated by the control response of the output voltage regulator and the allowance of the voltage<br />

fluctuation. Moreover, the validities of the design method are confirmed by experimental results that the design values agree well with the<br />

analysis result with 8.53% error.<br />

キーワード: 昇 圧 チョッパ, 自 動 電 流 制 御 , 自 動 電 圧 制 御 ,デッドビート 制 御<br />

(Boost chopper, ACR, AVR, Deadbeat control)<br />

1. はじめに<br />

近 年 , 電 気 自 動 車 ( 以 下 EV),スマートグリッドをはじめ<br />

として 大 容 量 の DC-DC コンバータが 注 目 されている。また,<br />

DC-DC コンバータの 高 効 率 化 , 小 型 化 に 対 する 要 求 が 高 ま<br />

っており, 昇 圧 リアクトルや 平 滑 コンデンサなどの 受 動 素<br />

子 を 小 型 化 する 技 術 について 盛 んに 研 究 されている (1)-(5) 。<br />

EV や 太 陽 光 インバータで 使 用 される 昇 圧 チョッパでは,<br />

平 滑 コンデンサや 昇 圧 リアクトルを 小 型 化 すると 負 荷 ステ<br />

ップ 応 答 に 対 する 出 力 電 圧 変 動 や 入 力 電 圧 変 化 に 対 する 入<br />

力 電 流 の 変 動 は 大 きくなる。これを 抑 制 するためには, 電<br />

圧 制 御 , 電 流 制 御 の 高 速 化 が 有 効 である。<br />

DC-DC コンバータの 制 御 方 法 として, 制 御 器 に DSP や<br />

FPGA を 用 いたデジタル 制 御 を 適 用 する 研 究 が 盛 んに 行 わ<br />

れている (6)-(9) 。 近 年 , 特 に FPGA の 発 展 により 非 常 に 高 速 で<br />

制 御 することが 可 能 になっている。 従 来 , 電 流 制 御 として<br />

比 例 ゲインと 積 分 器 から 構 成 される PI 制 御 がよく 使 用 され<br />

ている。 一 方 ,デジタル 制 御 系 では,n サンプルで 目 標 値 に<br />

追 従 できるデッドビート 制 御 やマルチレートサンプリング<br />

などが 研 究 されており, 高 速 サンプリングより 高 性 能 化 を<br />

実 現 している。 確 かに FPGA による 高 速 サンプリングを 行<br />

うことで, 制 御 性 能 を 飛 躍 的 に 向 上 させることができるが,<br />

平 滑 コンデンサ 容 量 と 電 圧 制 御 応 答 の 関 係 は 明 確 化 されて<br />

いない。また, 実 際 には, 電 圧 制 御 応 答 には 限 界 があり,<br />

その 制 約 条 件 を 定 量 的 に 考 察 した 文 献 は 著 者 らの 知 る 限 り<br />

ない。<br />

本 論 文 では, 昇 圧 チョッパを 例 に 取 り, 電 流 制 御 と 電 圧<br />

制 御 の 設 計 法 とそれぞれの 応 答 限 界 について 考 察 する。 出<br />

力 電 圧 制 御 に PI 制 御 を 用 い, 入 力 電 流 の 制 御 には,P 制 御 ,<br />

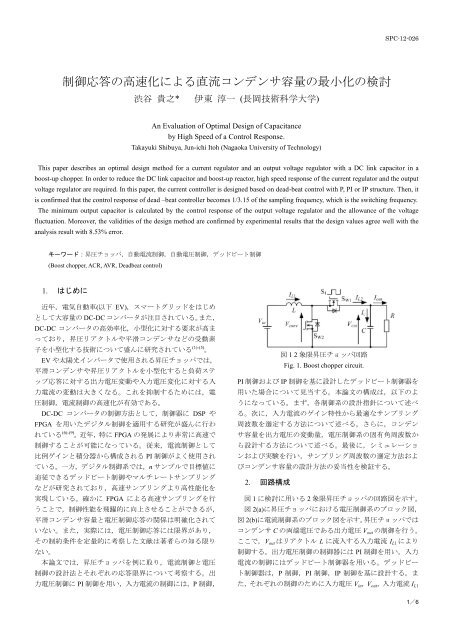

図 1 2 象 限 昇 圧 チョッパ 回 路<br />

Fig. 1. Boost chopper circuit.<br />

PI 制 御 および IP 制 御 を 基 に 設 計 したデッドビート 制 御 器 を<br />

用 いた 場 合 について 見 当 する。 本 論 文 の 構 成 は, 以 下 のよ<br />

うになっている。まず, 各 制 御 系 の 設 計 指 針 について 述 べ<br />

る。 次 に, 入 力 電 流 のゲイン 特 性 から 最 適 なサンプリング<br />

周 波 数 を 選 定 する 方 法 について 述 べる。さらに,コンデン<br />

サ 容 量 を 出 力 電 圧 の 変 動 量 , 電 圧 制 御 系 の 固 有 角 周 波 数 か<br />

ら 設 計 する 方 法 について 述 べる。 最 後 に,シミュレーショ<br />

ンおよび 実 験 を 行 い,サンプリング 周 波 数 の 選 定 方 法 およ<br />

びコンデンサ 容 量 の 設 計 方 法 の 妥 当 性 を 検 証 する。<br />

2. 回 路 構 成<br />

図 1 に 検 討 に 用 いる 2 象 限 昇 圧 チョッパの 回 路 図 を 示 す。<br />

図 2(a)に 昇 圧 チョッパにおける 電 圧 制 御 系 のブロック 図 ,<br />

図 2(b)に 電 流 制 御 系 のブロック 図 を 示 す。 昇 圧 チョッパでは<br />

コンデンサ C の 両 端 電 圧 である 出 力 電 圧 V out の 制 御 を 行 う。<br />

ここで,V out はリアクトル L に 流 入 する 入 力 電 流 I L1 により<br />

制 御 する。 出 力 電 圧 制 御 の 制 御 器 には PI 制 御 を 用 い, 入 力<br />

電 流 の 制 御 にはデッドビート 制 御 器 を 用 いる。デッドビー<br />

ト 制 御 器 は,P 制 御 ,PI 制 御 ,IP 制 御 を 基 に 設 計 する。ま<br />

た,それぞれの 制 御 のために 入 力 電 圧 V in ,V out , 入 力 電 流 I L1<br />

1/6

を 検 出 する。ここで,V in は 簡 単 化 のため 定 電 圧 源 を 用 いる。<br />

3. 制 御 方 法<br />

〈3・1〉 出 力 電 圧 制 御<br />

コンデンサ C の 両 端 電 圧 である 出 力 電 圧 制 御 には PI 制 御<br />

を 用 いる。ここで 電 流 制 御 系 ACR は 電 圧 制 御 系 AVR の 応<br />

答 に 対 して 十 分 に 高 速 であると 仮 定 し,ゲイン1のシステ<br />

ムと 仮 定 する。<br />

(a) AVR (Auto Voltage Regulation).<br />

出 力 電 圧 はコンデンサ 電 流 I c により 決 定 する。ここで I c<br />

は(1) 式 となる。<br />

I<br />

c<br />

IL<br />

2<br />

I<br />

out<br />

.............................................................. (1)<br />

これより,チョッパ 出 力 電 流 I L2 により I c を 制 御 すること<br />

ができる。ここで 負 荷 電 流 I out を 外 乱 とする。しかし, 実 際<br />

に 制 御 できる 電 流 は 入 力 電 流 I L1 のみであるため,I L2 から I L1<br />

への 変 換 が 必 要 になる。<br />

図 3 に 入 力 電 流 とチョッパ 出 力 電 流 の 関 係 図 を 示 す。I L1<br />

は S w1 によりスイッチングされ,I L2 となる。これより,チ<br />

ョッパの 変 調 率 をとすると I L1 と I L2 の 関 係 は(2) 式 となる。<br />

I<br />

I<br />

...................................................................(2)<br />

L2 L1<br />

これより, 入 力 電 流 指 令 値 I L1 *は(3) 式 となる。<br />

1<br />

I L<br />

I<br />

<br />

1* L2<br />

*<br />

............................................................. (3)<br />

ここで, 変 調 率 はチョッパの 昇 圧 比 をで 表 すと 定 常 状<br />

態 では 1/と 等 しくなる。また, 電 圧 制 御 系 の 閉 ループ 伝 達<br />

関 数 伝 達 関 数 G V は(4) 式 となる。<br />

G<br />

V<br />

<br />

s<br />

2<br />

KVI<br />

C<br />

K<br />

PV<br />

K<br />

s <br />

C C<br />

IV<br />

........................................... (4)<br />

電 圧 制 御 系 AVR における PI 制 御 器 のゲイン K PV および<br />

K IV は AVR の 閉 ループ 伝 達 関 数 と 2 次 標 準 形 と 比 較 すること<br />

で 設 計 し, 式 (5)となる。<br />

(b) ACR (Auto Current Regulation).<br />

図 2 システムブロック 図<br />

Fig. 2. System block diagram.<br />

K<br />

PV<br />

2<br />

C,<br />

K<br />

nv<br />

IV<br />

<br />

2 nv<br />

C<br />

,<br />

.................................... (5)<br />

〈3・2〉 入 力 電 流 制 御<br />

リアクトル L に 流 入 する 入 力 電 流 制 御 には n サンプル<br />

で 制 御 対 象 を 指 令 値 に 追 従 することが 可 能 であるデッドビ<br />

ート 制 御 を 適 用 する。これは 電 圧 制 御 における 入 力 電 流 制<br />

御 の 影 響 を 小 さくするためである。<br />

ここで 電 流 制 御 系 には P 制 御 器 ,PI 制 御 器 ,IP 制 御 器 を<br />

用 いる。また, 図 2(b)より,それぞれの 制 御 器 を 用 いた 電 流<br />

制 御 系 の 離 散 閉 ループ 伝 達 関 数 G P ,G PI ,G IP を(6) 式 ,(7) 式 ,<br />

(8) 式 に 示 す。<br />

T<br />

K<br />

PP<br />

G<br />

P<br />

<br />

L<br />

..................................................(6)<br />

T<br />

z K<br />

PP<br />

1<br />

L<br />

G<br />

図 3 入 力 電 流 とチョッパ 出 力 電 流 の 関 係<br />

Fig. 3. Relation between the input current and chopper<br />

PI<br />

<br />

z<br />

2<br />

K<br />

(<br />

L<br />

output current.<br />

PIP<br />

T<br />

( z 1)<br />

K<br />

PIP<br />

K<br />

L<br />

K<br />

T 2) z 1<br />

L<br />

<br />

PIP<br />

PII<br />

<br />

K<br />

T <br />

L<br />

PII<br />

T<br />

<br />

<br />

<br />

K<br />

IPI 2<br />

T<br />

L1<br />

GIP <br />

(8)<br />

2 K<br />

IPD K<br />

IPD<br />

K<br />

IPI 2 <br />

z ( T 2) z 1<br />

T T <br />

L L L <br />

2<br />

(7)<br />

2/6

ここで, 図 2(b-2)の PI 制 御 系 における 目 標 値 フィルタは<br />

制 御 系 のゼロ 点 を 打 ち 消 すフィルタである。また,T はサン<br />

プリング 時 間 とする。これより,それぞれの 閉 ループ 伝 達<br />

関 数 における 極 がすべてゼロになるようにそれぞれの 制 御<br />

器 のゲインを 設 計 し,デッドビート 制 御 を 実 現 する。その<br />

結 果 G P =1/z,G PI =G IP =1/z 2 となり,P 制 御 系 は 1 サンプル<br />

後 に 指 令 値 に 追 従 ,PI 制 御 系 ,IP 制 御 系 は 2 サンプル 後 に<br />

指 令 値 に 追 従 するシステムとなる。<br />

〈3・3〉 電 流 制 御 におけるサンプリング 周 波 数 選 定<br />

本 章 では 電 流 制 御 にデッドビート 制 御 を 適 用 した 際 のサ<br />

ンプリング 周 波 数 の 選 定 法 について 検 討 を 行 う。<br />

図 4 にデッドビート 応 答 の 近 似 モデルのタイミングチャ<br />

ートを 示 す。ここで 電 流 指 令 値 を 振 幅 I m の 正 弦 波 とする。P<br />

制 御 系 は 1 サンプル 後 に 指 令 値 に 追 従 ,PI 制 御 系 ,IP 制 御<br />

系 は 2 サンプル 後 に 指 令 値 に 追 従 するシステムである。こ<br />

のため PI 制 御 ,IP 制 御 系 の 波 形 は P 制 御 の 1 サンプル 遅 れ<br />

の 結 果 であり,ゲイン 特 性 は 同 じ 結 果 になる。<br />

図 5 にサンプリング 周 波 数 f s に 対 して 電 流 指 令 値 周 波 数<br />

f ref を 変 動 させたときの I L1 のゲイン 特 性 を 示 す。これより,<br />

サンプリング 周 波 数 が 指 令 値 周 波 数 に 対 して 高 いときゲイ<br />

ン 低 下 は 抑 制 されていることが 確 認 できる。ここで,ゲイ<br />

ン 低 下 許 容 を 3dB と 仮 定 すると,f ref / f s = 1/3.15 となる。し<br />

たがって,このときの 指 令 値 周 波 数 f ref を 所 望 の 電 流 制 御 応<br />

答 周 波 数 f d とすると,f s は f d の 3.15 倍 程 度 に 設 計 する 必 要<br />

がある。<br />

〈3・4〉 出 力 電 圧 変 動 とコンデンサ 容 量 の 関 係<br />

コンデンサ 両 端 の 出 力 電 圧 は 負 荷 変 動 により 変 動 する。<br />

本 節 では 負 荷 電 流 I out がステップ 変 動 したときの 電 圧 変 動 と<br />

コンデンサ, 電 圧 制 御 応 答 の 関 係 の 定 式 化 を 行 う。ここで,<br />

電 流 制 御 系 ACR の 応 答 は 電 圧 制 御 系 AVR の 応 答 よりも 十<br />

分 に 高 速 であると 仮 定 し,ACR のゲインは1,つまり I L2 *<br />

=I L2 と 仮 定 する。 負 荷 電 流 を 入 力 とした 場 合 の 外 乱 閉 ルー<br />

プ 伝 達 関 数 G load (s)は(9) 式 となる。<br />

G<br />

load<br />

1<br />

s<br />

( s)<br />

<br />

C ......................................(9)<br />

2<br />

s 2 s <br />

nv<br />

2<br />

nv<br />

ここで, 減 衰 係 数 z は 0.707 とし, 固 有 角 周 波 数 nv は 設<br />

計 値 とする。したがって,G load (s)の 単 位 ステップ 応 答 C load (t)<br />

は(10) 式 となる。<br />

C<br />

load<br />

( t)<br />

L<br />

-1<br />

<br />

G<br />

<br />

<br />

C<br />

load<br />

nv<br />

1<br />

( s)<br />

<br />

s<br />

<br />

1<br />

e<br />

2<br />

1<br />

<br />

sin<br />

<br />

<br />

1<br />

t <br />

<br />

<br />

nt<br />

2<br />

nv<br />

..... (10)<br />

出 力 電 圧 変 動 の 最 大 値 は 単 位 ステップ 応 答 におけるオー<br />

バーシュートと 同 等 になる。したがって 最 大 電 圧 変 動 量<br />

V out は(10) 式 を 微 分 し 傾 きがゼロとなる 時 間 で 求 まり,この<br />

ときの 時 間 T p は(11) 式 となる。<br />

T p<br />

<br />

<br />

nv<br />

1<br />

1<br />

<br />

tan<br />

1<br />

( <br />

2 <br />

2<br />

1<br />

<br />

)<br />

............................ (11)<br />

これより 負 荷 電 流 ステップI out によるV out は(10) 式 に(11)<br />

式 を 代 入 することで 求 まり,(12) 式 となる。<br />

V<br />

out<br />

I<br />

out<br />

<br />

e<br />

2<br />

C<br />

1 <br />

nv<br />

K<br />

a<br />

<br />

C<br />

nv<br />

I<br />

out<br />

2 <br />

1<br />

1<br />

<br />

tan <br />

2<br />

1<br />

<br />

<br />

<br />

1<br />

sin tan<br />

<br />

<br />

2<br />

1 <br />

<br />

<br />

<br />

<br />

<br />

..................................................................................... (12)<br />

ここで,I out は 負 荷 電 流 のステップ 変 化 量 である。また,<br />

K a に 含 まれるは 定 数 であるため 一 定 となる。よって 電 圧 変<br />

動 量 V out はコンデンサ C と 固 有 角 周 波 数 nv に 反 比 例 の 関<br />

係 となる。これより C は 許 容 電 圧 変 動 と nv から 求 まり,(13)<br />

式 となる。<br />

C<br />

図 4 入 力 電 流 タイミングチャート<br />

Fig. 4. Timing chart of input current.<br />

図 5 電 流 近 似 モデルゲイン 特 性<br />

Fig. 5. Gain characteristic by sampling frequency.<br />

I<br />

out a<br />

............................................................(13)<br />

out<br />

K<br />

V<br />

<br />

nv<br />

(13) 式 より,コンデンサ 容 量 の 設 計 が 可 能 である。<br />

4. シミュレーション 結 果<br />

〈4・1〉 電 流 制 御 系 におけるゲイン 特 性<br />

3/6

本 節 では 3 章 において 導 出 したサンプリング 周 波 数 の 妥<br />

当 性 を 示 す。ここでシミュレーション 条 件 は, 入 力 電 圧 V in =<br />

1p.u., 出 力 電 圧 V out = 2p.u., 入 力 電 流 振 幅 I m = 1p.u.,リアク<br />

トル L = 0.16msec である。また,それぞれの 制 御 系 のサンプ<br />

リング 周 波 数 を 目 標 の 応 答 周 波 数 f s = 3.15f ref とする。なお,<br />

それぞれのパラメータは 入 力 電 圧 V in =25V,および 定 格 電 流<br />

I n =4A で 基 準 化 した 値 である。<br />

図 6 にシミュレーションにおける 入 力 電 流 I L1 の 周 波 数 応<br />

答 を 示 す。 結 果 より, 指 令 値 周 波 数 f ref が 所 望 応 答 周 波 数 f d<br />

に 近 づくことでゲイン 特 性 が 低 下 していることがわかる。<br />

また,P 制 御 ,PI 制 御 ,IP 制 御 のすべての 制 御 系 において,<br />

f ref = f d で 設 定 したゲイン 低 下 許 容 3dB とほぼ 一 致 している<br />

ことが 確 認 できる。 以 上 より, 制 御 系 の 形 によらず,ゼロ<br />

点 を 含 まないデッドビート 制 御 系 では f s を f d の 3.15 倍 程 度<br />

に 設 定 すればよいことがわかる。<br />

〈4・2〉 出 力 電 圧 応 答 特 性<br />

本 節 では 3 章 において 検 討 した 出 力 電 圧 変 動 量 V out とコ<br />

ンデンサ 容 量 および 固 有 角 周 波 数 との 関 係 性 について 検 討<br />

する。ここでシミュレーション 条 件 は, 入 力 電 圧 V in = 1p.u.,<br />

リアクトル L = 0.32msec,コンデンサ 容 量 C = 11.3msec, 電<br />

圧 制 御 固 有 角 周 波 数 nv = 100rad/sec, 電 流 制 御 固 有 角 周 波 数<br />

d = 2πf d = 20000rad/sec,サンプリング 周 波 数 f s = 3.15f d =<br />

10kHz とした。<br />

図 7 に 出 力 電 圧 指 令 値 V out *を 2p.u.から 2.4p.u.へ 変 動 させ<br />

たときの 出 力 電 圧 応 答 および 電 流 応 答 の 結 果 を 示 す。ここ<br />

で,V out_ideal は 理 想 モデルの 制 御 ブロック 図 より 取 得 した 出<br />

力 電 圧 である。その 結 果 ,V out は V out_ideal とほぼ 一 致 するこ<br />

とから 制 御 系 は 設 計 通 りの 応 答 を 得 られていることを 確 認<br />

した。<br />

図 8 に 負 荷 電 流 I out を 0p.u.から 0.5 p.u.へステップ 変 化 さ<br />

せたときの 電 圧 応 答 および 電 流 応 答 の 結 果 を 示 す。これよ<br />

り, 負 荷 電 流 ステップによる 電 圧 変 動 量 V out は 0.199p.u.,<br />

V out_ideal = 0.203p.u.であり, 電 圧 変 動 誤 差 は 1.97%であるこ<br />

とを 確 認 した。<br />

図 9 に 負 荷 ステップ 応 答 において 電 圧 制 御 固 有 角 周 波 数<br />

nv を 変 化 させたときの 電 圧 変 動 を 示 す。これより,(11) 式<br />

より 算 出 したV out_cal は 理 想 モデル 電 圧 変 動 とほぼ 一 致 する<br />

ことが 確 認 できる。また, 計 算 式 同 様 にV out_cal は nv に 反 比<br />

例 することを 確 認 した。したがって 算 出 した 出 力 電 圧 変 動<br />

式 の 妥 当 性 を 確 認 した。ここで,シミュレーションモデル<br />

が 理 想 モデルや 計 算 結 果 と 誤 差 が 発 生 している 原 因 は 本 来<br />

入 力 電 流 指 令 I L1 *は I L2 *に 対 し 変 調 率 で 補 償 するところを<br />

本 制 御 では 定 常 状 態 における 変 調 率 = 1/で 補 償 している<br />

ためである。<br />

図 10 に 電 圧 変 動 V out を 0.2p.u.と 設 定 したとき 負 荷 電 流 ス<br />

テップによる 電 圧 変 動 をグラフ 化 した 結 果 を 示 す。ここで<br />

コンデンサ 容 量 は(12) 式 から 設 計 を 行 った。また,このとき<br />

の 電 圧 制 御 固 有 角 周 波 数 nv は 50rad/sec , 100rad/sec ,<br />

200rad/sec とする。シミュレーションと 計 算 結 果 に 若 干 誤 差<br />

が 発 生 しているのは 上 記 の 補 償 法 が 影 響 しているためであ<br />

図 6 入 力 電 流 ゲイン 特 性<br />

Fig. 6. Gain characteristic of the input current.<br />

る。これより,(12) 式 を 用 いることで 電 圧 変 動 と 電 圧 固 有 角<br />

周 波 数 からコンデンサ 容 量 を 設 計 することが 可 能 であるこ<br />

とを 確 認 した。<br />

図 7 電 圧 ステップ 応 答<br />

Fig. 7. Voltage step response.<br />

図 8 負 荷 電 流 ステップ 応 答<br />

Fig. 8. Load current step response.<br />

図 9 負 荷 電 流 ステップ 変 化 による 電 圧 変 動 量<br />

Fig. 9. The output voltage fluctuation by load current step<br />

(C =1800F).<br />

4/6

〈4・3〉 電 圧 制 御 系 の 最 大 固 有 角 周 波 数 の 検 討<br />

前 節 までの 考 察 により, 電 圧 制 御 の 固 有 角 周 波 数 nv によ<br />

り, 平 滑 コンデンサの 値 は 定 まることがわかった。しかし,<br />

制 御 遅 れや 操 作 量 の 飽 和 により, 電 圧 制 御 固 有 角 周 波 数 を<br />

高 くすることには 限 界 がある。ここでは 電 流 制 御 系 はデッ<br />

ドビート 制 御 を 仮 定 し,1/z と 置 いて, 制 御 遅 れを 模 擬 して<br />

いる。デッドビート 制 御 は 1 サンプル 以 内 に 電 流 が 指 令 値<br />

に 追 従 させなくてはならない。しかし, 電 流 の 変 化 率 は 昇<br />

圧 リアクトルと 電 源 電 圧 により 制 限 される。すなわち,1 サ<br />

ンプル 以 内 で 追 従 させるには, 電 流 のステップ 幅 は V in T/L<br />

以 下 でなくてはならない。ここでは 制 御 余 裕 をみて, 負 荷<br />

電 流 のステップ 変 化 幅 をI out = 0.8V in T/L とした。<br />

図 11 に 電 圧 制 御 固 有 角 周 波 数 nv を 変 化 させたときのシ<br />

ミュレーションによって 求 めた 出 力 電 圧 変 動 量 V out を 示<br />

す。 結 果 より,V outは nv が 1000rad/sec 付 近 から 計 算 によ<br />

り 算 出 した 結 果 に 対 し 誤 差 が 大 きくなり,3000rad/sec 付 近<br />

でそれ 以 上 電 圧 変 動 を 抑 えることができなくなる。サンプ<br />

リング 周 波 数 は 10kHz であるので,サンプリング 周 波 数 の<br />

約 1/20 付 近 で 飽 和 する。これは nv が 高 くなることにより 電<br />

流 制 御 系 の 制 御 遅 れによって 電 圧 制 御 系 の 応 答 が 遅 くなる<br />

ためである。したがって, 電 圧 制 御 系 の 応 答 周 波 数 はスイ<br />

ッチング 周 波 数 の 1/20 程 度 が 限 界 である。<br />

5. 実 験 結 果<br />

本 章 では 実 験 による 基 本 動 作 検 証 および 3 章 で 検 討 した<br />

コンデンサ 容 量 の 設 計 による 電 圧 変 動 について 検 討 を 行<br />

う。ここで,シミュレーションおよび 実 験 における 負 荷 電<br />

流 のステップは 負 荷 抵 抗 のステップ 変 化 で 模 擬 した。また,<br />

実 験 条 件 は, 入 力 電 圧 V in = 1p.u., 出 力 電 圧 V out = 2p.u.,リ<br />

アクトル L = 0.8msec,サンプリング 周 波 数 fs = 3.15f d =<br />

10kHz, 負 荷 抵 抗 R=4p.u.である。なお,それぞれのパラメ<br />

ータは 入 力 電 圧 V in =25V,および 定 格 電 流 I n =4A で 基 準 化 し<br />

た 値 である。<br />

図 12 に 出 力 電 圧 指 令 値 V out *を 2p.u から 2.4p.u.へステッ<br />

プ 変 化 させたときの 応 答 特 性 を 示 す。その 結 果 , 出 力 電 圧<br />

応 答 における 行 き 過 ぎ 時 間 T ps は 42.4msec であることを 確<br />

認 した。2 次 標 準 形 のステップ 応 答 における 行 き 過 ぎ 時 間<br />

T ps_ideal は 44.4msec であることから, 実 機 の 制 御 系 の 応 答 は<br />

誤 差 4.5%であり, 大 概 設 計 通 りの 応 答 を 得 られていること<br />

が 確 認 できる。<br />

図 13 に 負 荷 抵 抗 R を 0p.u.から 4p.u.へステップ 変 化 させ<br />

たときの 応 答 波 形 を 示 す。これより, 負 荷 電 流 ステップに<br />

よる 電 圧 変 動 量 V out は 1.86p.u.であることを 確 認 した。(12)<br />

式 より 算 出 したV out_cal =0.203p.u.である。したがって, 計 算<br />

式 との 誤 差 は 8.53%である。<br />

図 14 に 負 荷 抵 抗 R を 0p.u.から 4p.u.へステップ 変 化 させ<br />

たときの 電 圧 変 動 量 の 電 圧 変 動 量 をグラフ 化 したものを 示<br />

す。 結 果 より,シミュレーション 値 および 実 験 値 のV out は<br />

低 電 圧 制 御 固 有 角 周 波 数 において 計 算 値 より 変 動 量 が 小 さ<br />

いことを 確 認 した。これは 検 討 では 純 粋 な 負 荷 電 流 ステッ<br />

図 10 負 荷 電 流 ステップ 変 化 による 電 圧 変 動 量<br />

Fig. 10. Output voltage fluctuation by load current step<br />

(V out =0.2p.u.).<br />

図 11 固 有 角 周 波 数 に 対 する 電 圧 変 動 量<br />

Fig. 11. Output voltage fluctuation for nv .<br />

図 12 電 圧 ステップ 応 答<br />

Fig. 12.Voltage step response.<br />

図 13 負 荷 抵 抗 ステップによる 電 圧 応 答 波 形<br />

Fig. 13. Voltage response by load resistance step response.<br />

5/6

プではなく, 負 荷 抵 抗 ステップによる 模 擬 を 行 っているこ<br />

とによる 影 響 である。また,コンデンサの 等 価 直 列 抵 抗<br />

(ESR)の 影 響 , 変 換 器 の 損 失 によるダンピング 効 果 , 使 用<br />

したコンデンサ 容 量 の 誤 差 などがある。<br />

図 15 に 電 圧 変 動 V ou を 0.2p.u.と 設 定 したとき 負 荷 抵 抗 ス<br />

テップによる 電 圧 変 動 をグラフ 化 した 結 果 を 示 す。これよ<br />

り, 算 出 したV out は 計 算 式 に 対 し 低 い 値 となっていること<br />

がわかる。 誤 差 の 原 因 は 先 述 の 影 響 が 現 れているためであ<br />

る。<br />

6. まとめ<br />

本 論 文 では, 昇 圧 チョッパの 電 流 制 御 系 と 出 力 電 圧 制<br />

御 系 の 限 界 応 答 設 計 について 述 べた。 入 力 電 流 制 御 にデ<br />

ッドビート 制 御 器 を 用 いたとき, 目 標 とする 応 答 周 波 数<br />

f d の 3.15 倍 程 度 以 上 にサンプリング 周 波 数 (キャリア 周<br />

波 数 )を 設 定 すればよいことを 明 らかにした。<br />

また, 電 圧 制 御 系 において 負 荷 電 流 ステップ 入 力 時 に<br />

おける 出 力 電 圧 変 動 量 と 電 圧 制 御 固 有 角 周 波 数 ,コンデ<br />

ンサ C の 関 係 性 を 定 式 化 し,これらの 関 係 を 明 らかにし<br />

た。また,シミュレーションにより, 電 圧 制 御 固 有 角 周<br />

波 数 は 1000rad/sec 以 下 である 必 要 があることを 明 らかに<br />

した。さらに 検 証 実 験 を 行 い, 電 圧 変 動 値 を 0.2p.u., 固<br />

有 角 周 波 数 を 100rad/sec としたとき, 電 圧 変 動 誤 差 は 設 計<br />

値 に 対 して 8.53%であり,おおむね 理 論 と 一 致 している。<br />

以 上 より,これらの 設 計 指 針 の 有 効 性 を 確 認 した。<br />

文<br />

(1) K. Kouno, Y. Ishiyama, M. Yamamoto:“Optimum Design of Trans-linked<br />

method single phase interleaved PFC converter”, JIASC IEEJ,H23,1-74<br />

河 野 研 太 , 石 倉 祐 樹 , 山 本 真 義 :「トランスリンク 方 式 単 層 インター<br />

リーブ PFC コンバータの 最 適 設 計 方 法 」 平 成 23 年 産 業 応 用 部 門 大<br />

会 1-74<br />

(2) T. Fushimi, H. Haga, S. Kondo:“Control Method of Electrolytic Capacitor<br />

Less Buck-boost Converter for Single-phase UPS”, JIASC IEEJ,H23,<br />

1-82<br />

伏 見 高 明 , 芳 賀 仁 , 近 藤 正 示 :「 電 解 コンデンサレス 昇 降 圧 チョッパ<br />

を 用 いた 常 時 商 用 単 層 UPS の 小 型 化 への 検 討 」<br />

平 成 23 年 産 業 応 用 部 門 大 会 1-82<br />

(3) Y. Nakamura, M. Nakahama, M. Yamamoto:“Frequency Property Analysis<br />

of Multi-phase Boost Chopper Circuit”, IEEJ annual meeting,H22,<br />

4-009<br />

中 村 祐 太 , 中 浜 真 之 , 山 本 真 義 :「マルチフェーズ 昇 圧 チョッパ 回 路<br />

の 周 波 数 特 性 解 析 」 平 成 22 年 電 気 学 会 全 国 大 会 大 会 4-009<br />

(4) T. Mishima, M. Hattori, D. Tukiyama, Shuuji Miyake, M. Nakaoka:<br />

“Optimum Design of Trans-linked method single phase interleaved PFC<br />

converter”, IEEJ annual meeting,H22,4-014<br />

三 島 智 和 , 服 部 将 之 , 築 山 大 輔 , 三 宅 修 二 , 中 岡 睦 雄 :「トランスリン<br />

ク 方 式 単 層 インターリーブ PFC コンバータの 最 適 設 計 方 法 」 平 成 22<br />

年 電 気 学 会 全 国 大 会 大 会 4-014<br />

(5) K. Mathuura, J. Itoh:“A Loss Analysis of a 3-Level switched capacitor<br />

DC-DC Converter”, SPC-11-098<br />

松 浦 浩 一 , 伊 東 淳 一 :「 低 インダクタによる 高 昇 圧 比 向 け DC-DC コ<br />

ンバータの 基 礎 検 討 」, 半 導 体 電 力 変 換 研 究 会 ,SPC-10-104(2010)<br />

(6) T. Yokoyama, T. Komiyama, E. Shimada:Current Control for Utility<br />

Interactive Inverter Using Multisampling Method Based on FPGA” IEEJ<br />

Trans.1A, Vol.130, No.1, 2010, pp.51-59<br />

献<br />

図 14 負 荷 抵 抗 ステップ 変 化 による 電 圧 変 動 量<br />

Fig. 14. Output voltage fluctuation by load resistance<br />

step (C =1800F).<br />

図 15 負 荷 抵 抗 ステップ 変 化 による 電 圧 変 動 量<br />

Fig. 15. Output voltage fluctuation by load resistance<br />

step (V out =0.2p.u.).<br />

横 山 智 樹 , 小 宮 山 剛 , 島 田 永 悟 「FPGA によるマルチサンプリ<br />

ングを 適 用 した 単 相 系 統 連 系 インバータの 電 流 制 御 」 電 学 論 D,<br />

Vol.130, No.1, 2010, pp.51-59<br />

(7) H. Abe, H. Fujimoto” Perfect Tracking Control of Single Phase<br />

Inverter with Inter Sampling for Arbitary Waveform”JIASC IEEJ, H18<br />

安 部 洋 則 , 藤 本 博 志 , " 任 意 波 形 に 対 するインターサンプリング<br />

を 用 いた 単 相 インバータの 完 全 追 従 制 御 ", 平 成 18 年 産 業 応 用 部<br />

門 大 会<br />

(8) 渋 谷 貴 之 , 野 下 裕 市 , 伊 東 淳 一 : 「 昇 圧 チョッパにおけるデッドビー<br />

ト 制 御 による 電 流 応 答 限 界 に 関 する 考 察 」 電 気 関 係 学 会 北 陸 支 部 連<br />

合 大 会 A-64(2011)<br />

(9) 渋 谷 貴 之 , 野 下 裕 市 , 伊 東 淳 一 : 「 昇 圧 チョッパにおける 電 流 制 御<br />

系 のサンプリング 周 波 数 選 定 法 に 関 する 考 察 」 平 成 23 年 度 電 気 学<br />

会 東 京 支 部 新 潟 支 所 研 究 発 表 会 ,Ⅳ-06(2011)<br />

6/6