Computer Architecture and Organization Chapter 7 â Memory - IIUSA

Computer Architecture and Organization Chapter 7 â Memory - IIUSA

Computer Architecture and Organization Chapter 7 â Memory - IIUSA

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

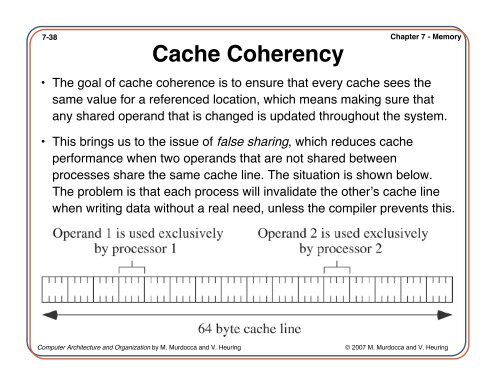

7-38 <strong>Chapter</strong> 7 - <strong>Memory</strong><br />

Cache Coherency<br />

• The goal of cache coherence is to ensure that every cache sees the<br />

same value for a referenced location, which means making sure that<br />

any shared oper<strong>and</strong> that is changed is updated throughout the system.<br />

• This brings us to the issue of false sharing, which reduces cache<br />

performance when two oper<strong>and</strong>s that are not shared between<br />

processes share the same cache line. The situation is shown below.<br />

The problem is that each process will invalidate the other’s cache line<br />

when writing data without a real need, unless the compiler prevents this.<br />

<strong>Computer</strong> <strong>Architecture</strong> <strong>and</strong> <strong>Organization</strong> by M. Murdocca <strong>and</strong> V. Heuring<br />

© 2007 M. Murdocca <strong>and</strong> V. Heuring