ACHIEVING MISSION ASSURANCE - Raytheon

ACHIEVING MISSION ASSURANCE - Raytheon

ACHIEVING MISSION ASSURANCE - Raytheon

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

onTechnology<br />

IBM Cell Processor<br />

Paves Way for New<br />

Multi-threaded Processors<br />

An observation was made in 1965 by<br />

Gordon Moore, co-founder of Intel, stating<br />

that the number of transistors per square<br />

inch on an integrated circuit has doubled<br />

every year since they were invented. Moore<br />

predicted that this trend would continue for<br />

the foreseeable future. He was right ... to a<br />

point. Instead of doubling every year, the<br />

density has doubled every 18 months; this<br />

has become the current definition of<br />

Moore’s Law.<br />

Now the issue that remains is how to<br />

effectively utilize all these transistors.<br />

Increase in Real Performance Lagging<br />

Unfortunately, the increase in real performance<br />

is not commensurate with each new<br />

device generation. Data indicates that only<br />

40 percent improvement in performance<br />

has occurred with each doubling of transistors.<br />

This is primarily due to the push to<br />

improve single thread performance. Adding<br />

architectural complexity to enhance the<br />

instruction level parallelism (ILP) — and ultimately<br />

overall performance — is hindering<br />

the effectiveness of these transistors.<br />

Complexity such as dynamic execution<br />

(rescheduling a serial stream of instructions<br />

in real time so they can execute in parallel),<br />

complex branch prediction logic, out-oforder<br />

execution (to better utilize processing<br />

resources) and large caches are common<br />

techniques used in many state-of-theindustry<br />

components today.<br />

New Breed of Processors<br />

A new breed of processors inspired by the<br />

IBM Cell processor is changing this trend.<br />

The fundamental approach of the Cell<br />

processor’s design sacrifices single threaded<br />

performance optimizations for additional<br />

hardware resources that perform parallel<br />

thread computations. Optimizing for thread<br />

level parallelism (TLP) rather than ILP represents<br />

a significant change in architecture.<br />

A critical examination of Cell processor<br />

implementation — and therefore TLP optimization<br />

— has determined that a much<br />

more efficient use of transistors for certain<br />

applications can be achieved.<br />

The new Cell processor, which is a collaborative<br />

effort among IBM, Sony and Toshiba,<br />

has been designed primarily for the video<br />

game market and will first appear in Sony<br />

PlayStation 3 in spring 2006. It’s expected<br />

to provide an order of magnitude of computing<br />

power far beyond what is currently<br />

achievable with today’s processors. While<br />

optimizing for TLP works wonders for videorendering<br />

applications, it’s also an efficient<br />

architecture for real-time embedded sensor<br />

processing and many of <strong>Raytheon</strong>’s system<br />

applications.<br />

Pursuing System Performance<br />

Improvements<br />

Multiple teams across <strong>Raytheon</strong> conducted<br />

a critical and detailed examination of the<br />

Cell processor during 2005. They determined<br />

that significant system performance<br />

improvements can be realized. For example,<br />

radar modes that were once only dreamed<br />

of by system analyst and waveform designers<br />

can now be implemented in an embedded<br />

real-time airborne application.<br />

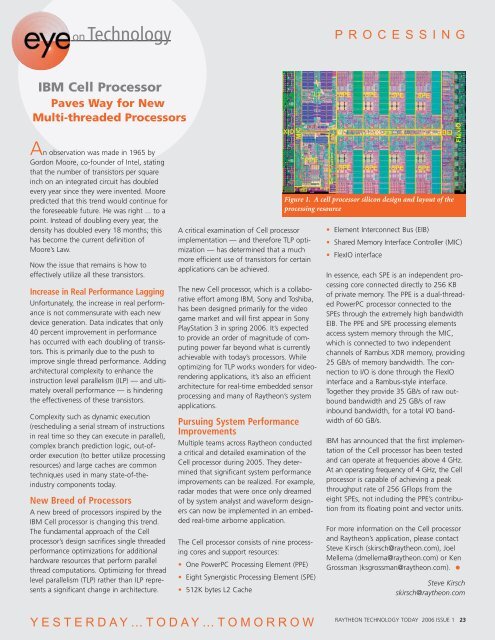

The Cell processor consists of nine processing<br />

cores and support resources:<br />

One PowerPC Processing Element (PPE)<br />

Eight Synergistic Processing Element (SPE)<br />

512K bytes L2 Cache<br />

YESTERDAY…TODAY…TOMORROW<br />

PROCESSING<br />

Figure 1. A cell processor silicon design and layout of the<br />

processing resource<br />

Element Interconnect Bus (EIB)<br />

Shared Memory Interface Controller (MIC)<br />

FlexIO interface<br />

In essence, each SPE is an independent processing<br />

core connected directly to 256 KB<br />

of private memory. The PPE is a dual-threaded<br />

PowerPC processor connected to the<br />

SPEs through the extremely high bandwidth<br />

EIB. The PPE and SPE processing elements<br />

access system memory through the MIC,<br />

which is connected to two independent<br />

channels of Rambus XDR memory, providing<br />

25 GB/s of memory bandwidth. The connection<br />

to I/O is done through the FlexIO<br />

interface and a Rambus-style interface.<br />

Together they provide 35 GB/s of raw outbound<br />

bandwidth and 25 GB/s of raw<br />

inbound bandwidth, for a total I/O bandwidth<br />

of 60 GB/s.<br />

IBM has announced that the first implementation<br />

of the Cell processor has been tested<br />

and can operate at frequencies above 4 GHz.<br />

At an operating frequency of 4 GHz, the Cell<br />

processor is capable of achieving a peak<br />

throughput rate of 256 GFlops from the<br />

eight SPEs, not including the PPE’s contribution<br />

from its floating point and vector units.<br />

For more information on the Cell processor<br />

and <strong>Raytheon</strong>’s application, please contact<br />

Steve Kirsch (skirsch@raytheon.com), Joel<br />

Mellema (dmellema@raytheon.com) or Ken<br />

Grossman )ksgrossman@raytheon.com).<br />

Steve Kirsch<br />

skirsch@raytheon.com<br />

RAYTHEON TECHNOLOGY TODAY 2006 ISSUE 1 23