Xilinx XC95108 In-System Programmable CPLD datasheet, v3.0 (12 ...

Xilinx XC95108 In-System Programmable CPLD datasheet, v3.0 (12 ...

Xilinx XC95108 In-System Programmable CPLD datasheet, v3.0 (12 ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

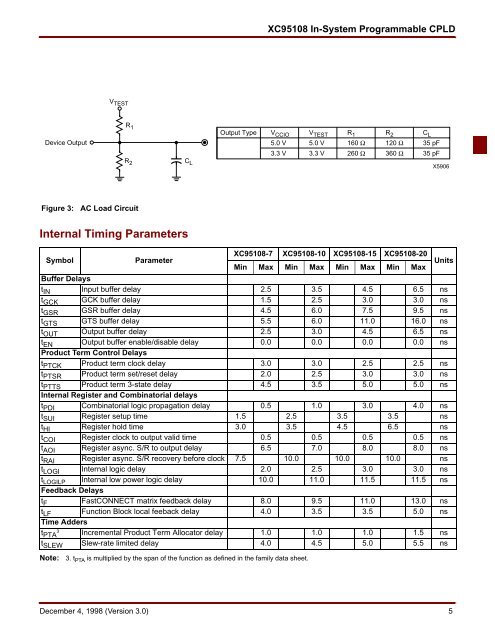

<strong>XC95108</strong> <strong>In</strong>-<strong>System</strong> <strong>Programmable</strong> <strong>CPLD</strong>V TESTDevice OutputR 1Output TypeV CCIO5.0 V3.3 VV TEST5.0 V3.3 VR 1160 Ω260 ΩR 2<strong>12</strong>0 Ω360 ΩC L35 pF35 pFR 2C LX5906Figure 3: AC Load Circuit<strong>In</strong>ternal Timing ParametersSymbolParameterNote: 3. t PTA is multiplied by the span of the function as defined in the family data sheet.<strong>XC95108</strong>-7 <strong>XC95108</strong>-10 <strong>XC95108</strong>-15 <strong>XC95108</strong>-20UnitsMin Max Min Max Min Max Min MaxBuffer Delayst IN <strong>In</strong>put buffer delay 2.5 3.5 4.5 6.5 nst GCK GCK buffer delay 1.5 2.5 3.0 3.0 nst GSR GSR buffer delay 4.5 6.0 7.5 9.5 nst GTS GTS buffer delay 5.5 6.0 11.0 16.0 nst OUT Output buffer delay 2.5 3.0 4.5 6.5 nst EN Output buffer enable/disable delay 0.0 0.0 0.0 0.0 nsProduct Term Control Delayst PTCK Product term clock delay 3.0 3.0 2.5 2.5 nst PTSR Product term set/reset delay 2.0 2.5 3.0 3.0 nst PTTS Product term 3-state delay 4.5 3.5 5.0 5.0 ns<strong>In</strong>ternal Register and Combinatorial delayst PDI Combinatorial logic propagation delay 0.5 1.0 3.0 4.0 nst SUI Register setup time 1.5 2.5 3.5 3.5 nst HI Register hold time 3.0 3.5 4.5 6.5 nst COI Register clock to output valid time 0.5 0.5 0.5 0.5 nst AOI Register async. S/R to output delay 6.5 7.0 8.0 8.0 nst RAI Register async. S/R recovery before clock 7.5 10.0 10.0 10.0 nst LOGI <strong>In</strong>ternal logic delay 2.0 2.5 3.0 3.0 nst LOGILP <strong>In</strong>ternal low power logic delay 10.0 11.0 11.5 11.5 nsFeedback Delayst F FastCONNECT matrix feedback delay 8.0 9.5 11.0 13.0 nst LF Function Block local feeback delay 4.0 3.5 3.5 5.0 nsTime Adders3t PTA <strong>In</strong>cremental Product Term Allocator delay 1.0 1.0 1.0 1.5 nst SLEW Slew-rate limited delay 4.0 4.5 5.0 5.5 nsDecember 4, 1998 (Version 3.0) 5