SRAM System Design Guidelines

SRAM System Design Guidelines

SRAM System Design Guidelines

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

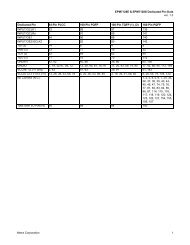

<strong>SRAM</strong> <strong>System</strong> <strong>Design</strong> <strong>Guidelines</strong>When power planes are correctly bypassed, they are at thesame AC potential as ground planes. Therefore, they can beused as a reference for controlled impedance traces. Usingboth power and ground planes, however, is unwise becausethe transition between the two has a high potential of causingnoticeable impedance discontinuities in trace impedance,which is a source of unwanted reflections. (This applicationnote will explain reflections in more detail in the next section.)Vias in TracesWhen routing a trace, the signal should remain on the samesignal plan. Using a via to route to another plane diminishessignal quality. Vias should therefore be avoided as much aspossible. If vias have to be used in a high-speed design, thefollowing guidelines should be considered.1. Make vias as large as possible (more area equals lessinductance and resistance).2. Plate external layers with the maximum thickness ofcopper during fabrication.3. Plating of filling the via holes solid.+ _Distance(Y-X)XYStep Voltage: VAt point X, the step is still ofsize V, but is now delayedAt point Y, the step isdelayed even furtherReflections and TerminationsAnother problem that arises in digital signal systems involvesreflections due to poorly terminated transmission lines. Thissection will discuss a few important points to remember whendesigning with long wiring networks. For a full discussion ontransmission lines, please refer to the Terminations applicationnote available on the Cypress web site.What is a Reflection?A reflection is an unwanted pulse on a transmission line thatis a result of an unmatched source or load impedance. Thetransmission line has an intrinsic value called its characteristicimpedance. A reflection back toward the driver sourcecan occur if the line’s load and characteristic impedances arenot matched, and a second reflection back toward the loadcan occur if the source and characteristic impedances arealso not matched.Why do Reflections Occur?Reflections occur because of impedance mismatches thatcause a disproportion of energy transfer. If the line is ideal,and the source impedance Z S equals the load impedance Z L ,then half the energy in the propagating signal will be lost inthe source impedance, and the other half in the loadimpedance (since the ideal line is lossless). However, if theload resistor at the end of the line is larger than the line’scharacteristic impedance, there will be extra energy availablethat is “reflected” back toward the source. That is, there isanother signal that propagates down the line that “bounces”off the load if there is an impedance mismatch.Characteristic ImpedanceThe most important variable of any line is its characteristic, orinput, impedance. This is the impedance seen looking into thetwo left-hand terminals of the line.t 0 t 1Figure 10. Voltage Step Input to an Ideal LineFigure 10 below illustrates how a digital pulse propagatesdown an ideal line. The pulse is set onto the beginning of theline by the source at time t = 0. This pulse is then transferreddown the line without being distorted or attenuated while it isdelayed in time according to the line’s propagation delay. Atpoint X, the voltage on the line is low, until time t 0 at whichtime the signal passes point X on the line, and we can seethat the pulse drives the voltage up to the high level. A similarsituation exists for point Y, except that the signal stays lowlonger while it waits for the pulse to propagate down the line.We can find the characteristic impedance of this line byfinding the amount of current it takes to impress the stepvoltage on a given length of the line, in this case betweenarbitrary points Y and X.The capacitance of the length of line between points X and Yis given as:CC xy = ⎛----⎞×( Y–X)⎝in·⎠. Eq. 9The total additional charge necessary to charge the capacitancebetween these points is equal to:CCharge= C xy= ⎛----⎞ ⎝in·⎠ ( Y–X)V. Eq. 10The time interval (in seconds) in which during which Cxy mustbe charged is equal to the separation of the two points timesthe propagation delay in seconds per unit length:T = ( Y–X)⎛----L⎞⎛----C⎞⎝in·⎠⎝in·⎠. Eq. 117