- Page 1 and 2: Features• High-performance, Low-p

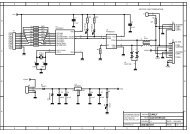

- Page 3 and 4: -ATmega128(L)Block DiagramFigure 2.

- Page 5 and 6: ATmega128(L)The ATmega128 is 100% p

- Page 7 and 8: ATmega128(L)The port G pins are tri

- Page 9 and 10: ATmega128(L)an arithmetic operation

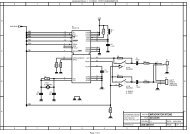

- Page 11 and 12: ATmega128(L)Figure 4. AVR CPU Gener

- Page 13 and 14: ATmega128(L)Instruction ExecutionTi

- Page 15 and 16: ATmega128(L)When using the SEI inst

- Page 17 and 18: ATmega128(L)SRAM Data MemoryThe ATm

- Page 19: ATmega128(L)Data Memory Access Time

- Page 23 and 24: ATmega128(L)The next code examples

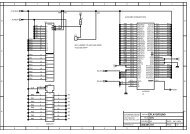

- Page 25 and 26: ATmega128(L)Figure 11. External Mem

- Page 27 and 28: ATmega128(L)Pull-up and Bus-keeperT

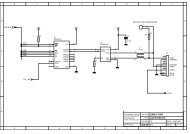

- Page 29 and 30: ATmega128(L)Figure 16. External Dat

- Page 31 and 32: ATmega128(L)• Bit 0 - Res: Reserv

- Page 33 and 34: ATmega128(L)Using all 64KB Location

- Page 35 and 36: ATmega128(L)Asynchronous Timer Cloc

- Page 37 and 38: ATmega128(L)Table 9. Start-up Times

- Page 39 and 40: ATmega128(L)Calibrated Internal RCO

- Page 41 and 42: ATmega128(L)Timer/Counter Oscillato

- Page 43 and 44: ATmega128(L)Idle ModeADC Noise Redu

- Page 45 and 46: ATmega128(L)Minimizing PowerConsump

- Page 47 and 48: ATmega128(L)System Control andReset

- Page 49 and 50: ATmega128(L)2. V BOT may be below n

- Page 51 and 52: ATmega128(L)Watchdog ResetWhen the

- Page 53 and 54: ATmega128(L)Table 21. WDT Configura

- Page 55 and 56: ATmega128(L)The following code exam

- Page 57 and 58: ATmega128(L)Table 23. Reset and Int

- Page 59 and 60: ATmega128(L)When the BOOTRST fuse i

- Page 61 and 62: ATmega128(L)• Bit 0 - IVCE: Inter

- Page 63 and 64: ATmega128(L)Ports as General Digita

- Page 65 and 66: ATmega128(L)Consider the clock peri

- Page 67 and 68: ATmega128(L)Unconnected pinsAlterna

- Page 69 and 70: ATmega128(L)Special Function IO Reg

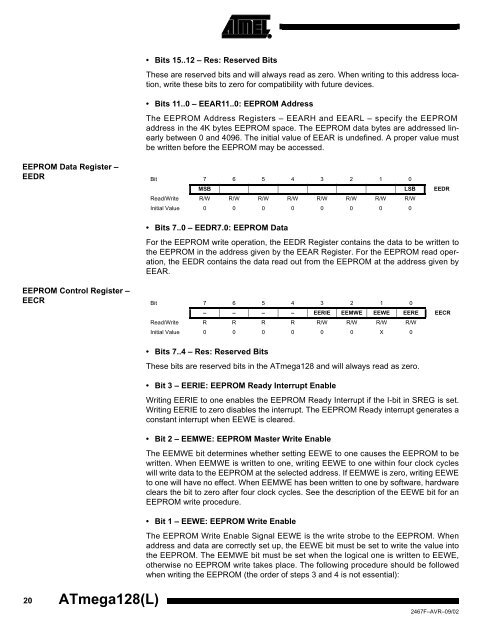

- Page 71 and 72:

ATmega128(L)• OC1B, Bit 6OC1B, Ou

- Page 73 and 74:

ATmega128(L)Alternate Functions of

- Page 75 and 76:

ATmega128(L)• IC1 - Port D, Bit 4

- Page 77 and 78:

ATmega128(L)Alternate Functions of

- Page 79 and 80:

ATmega128(L)Table 41. Overriding Si

- Page 81 and 82:

ATmega128(L)Alternate Functions of

- Page 83 and 84:

ATmega128(L)Register Description fo

- Page 85 and 86:

ATmega128(L)Port F Data Direction R

- Page 87 and 88:

ATmega128(L)Table 48. Interrupt Sen

- Page 89 and 90:

ATmega128(L)8-bit Timer/Counter0wit

- Page 91 and 92:

ATmega128(L)Signal description (int

- Page 93 and 94:

ATmega128(L)The setup of the OC0 sh

- Page 95 and 96:

ATmega128(L)An interrupt can be gen

- Page 97 and 98:

ATmega128(L)Phase Correct PWM ModeT

- Page 99 and 100:

ATmega128(L)Figure 42. Timer/Counte

- Page 101 and 102:

ATmega128(L)Table 52. Waveform Gene

- Page 103 and 104:

ATmega128(L)Asynchronous Operationo

- Page 105 and 106:

ATmega128(L)from Power-save mode, a

- Page 107 and 108:

ATmega128(L)one of them advancing d

- Page 109 and 110:

ATmega128(L)Figure 46. 16-bit Timer

- Page 111 and 112:

ATmega128(L)• WGMn3 is added to T

- Page 113 and 114:

ATmega128(L)The following code exam

- Page 115 and 116:

ATmega128(L)TCCRnB). There are clos

- Page 117 and 118:

ATmega128(L)(ICFn) must be cleared

- Page 119 and 120:

ATmega128(L)Compare Match OutputUni

- Page 121 and 122:

ATmega128(L)Figure 51. CTC Mode, Ti

- Page 123 and 124:

ATmega128(L)The result will then be

- Page 125 and 126:

ATmega128(L)at TOP, the PWM period

- Page 127 and 128:

ATmega128(L)In phase and frequency

- Page 129 and 130:

ATmega128(L)Figure 58. Timer/Counte

- Page 131 and 132:

ATmega128(L)Table 60. Compare Outpu

- Page 133 and 134:

ATmega128(L)• Bit 6 - ICESn: Inpu

- Page 135 and 136:

ATmega128(L)Output Compare Register

- Page 137 and 138:

ATmega128(L)• Bit 2 - TOIE1: Time

- Page 139 and 140:

ATmega128(L)Extended Timer/CounterI

- Page 141 and 142:

ATmega128(L)Timer/Counter3,Timer/Co

- Page 143 and 144:

ATmega128(L)8-bit Timer/Counter2wit

- Page 145 and 146:

ATmega128(L)clear Clear TCNT2 (set

- Page 147 and 148:

ATmega128(L)put Compare (FOC2) stro

- Page 149 and 150:

ATmega128(L)An interrupt can be gen

- Page 151 and 152:

ATmega128(L)cleared on the compare

- Page 153 and 154:

ATmega128(L)Figure 70. Timer/Counte

- Page 155 and 156:

ATmega128(L)When OC2 is connected t

- Page 157 and 158:

ATmega128(L)• Bit 6 - TOIE2: Time

- Page 159 and 160:

ATmega128(L)When the modulator is e

- Page 161 and 162:

ATmega128(L)When configured as a Ma

- Page 163 and 164:

ATmega128(L)The following code exam

- Page 165 and 166:

ATmega128(L)• Bit 4 - MSTR: Maste

- Page 167 and 168:

ATmega128(L)Data ModesThere are fou

- Page 169 and 170:

ATmega128(L)Figure 79. USART Block

- Page 171 and 172:

ATmega128(L)Signal description:txcl

- Page 173 and 174:

ATmega128(L)Frame FormatsA serial f

- Page 175 and 176:

ATmega128(L)baud and control regist

- Page 177 and 178:

ATmega128(L)interrupt-driven data t

- Page 179 and 180:

ATmega128(L)Receiving Frames with 9

- Page 181 and 182:

ATmega128(L)stored in the receive b

- Page 183 and 184:

ATmega128(L)Figure 85. Stop Bit Sam

- Page 185 and 186:

ATmega128(L)data frames. When the f

- Page 187 and 188:

ATmega128(L)Register, and a new sta

- Page 189 and 190:

ATmega128(L)Table 78. UPMn Bits Set

- Page 191 and 192:

ATmega128(L)Examples of Baud RateSe

- Page 193 and 194:

ATmega128(L)Table 84. Examples of U

- Page 195 and 196:

ATmega128(L)Two-wire SerialInterfac

- Page 197 and 198:

ATmega128(L)Address Packet FormatAl

- Page 199 and 200:

ATmega128(L)• Different masters m

- Page 201 and 202:

ATmega128(L)Overview of the TWIModu

- Page 203 and 204:

ATmega128(L)TWI Register Descriptio

- Page 205 and 206:

ATmega128(L)• Bits 1..0 - TWPS: T

- Page 207 and 208:

ATmega128(L)TWINT bit in TWCR is se

- Page 209 and 210:

ATmega128(L)Assembly Code Example C

- Page 211 and 212:

ATmega128(L)Figure 96. Data Transfe

- Page 213 and 214:

ATmega128(L)Figure 97. Formats and

- Page 215 and 216:

ATmega128(L)START enables the maste

- Page 217 and 218:

ATmega128(L)The upper seven bits ar

- Page 219 and 220:

ATmega128(L)Figure 101. Formats and

- Page 221 and 222:

ATmega128(L)Table 91. Status Codes

- Page 223 and 224:

ATmega128(L)Multi-master Systemsand

- Page 225 and 226:

ATmega128(L)Analog ComparatorThe An

- Page 227 and 228:

ATmega128(L)When changing the ACIS1

- Page 229 and 230:

ATmega128(L)Figure 108. Analog to D

- Page 231 and 232:

ATmega128(L)Prescaling andConversio

- Page 233 and 234:

ATmega128(L)Table 95. ADC Conversio

- Page 235 and 236:

ATmega128(L)completes. The CPU will

- Page 237 and 238:

ATmega128(L)Figure 115. Offset Erro

- Page 239 and 240:

ATmega128(L)ADC Conversion ResultAf

- Page 241 and 242:

ATmega128(L)ADCL will thus read 0x0

- Page 243 and 244:

ATmega128(L)same time as the ADC is

- Page 245 and 246:

ATmega128(L)JTAG Interface andOn-ch

- Page 247 and 248:

ATmega128(L)Figure 121. TAP Control

- Page 249 and 250:

ATmega128(L)• 2 single Program Me

- Page 251 and 252:

ATmega128(L)IEEE 1149.1 (JTAG)Bound

- Page 253 and 254:

ATmega128(L)Figure 123. Reset Regis

- Page 255 and 256:

ATmega128(L)Boundary-scan ChainScan

- Page 257 and 258:

ATmega128(L)Figure 126. Additional

- Page 259 and 260:

ATmega128(L)Figure 129. Analog comp

- Page 261 and 262:

ATmega128(L)Table 105. Boundary-sca

- Page 263 and 264:

ATmega128(L)Table 105. Boundary-sca

- Page 265 and 266:

ATmega128(L)ATmega128 BoundaryscanO

- Page 267 and 268:

ATmega128(L)Table 107. ATmega128 Bo

- Page 269 and 270:

ATmega128(L)Table 107. ATmega128 Bo

- Page 271 and 272:

ATmega128(L)Table 107. ATmega128 Bo

- Page 273 and 274:

ATmega128(L)Note that the user soft

- Page 275 and 276:

ATmega128(L)Table 109. Boot Lock Bi

- Page 277 and 278:

ATmega128(L)• Bit 1 - PGERS: Page

- Page 279 and 280:

ATmega128(L)Performing Page Erase b

- Page 281 and 282:

ATmega128(L)the SPMCSR, the value o

- Page 283 and 284:

ATmega128(L); disable interrupts if

- Page 285 and 286:

ATmega128(L)MemoryProgrammingProgra

- Page 287 and 288:

ATmega128(L)Table 119. Fuse High By

- Page 289 and 290:

ATmega128(L)Parallel ProgrammingPar

- Page 291 and 292:

ATmega128(L)Table 126. No. of Words

- Page 293 and 294:

ATmega128(L)3. Set DATA = Address h

- Page 295 and 296:

ATmega128(L)Figure 138. Programming

- Page 297 and 298:

ATmega128(L)4. Set OE to “0”, B

- Page 299 and 300:

ATmega128(L)Figure 143. Parallel Pr

- Page 301 and 302:

ATmega128(L)Figure 144. SPI Serial

- Page 303 and 304:

ATmega128(L)Table 129. Minimum Wait

- Page 305 and 306:

ATmega128(L)SPI Serial ProgrammingC

- Page 307 and 308:

ATmega128(L)PROG_COMMANDS ($5)PROG_

- Page 309 and 310:

ATmega128(L)Programming CommandRegi

- Page 311 and 312:

ATmega128(L)Table 131. JTAG Program

- Page 313 and 314:

ATmega128(L)Figure 149. State Machi

- Page 315 and 316:

ATmega128(L)Entering Programming Mo

- Page 317 and 318:

ATmega128(L)7. Write Fuse high byte

- Page 319 and 320:

ATmega128(L)T A = -40°C to 85°C,

- Page 321 and 322:

ATmega128(L)Two-wire Serial Interfa

- Page 323 and 324:

ATmega128(L)Figure 154. SPI Interfa

- Page 325 and 326:

ATmega128(L)External Data Memory Ti

- Page 327 and 328:

ATmega128(L)Table 141. External Dat

- Page 329 and 330:

ATmega128(L)Figure 158. External Me

- Page 331 and 332:

ATmega128(L)Figure 160. Active Supp

- Page 333 and 334:

ATmega128(L)Figure 164. Active Supp

- Page 335 and 336:

ATmega128(L)Figure 168. Idle Supply

- Page 337 and 338:

ATmega128(L)Figure 172. Power-down

- Page 339 and 340:

ATmega128(L)Figure 176. Standby Sup

- Page 341 and 342:

ATmega128(L)Figure 180. I/O Pin Pul

- Page 343 and 344:

ATmega128(L)Figure 184. I/O Pin Sou

- Page 345 and 346:

ATmega128(L)Figure 188. BOD Thresho

- Page 347 and 348:

ATmega128(L)Figure 192. Analog Comp

- Page 349 and 350:

ATmega128(L)Figure 195. RC Oscillat

- Page 351 and 352:

ATmega128(L)Figure 199. RC Oscillat

- Page 353 and 354:

ATmega128(L)Register SummaryAddress

- Page 355 and 356:

ATmega128(L)Register Summary (Conti

- Page 357 and 358:

ATmega128(L)Instruction Set Summary

- Page 359 and 360:

ATmega128(L)Ordering InformationSpe

- Page 361 and 362:

RATmega128(L)64M1DMarked PIN 1 iden

- Page 363 and 364:

ATmega128(L)10. Updated Programming

- Page 365 and 366:

ATmega128(L)ErratasATmega128 Rev. F

- Page 367 and 368:

ATmega128(L)Table of Contents Featu

- Page 369 and 370:

ATmega128(L)Overview...............

- Page 371 and 372:

ATmega128(L)Programming Via the JTA