An Automatic Approach to Generate Haste Code from Simulink ...

An Automatic Approach to Generate Haste Code from Simulink ...

An Automatic Approach to Generate Haste Code from Simulink ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

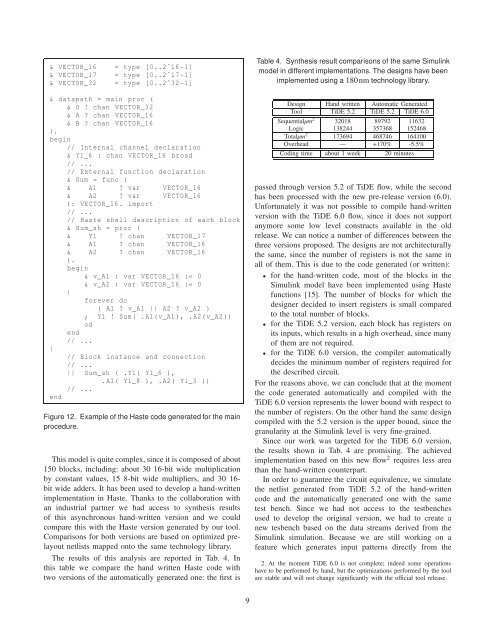

& VECTOR_16& VECTOR_17& VECTOR_32= type [0..2ˆ16-1]= type [0..2ˆ17-1]= type [0..2ˆ32-1]Table 4. Synthesis result comparisons of the same <strong>Simulink</strong>model in different implementations. The designs have beenimplemented using a 180nm technology library.& datapath = main proc (& O ! chan VECTOR_32& A ? chan VECTOR_16& B ? chan VECTOR_16).begin// Internal channel declaration& Y1_6 : chan VECTOR_16 broad// ...// External function declaration& Sum = func (& A1 ? var VECTOR_16& A2 ? var VECTOR_16): VECTOR_16. import// ...// <strong>Haste</strong> shell description of each block& Sum_sh = proc (& Y1 ! chan VECTOR_17& A1 ? chan VECTOR_16& A2 ? chan VECTOR_16).begin& v_A1 : var VECTOR_16 := 0& v_A2 : var VECTOR_16 := 0|forever do( A1 ? v_A1 || A2 ? v_A2 ); Y1 ! Sum( .A1(v_A1), .A2(v_A2))odend// ...|// Block instance and connection// ...|| Sum_sh ( .Y1( Y1_6 ),.A1( Y1_8 ), .A2( Y1_3 ))// ...endFigure 12. Example of the <strong>Haste</strong> code generated for the mainprocedure.This model is quite complex, since it is composed of about150 blocks, including: about 30 16-bit wide multiplicationby constant values, 15 8-bit wide multipliers, and 30 16-bit wide adders. It has been used <strong>to</strong> develop a hand-writtenimplementation in <strong>Haste</strong>. Thanks <strong>to</strong> the collaboration withan industrial partner we had access <strong>to</strong> synthesis resultsof this asynchronous hand-written version and we couldcompare this with the <strong>Haste</strong> version generated by our <strong>to</strong>ol.Comparisons for both versions are based on optimized prelayoutnetlists mapped on<strong>to</strong> the same technology library.The results of this analysis are reported in Tab. 4. Inthis table we compare the hand written <strong>Haste</strong> code withtwo versions of the au<strong>to</strong>matically generated one: the first isDesign Hand written <strong>Au<strong>to</strong>matic</strong> <strong>Generate</strong>dTool TiDE 5.2 TiDE 5.2 TiDE 6.0Sequentialµm 2 32018 89792 11632Logic 138244 357368 152468Totalµm 2 173694 468746 164100Overhead — +170% -5.5%Coding time about 1 week 20 minutespassed through version 5.2 of TiDE flow, while the secondhas been processed with the new pre-release version (6.0).Unfortunately it was not possible <strong>to</strong> compile hand-writtenversion with the TiDE 6.0 flow, since it does not supportanymore some low level constructs available in the oldrelease. We can notice a number of differences between thethree versions proposed. The designs are not architecturallythe same, since the number of registers is not the same inall of them. This is due <strong>to</strong> the code generated (or written):• for the hand-written code, most of the blocks in the<strong>Simulink</strong> model have been implemented using <strong>Haste</strong>functions [15]. The number of blocks for which thedesigner decided <strong>to</strong> insert registers is small compared<strong>to</strong> the <strong>to</strong>tal number of blocks.• for the TiDE 5.2 version, each block has registers onits inputs, which results in a high overhead, since manyof them are not required.• for the TiDE 6.0 version, the compiler au<strong>to</strong>maticallydecides the minimum number of registers required forthe described circuit.For the reasons above, we can conclude that at the momentthe code generated au<strong>to</strong>matically and compiled with theTiDE 6.0 version represents the lower bound with respect <strong>to</strong>the number of registers. On the other hand the same designcompiled with the 5.2 version is the upper bound, since thegranularity at the <strong>Simulink</strong> level is very fine-grained.Since our work was targeted for the TiDE 6.0 version,the results shown in Tab. 4 are promising. The achievedimplementation based on this new flow 2 requires less areathan the hand-written counterpart.In order <strong>to</strong> guarantee the circuit equivalence, we simulatethe netlist generated <strong>from</strong> TiDE 5.2 of the hand-writtencode and the au<strong>to</strong>matically generated one with the sametest bench. Since we had not access <strong>to</strong> the testbenchesused <strong>to</strong> develop the original version, we had <strong>to</strong> create anew tesbench based on the data streams derived <strong>from</strong> the<strong>Simulink</strong> simulation. Because we are still working on afeature which generates input patterns directly <strong>from</strong> the2. At the moment TiDE 6.0 is not complete; indeed some operationshave <strong>to</strong> be performed by hand, but the optimizations performed by the <strong>to</strong>olare stable and will not change significantly with the official <strong>to</strong>ol release.9