EECS 370 – Introduction to Computer Organization – Exam 1 w

EECS 370 – Introduction to Computer Organization – Exam 1 w

EECS 370 – Introduction to Computer Organization – Exam 1 w

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

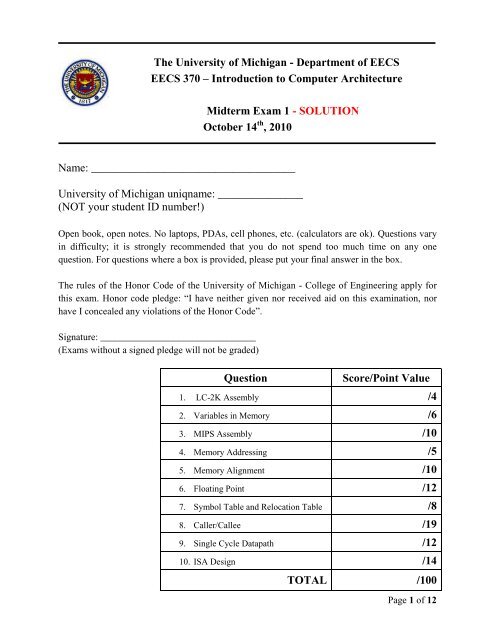

The University of Michigan - Department of <strong>EECS</strong><strong>EECS</strong> <strong>370</strong> <strong>–</strong> <strong>Introduction</strong> <strong>to</strong> <strong>Computer</strong> ArchitectureMidterm <strong>Exam</strong> 1 - SOLUTIONOc<strong>to</strong>ber 14 th , 2010Name: ____________________________________University of Michigan uniqname: _______________(NOT your student ID number!)Open book, open notes. No lap<strong>to</strong>ps, PDAs, cell phones, etc. (calcula<strong>to</strong>rs are ok). Questions varyin difficulty; it is strongly recommended that you do not spend <strong>to</strong>o much time on any onequestion. For questions where a box is provided, please put your final answer in the box.The rules of the Honor Code of the University of Michigan - College of Engineering apply forthis exam. Honor code pledge: “I have neither given nor received aid on this examination, norhave I concealed any violations of the Honor Code”.Signature: ________________________________(<strong>Exam</strong>s without a signed pledge will not be graded)QuestionScore/Point Value1. LC-2K Assembly /42. Variables in Memory /63. MIPS Assembly /104. Memory Addressing /55. Memory Alignment /106. Floating Point /127. Symbol Table and Relocation Table /88. Caller/Callee /199. Single Cycle Datapath /1210. ISA Design /14TOTAL /100Page 1 of 12

1. LC-2K Assembly [4 pts]You are given the following segment of LC-2K assembly code:.fill 21626880 //=0x014A 0000haltCurious <strong>to</strong> determine what this program does, you run it on your recently completed Project1simula<strong>to</strong>r. How many instructions does the simula<strong>to</strong>r execute in <strong>to</strong>tal? (Note: all registers areinitialized <strong>to</strong> zero)A. 0B. 1C. 2 (partial credit of 2 pts is given if you choose this answer)D. Infinite (the instruction translates <strong>to</strong> jalr 1 2)2. Variables in Memory [6 pts]You find the program below by the printer in the CSE lab. Somebody deleted all the variablenames! Fortunately, we still have the information below from the last compilation. Reconstructthe original program by filling in the blanks based on the information provided.Variable information:• x is 4 bytes and resides on the stack.• y is 8 bytes and resides on the stack.• *r is 10 bytes and resides on the heap.• *x is 8 bytes and resides on the heap.• z is 2 bytes and resides in the static section.• p is 20 bytes and resides in the static section.• r is 4 bytes and resides in the static section.• w is 4 bytes and resides in the static section.char *_r_;char _p_ [20];int _w_;int mynamelessfunction(double _y_){static short _z_;int *_x_;. . .. . ._r__ = (char *)malloc(sizeof(char) * 10);. . ._x__ = (int *)malloc(sizeof(int) * 2);}. . .Page 2 of 12

3. MIPS Assembly [10 pts]Given the following C code snippet and its corresponding MIPS assembly code:...z = 0;...clear $s3while (x != 0) { loop beq $s1 $0 breakx = x - y;sub $s1 $s1 $s2}j loop...break ...Answer the questions below. Beware, you are not allowed <strong>to</strong> use any other register except forthose mentioned in the code above (i.e., $s1, $s2, $s3, $0).a) [4 points] clear is a pseudo-instruction in MIPS. Suggest two possible single instructionimplementations of clear using real MIPS instructions (no pseudo-instructions allowed)Possible answers:• and $s3 $s3 $0• add $s3 $0 $0• sub $s3 $s3 $s3• mult $s3 $s3 $0• xor $s3 $s3 $s3• lui $s3 0b) [6 points] You noticed that the C code is compiled inefficiently <strong>–</strong> indeed, this assembly codeexecutes 2 branches/jumps for each loop iteration.Rewrite the assembly code for this C code snippet so that the ‘while’ loop only executes atmost one branch or jump instruction for each loop iteration. (Note: your answer shouldconsist of at most four MIPS instructions)# Your MIPS assembly code hereclear $s31 add $s1 $s1 $s2 beq $s1 $0 break2 loop: sub $s1 $s1 $s2 sub $s1 $s1 $s23 bne $s1 $0 loop bne $s1 $0 loop4break: ...Page 3 of 12

4. Memory Addressing [5 pts]Consider the following MIPS assembly program:0: lui $2, 131: addi $1, $1, -22: sh $1, 1000($0)3: lh $1, 1002($0)4: sw $2, 1000($0)Recall that register $0 always contains the value zero and that MIPS is big-endian. Fill in thefollowing tables in hexadecimal, based on the instruction sequence above. When a register ormemory location does not change, write a dash (--) in the corresponding space of the table.The initial value for register $1 is 0xABCDEF01 and for register $2 is 0x00001000.Register After inst 0 After inst 1 After inst 2 After inst 3 After inst 4$1 -- 0xABCDEEFF -- 0xFFFFBEEF --$2 0x000D0000 -- -- -- --MemoryAddressInitialValueAfter inst 0 After inst 1 After inst 2 After inst 3 After inst 41000 0xDE -- -- 0xEE -- 0x001001 0xAD -- -- 0xFF -- 0x0D1002 0xBE -- -- -- -- 0x001003 0xEF -- -- -- -- 0x00Page 4 of 12

5. Memory Alignment [10 pts]You are given the set of C declarations shown below. Assume that the first available memorylocation is at 100 decimal, that the machine is a 32-bit architecture and that you are using acompiler that does not do any optimization and does not rearrange variable declarations.double a;104-111 (8 bytes)char b;112-112 (1 byte)struct { -padding- 113-119short c;120-121 (2 bytes)struct { -padding- 122-127struct {double d; 128-135 (8 bytes)char **e; 136-139 (4 bytes)} f; -padding- 140-143char g;144-144 (1 byte)} h; -padding- 145-151struct {int i[10];152-191 (40 bytes)short *j;192-195 (4 bytes)} k;} l; -padding- 196-199int m200-203 (4 bytes)int n;204-207 (8 bytes)List the memory locations at which variables e, i and k are placed. Start and end addressesshould be inclusive, that is, if a variable used addresses 10, 11 and 12, the start address would be10 and the end address 12.Variable Start Address End Addresse 136 139i 152 191k 152 195l 120 199n 204 207Page 5 of 12

6. Floating Point [12 pts]You are working for a company developing a high quality graphics processor. This processorwill distinguish itself from competi<strong>to</strong>rs by supporting accurate graphics over an extremely widecontrast range. This is done by using floating point numbers, rather than integers, <strong>to</strong> representthered/green/blue pixel intensity values. To allow a complete (R, G, B) triplet <strong>to</strong> fit in<strong>to</strong> a 64 bitword, 21 bits are used for each value. As 21 bits are not sufficient for standard IEEE singleprecision floating point, an unusual floating point representation is designed with smaller fields.Everything works exactly as in the standard IEEE floating point except:• The exponent uses only 7 bits, with bias 63• The mantissa (significand) uses only 13 bitsa) [6 points] How would a value of -0.265625 decimal be represented in this format? Show all21 bits in the boxes provided and clearly label which bits make up each of the sign,exponent, and mantissa. (Hint: 0.265625 is exactly equal <strong>to</strong> the fraction 17/64). Show yourwork <strong>to</strong> receive credit for your answer.Negative, so sign bit is one, 17/64 = (17/16) * 2 -2Exponent is -2, bias 63 makes exponent field 61 decimal, 0111101 binary17 decimal is 10001 binary, suppress leading one so mantissa field gets 0001Answer in binary:1 0 1 1 1 1 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0S E E E E E E E M M M M M M M M M M M M Mb) [6 points] The number from part (a) is added <strong>to</strong> the floating point value represented by thebits shown below. Show the final result of the addition in this floating point format in theboxes provided. Show your work <strong>to</strong> receive credit for your answer.001111001100000000000Working in binary, we have:1.11 * 2 -3 [shown above] -1.0001 * 2 -2 [from part a]Exponents differ by 1, so shift smaller operand right 1 bit: 1.11 * 2 -3 becomes 0.111 * 2 -2Add 0.111 * 2 -2 <strong>to</strong> -1.0001 * 2 -2 , sum is -0.0011 * 2 -2Too small, must shift 3 bits <strong>to</strong> renormalize, normalized sum is -1.1 * 2 -5Answer in binary:1 0 1 1 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0S E E E E E E E M M M M M M M M M M M M MPage 6 of 12

7. Symbol Table and Relocation Table [8 pts]Given the following program file, which symbols must be placed in<strong>to</strong> the symbol table of itsobject file in order for the linker <strong>to</strong> successfully bind all the symbol references? Which linesshould be placed in the relocation table? List the items for each table in the boxes provided.Myfile.c:1: int avg;2: extern bool flag;3:4: int <strong>EECS</strong><strong>370</strong>(int size)5: {6: int i ;7: int sum = 0;8: flag = 0;9: for (i=0; i < size; i++) {10: sum += grade(i);11: }12: i = average(sum,size);13: avg = i;14: return sum;15: }avgflag<strong>EECS</strong><strong>370</strong>gradeaverageSymbol tableline #8line #10line #12line #13Relocation tablePage 7 of 12

8. Caller/Callee [19 pts]You are given the following two C functions:int foo(int a) {int w=2, x=3, y=4, z=5, v;w = a + x;w += bar(w, x);y = w + z;for (v = 0; v < 5; v++) {z += bar(w, y);}if (y > 20) return y;return w;}int bar(int a, int b) {int p=a, q=b, r, s=1;s += abs(-4);printf(“Values: %d,%d”, p, q);for (r = 0; r < 10; r++) {q = q + p;printf(“New q: %d”, q);}return q;}a) [4 points] Assume that in the function foo variables w, x, and y are all mapped <strong>to</strong> calleesavedregisters. How many s<strong>to</strong>re/load instructions will the compiler insert in the assemblycode of foo for saving and res<strong>to</strong>ring these three registers? [Note: we want <strong>to</strong> know howmany lw/sw instructions the compiler inserts, not how many would be executed] Indicate onthe code of foo where these instructions are inserted and then report the <strong>to</strong>tal below <strong>to</strong>receive any credit for your answer.1 sw instruction for each of w,x,y before “w=a+x”.1 lw instruction for each of w,x,y before “return y”1 lw instruction for each of w,x,y before “return w”sw instructions: _____3______lw instructions: ____6_______b) [11 points] To answer this question, fill the tables in the next page. You must show yourwork on the copy of the code at the bot<strong>to</strong>m of the next page <strong>to</strong> receive any credit.Assume that the function foo is called only once. How many s<strong>to</strong>re/load operations areexecuted for each variable in foo and bar? Do the analysis assuming for each variableboth a caller-saved and a callee-saved mapping, and consider the single call <strong>to</strong> foo and the<strong>to</strong>tal of all the resulting call(s) <strong>to</strong> bar. Assume that parameters a and b are s<strong>to</strong>red inspecial input parameter registers.Page 8 of 12

foo()CallersavedCalleesavedbar()CallersavedCalleesaved# sw # lw # sw # lw # sw # lw # sw # lwv 5 5 1 1 p 72 72 6 6w 6 6 1 1 q 72 72 6 6x 0 0 1 1 r 60 60 6 6y 5 5 1 1 s 6 6 6 6z 6 6 1 1c) [4 points] If you have 3 caller-saved and 2 callee-saved registers available, what is the bestmapping of registers <strong>to</strong> variables <strong>to</strong> minimize the <strong>to</strong>tal number of load/s<strong>to</strong>re operations?(circle your selection below)foo() v caller callee bar() p caller calleew caller callee q caller calleex caller callee r caller calleey caller callee s caller calleez caller calleeCopy of code snippet from the previous page [You must show your work here]:int foo(int a) {int w=2, x=3, y=4, z=5, v;w = a + x;w += bar(w, x);y = w + z;for (v = 0; v < 5; v++) {z += bar(w, y);}if (y > 20) return y;return w;}int bar(int a, int b) {int p=a, q=b, r, s=1;s += abs(-4);printf(“Values: %d,%d”, p, q);for (r = 0; r < 10; r++) {q = q + p;printf(“New q: %d”, q);}return q;}Page 9 of 12

9. Single Cycle Datapath [12 pts]After graduation you join a start-up company that specializes in single-cycle LC2K processors(similar <strong>to</strong> those studied in class). The company wants you <strong>to</strong> do some verification of theirnewest processor <strong>to</strong> ensure correctness, thus you decide <strong>to</strong> develop some single-instruction testsprograms <strong>to</strong> check that the control ROM is working properly.Below is a table of possible bugs that you are checking for. For instance the first row considersthe possibility that control signal D (as shown in the picture) is forced <strong>to</strong> always be 0 (in jargon,it is said <strong>to</strong> be ‘stuck-at 0’). Which LC2K instructions could be used <strong>to</strong> reveal this bug? For eachbug, circle all instructions that could be used <strong>to</strong> expose the bug by sending them <strong>to</strong> the processorand then checking the results (by inspecting memory and register file).D stuck-at 0 add nand sw lw beq jalr noop haltC stuck-at 1 add nand sw lw beq jalr noop haltB stuck-at 0 add nand sw lw beq jalr noop haltA stuck-at 1 add nand sw lw beq jalr noop haltPage 10 of 12

10. ISA Design [14 pts]Your <strong>EECS</strong> <strong>370</strong> instructional staff has come up with a ridiculously fast ISA that just embarrassesopposing ISAs. This new ISA, ShoeLace, is byte-addressable, stack-based and it contains twoaccumula<strong>to</strong>rs (ACC1 and ACC2) <strong>to</strong> assist with computations. There are three instructions typesthat vary in length and are detailed below.R-type instructionsbits 7-4 bits 3-0unused opcodeInstruction Opcode Actionmov1 0001 Pop the <strong>to</strong>p value of the stack and s<strong>to</strong>re it in<strong>to</strong> ACC1mov2 0011 Pop the <strong>to</strong>p value of the stack and s<strong>to</strong>re it in<strong>to</strong> ACC2pop 0000 Pop the <strong>to</strong>p value of the stackhalt 1000 S<strong>to</strong>p the programI-type instructions(immediate is a 12-bit valuein 2’s complement form)bits 15-4 bits 3-0immediateopcodeInstruction Opcode Actionpushi 0010 Push immediate on<strong>to</strong> the stackload 0110 Load MEM[ACC1+immediate] on<strong>to</strong> the <strong>to</strong>p of the stacks<strong>to</strong>re 0101 S<strong>to</strong>re the <strong>to</strong>p value of the stack in<strong>to</strong> MEM[ACC1+immediate]bgz 0100If (ACC1 ≥ 0) PC = PC+2+immediate, else PC=PC+2; ACC1=0If ACC1 is greater than zero, branch. Then always set ACC1 <strong>to</strong>zero. Note that PC increments by 2, since this instruction takes 2bytes.U-type instructionsbits 15-14 bits 13-4 bits 3-0dest code unused opcodeInstruction Opcode Dest code Mnemonic Actionneg. 100100 neg.acc1 ACC1 = (-1)*ACC111 neg.acc2 ACC2 = (-1)*ACC2add. 101100 add.acc1 ACC1 = ACC1+ACC211 add.acc2 ACC2 = ACC1+ACC2Page 11 of 12

a) [1 points] Is this a RISC or CISC architecture? Circle your response.RISCCISCb) [3 points] Translate the following assembly instructions in<strong>to</strong> machine code.Assembly Instructionload -14add.acc1bgz 17Machine Code (hex)0b1111 1111 0010 0110 = 0xFF260b0000 0000 0000 1011 = 0x000B0b0000 0001 0001 0100 = 0x0114c) [10 points] Translate the following C instruction in<strong>to</strong> assembly instructions. Assume that ais s<strong>to</strong>red at memory address 4, b at address 8 and the result should be s<strong>to</strong>red at address 12.Both accumula<strong>to</strong>rs are initialized at 0. Make sure branch offsets are specified as integervalues, not labels. Use the table below for your code. You may not need <strong>to</strong> use all the rowsavailable.if (b >12) result = a;Retrieve b from memoryload 8Compare b <strong>to</strong> 12mov2pushi 12mov1neg.acc2add.acc1//acc1 is 12-bEvaluate if conditionbgz 4Set result <strong>to</strong> aload 4s<strong>to</strong>re 12Page 12 of 12