KHON KAEN UNIVERSITY DEPARTMENT OF ELECTRICAL ENGINEERING

khon kaen university department of electrical engineering à¸à¸²à¸£à¸à¸à¸¥à¸à¸ ...

khon kaen university department of electrical engineering à¸à¸²à¸£à¸à¸à¸¥à¸à¸ ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>KHON</strong> <strong>KAEN</strong> <strong>UNIVERSITY</strong><br />

<strong>DEPARTMENT</strong> <strong>OF</strong> <strong>ELECTRICAL</strong> <strong>ENGINEERING</strong><br />

การทดลอง LAB06 : คุณสมบัติและวงจรเบื ้องตนไอซี Logic Gates<br />

วัตถุประสงค :<br />

1. ตองการใหนักศึกษาไดเขาใจถึงคุณสมบัติของไอซี ชนิด TTL<br />

2. ตองการใหนักศึกษาจําลองการทํางานและวัดคุณสมบัติของไอซี ชนิด TTL<br />

อุปกรณ : 1. Computer set + TINA program 1 เครื่อง<br />

2. Function Generator 1 เครื่อง<br />

3. Oscilloscope 1 เครื่อง<br />

4. Dual Power supply 1 เครื่อง<br />

5. IC 74LS00 (NAND - TTL) 1 ตัว<br />

IC 74LS86 (Exclusive OR - TTL) 1 ตัว<br />

งานที่ตองทํากอนเขาปฏิบัติการ :<br />

1. ใหนักศึกษาหาคุณสมบัติ (Specification) และทํารายงานของไอซีเบอรตางๆ ขางตน กอนเขา<br />

ปฏิบัติการ<br />

2. ใหนักศึกษาสรางวงจรดังรูปที่ 6.1 โดยใชโปรแกรม TINA แลวเก็บไวในรูปของไฟลสกุล tsc<br />

คําแนะนํา :<br />

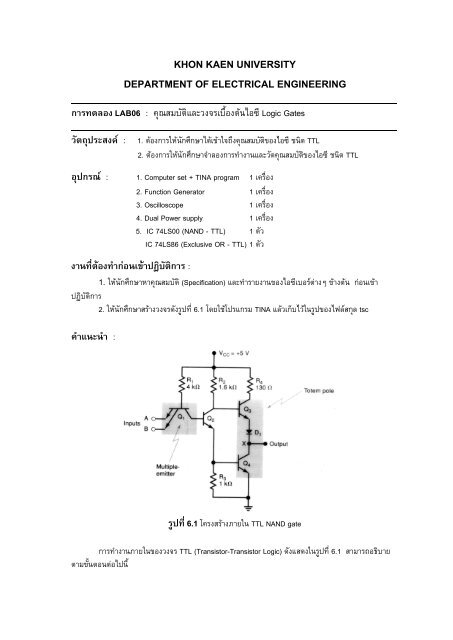

รูปที่ 6.1 โครงสรางภายใน TTL NAND gate<br />

การทํางานภายในของวงจร TTL (Transistor-Transistor Logic) ดังแสดงในรูปที่ 6.1 สามารถอธิบาย<br />

ตามขั้นตอนตอไปนี้

1. เมื ่อมีสัญญาณเขา Vin ที่สภาวะโลจิก “1” เขาที่ขาอีมิตเตอร (E) ของ Q1 จะทําใหมีกระแสไหลจากขา<br />

เบส (B) ไปยังขาคอลเล็กเตอร (C) ของ Q1 กระแสนี้จะไหลเขาที่ขาเบส (B) ของ Q2 ทําใหทรานซิสเตอร Q2<br />

ทํางาน (On) เกิดกระแสไหลผาน R2 เขาที่ขาคอลเล็กเตอร (C) ของ Q2 ผานออกทางขาอีมิตเตอร (E) ของ Q2<br />

ผาน R3 ทําใหเกิดแรงดันตกครอม R3 สูงขึ้น จนกระทั่งเพียงพอทําใหทรานซิสเตอร Q4 ทํางาน (On) สงผล<br />

ทําใหแรงดันที่ขาคอลเล็กเตอร (C) ของ Q4 ลดต่ําลง หรือแรงดันที่ขาออก Vout มีสภาวะโลจิก “0” ใน<br />

ขณะเดียวกันแรงดันที่ขาเบส (B) ของ Q3 จะลดต่ําลง เนื่องจากแรงดันตกครอม R2 สูงขึ้น หรือทรานซิสเตอร<br />

Q2 อยูในสภาวะอิ่มตัว (Saturation) ดังนั้นจึงไมมีกระแสไหลเขาที่ขาเบส (B) ของ Q3 ทําใหทรานซิสเตอร Q3<br />

ไมทํางาน (Off)<br />

2. เมื ่อมีสัญญาณเขา Vin ที่สภาวะโลจิก “0” เขาที่ขาอีมิตเตอร (E) ของ Q1 จะทําใหทรานซิสเตอร Q1<br />

ทํางาน (On) กระแสไหลเบส (B) จึงเปลี่ยนทิศทางไหลจากขาเบส (B) ไปยังขาอีมิตเตอร (E) ของ Q1 นั้นคือ<br />

จะไมมีกระแสไหลเขาที่ขาเบส (B) ของ Q2 ทําใหทรานซิสเตอร Q2 ไมทํางาน (Off) ดังนั้นจึงไมมีกระแสอีมิต<br />

เตอรไหลผาน R3 นั้นคือจะไมมีกระแสไหลเขาที่ขาเบส (B) ของ Q4 ทรานซิสเตอร Q4 จึงไมทํางาน (Off) ใน<br />

ขณะเดียวกันเมื่อไมมีกระแสอีมิตเตอร ก็จะไมมีกระแสคอลเล็กเตอรดวย แตจะมีกระแสไหลผาน R2 เขาที่ขาเบส<br />

(B) ของ Q3 ทําใหทรานซิสเตอร Q3 ทํางาน (On) นั้นคือจะทําใหเกิดกระแสไหลผาน R4 เขาที่ขาคอลเล็กเตอร<br />

(C) และไหลออกที่ขาอีมิตเตอร (E) ของ Q3 ผานไดโอด D1 ไปยังโหลด ดังนั้นแรงดันที่ขาออก Vout จึงยก<br />

สูงขึ้น เกิดเปนสภาวะโลจิก “1”<br />

การทดลอง :<br />

1. การจําลองการทํางานภายในโดยโปรแกรม TINA<br />

1.1 โหลดไฟลสกุล tsc ลงบนโปรแกรม TINA และกําหนดสัญญาณเขา Vin โดยการเชื่อม A และ B<br />

เขาดวยกัน และกําหนดตําแหนงจุดวัด In, Out ในรูปที่ 6.1<br />

1.2 กําหนดคุณสมบัติของ Vin เปน Input และตําแหนงจุดวัด In, Out เปน Output<br />

1.3 ทําการวิเคราะหแบบ DC Analysis ชนิด DC Transfer Characteristic โดยวิเคราะหจาก 0V<br />

ถึง 5V กําหนดการวิเคราะห 1000 จุด<br />

1.4 เก็บผลลัพทการจําลองระหวางแรงดันเขา Vin และ Vout เพื่อเปรียบเทียบกับผลการทดลอง<br />

2. การทดลองการทํางานภายในโดยใชการตอทดลองจริง<br />

2.1 นําไอซี TTL เบอร 74LS00 ตอลงบน Bread Board ตอแรงดัน +5V เขาที่ขา Vcc และตอ 0V<br />

เขาที่ขา Gnd สัญญาณเขา A,B ตอรวมกัน แลวจึงตอเขาที่ขาสัญญาณ Oscilloscope ชองทาง A สวนสัญญาณ<br />

ออก Y ตอเขาที่สัญญาณ Oscilloscope ชองทาง B<br />

2.2 เปดเครื่อง Oscilloscope ปรับตั้งจนกระทั่งไดสัญญาณทร็ก (Tracker) แลวจึงกําหนดคาเริ่มตน<br />

1V/Div ทั้งสองชองทาง ตั้งระดับอางอิง (Reference) ไวที่ต่ําแหนงต่ําสุดของจอ<br />

2.3 ปรับแรงดันแหลงจายไฟอีกชุดหนึ่งระดับ 0V ตอสัญญาณนี้เขาที่สัญญาณเขา A,B แลวจึงปรับ<br />

แรงดันแหลงจายไฟจากระดับ 0V ถึง 5V สเตปละ 0.1V แลววัดระดับสัญญาณเขา A,B และสัญญาณออก Y นํา<br />

ขอมูลที่ไดนํามาวาดรูปกราฟระหวางแรงดันเขา Vin กับแรงดันออก Vout<br />

หมายเหตุ: ในกรณีผลของสัญญาณออก Y นอยมาก อาจจะเพิ่มระดับสเตปเปน 0.5V ได<br />

LAB06-2

สิ่งที ่ตองการ: 1. นําผลการทดลองในขอที่ 1. เปรียบเทียบกับผลการทดลองในขอที่ 2 โดยการนําผลการทดลอง<br />

มาวาดรูปกราฟในรูปเดียวกัน<br />

2. จากผลการทดลองในขอที่ 1 และขอที่ 2 จงหาคาคุณสมบัติ VIH, VIL, VOH, VOL<br />

3. การจําลองหาคุณสมบัติดานโลจิกโดยโปรแกรม TINA<br />

3.1 สรางวงจรดังรูปที่ 6.2 โดยใชโปรแกรม TINA<br />

รูปที่ 6.2 วงจรทดลองหาคุณสมบัติดานโลจิก<br />

3.2 เลือกโหมด Interactive mode ชนิด Digital mode โดยการกดปุมไปที่ Interactive สังเกต<br />

สภาวะที่เปลี่ยนแปลง แลวนํามาเขียนเปนตาราง Truth table หากมีการเปลี่ยนแปลงเร็วมาก ใหไปกําหนด<br />

Option ในโหมด Interactive mode โดยเลือก Simulation time Unit = 1m และ Animation time Unit = 10<br />

3.3 เลือกการวิเคราะหชนิด Digital Timing Analysis โดยการกดปุม Analysis และกําหนดคาสุดทาย<br />

5mS แลวเก็บผลลัพทการจําลองในรูปสัญญาณ Waveform เพื่อนํามาเปรียบเทียบกับผลการทดลองจริง<br />

4. การทดลองหาคุณสมบัติดานโลจิกโดยการตอทดลองจริง<br />

4.1 นําไอซี TTL เบอร 74LS86 ตอลงบน Bread Board ตอแรงดัน +5V เขาที่ขา Vcc และตอ 0V<br />

เขาที่ขา Gnd สัญญาณเขา A เขาที่ขาสัญญาณ Oscilloscope ชองทาง A สวนสัญญาณออก Y ตอเขาที่<br />

สัญญาณ Oscilloscope ชองทาง B สําหรับสัญญาณเขา B ใหตอกับสวิตทโลจิก<br />

4.2 เปดเครื่อง Function Generator แลวจึงกําหนดคาตามขั้นตอนดังนี้<br />

- Waveform : Square wave<br />

- Frequency : 2kHz<br />

- Amplitude : 2.5V<br />

- Offset : 2.5V<br />

แลวจึงตอสัญญาณที่ไดเขากับสัญญาณเขา A ของไอซี 74LS86<br />

4.3 ตอขาสัญญาณเขา B ของไอซีเบอร 74LS86 เขากับ Gnd หรือโลจิก “0” ใหตรวจจับและเก็บ<br />

ผลลัพทของสัญญาณเขา A และสัญญาณออก Y โดยใช Oscilloscope<br />

4.4 ตอขาสัญญาณเขา B ของไอซีเบอร 74LS86 เขากับ Vcc หรือโลจิก “1” ใหตรวจจับและเก็บ<br />

LAB06-3

ผลลัพทของสัญญาณเขา A และสัญญาณออก Y โดยใช Oscilloscope<br />

4.5 นําผลการทดลองในขอ 4.3 รวมกับผลการทดลองในขอ 4.4 โดยกําหนดใหสัญญาณเขา A เปน<br />

สัญญาณอางอิง นํามาเขียนกราฟสัญญาณในรูปเดียวกัน<br />

สิ่งที ่ตองการ: 1. นําผลการทดลองในขอที่ 3 เปรียบเทียบกับผลการทดลองในขอที่ 4 โดยการนําผลการทดลอง<br />

มาวาดกราฟในรูปเดียวกัน<br />

เงื่อนไขการทดลองปฏิบัติการ :<br />

สําหรับการทดลอง LAB06: คุณสมบัติและวงจรเบื ้องตนไอซี Logic Gate เมื ่อทําการทดลองเสร็จ<br />

จะตองนําผลการทดลอง เสนออาจารยผูควบคุมแลป และจะตองตอบคําถามของอาจารยผูควบคุมแลป เมื ่อ<br />

ครบถวนแลว อาจารยผูควบคุมแลปจะเซนตชื ่อกํากับผลการทดลองนั้นๆ หากในรายงานไมมีลายเซนตจะไมได<br />

รับการตรวจ<br />

ตัวอยางคําถาม :<br />

1. การทํางานภายในของวงจร TTL จะเปนอยางไร เมื ่อสัญญาณเขา Input มีโลจิกตางกัน เชน A มี<br />

โลจิกเปน “0” และ B มีโลจิกเปน “1”<br />

2. ทรานซิสเตอร Q1 จะเริ่มทํางาน เมื ่อแรงดันที่ขาสัญญาณเขา Input มีแรงดันไมมากกวาเทาไร<br />

เปนอยางไร<br />

3. ลักษณะ Totem pole มีการทํางานเปนอยางไร<br />

4. ขณะสัญญาณออก Output มีสภาวะโลจิก “0” จะทําใหแรงดันขาออก Vout เทาไร<br />

5. ขณะสัญญาณออก Output มีสภาวะโลจิก “1” จะทําใหแรงดันขาออก Vout เทาไร<br />

6. ในขณะที่ทรานซิสเตอรอยูในสภาวะทํางาน (On) จะมีคุณสมบัติอยางไร<br />

7. ในขณะที่ทรานซิสเตอรอยูในสภาวะไมทํางาน (Off) จะมีคุณสมบัติอยางไร<br />

8. ในการจําลองการทํางานจะรูไดอยางไรวาทรานซิสเตอรอยูในสภาวะทํางาน (On)<br />

9. ในการจําลองการทํางานจะรูไดอยางไรวาทรานซิสเตอรอยูในสภาวะไมทํางาน (Off)<br />

10. ผลการทดลองในหัวขอ 1.4 เปนอยางไร อธิบายเหตุผลพอสังเขป<br />

11. ผลการทดลองในหัวขอ 1.4 จะลบสัญญาณที่ไมจําเปนออก จะทําอยางไร<br />

12. รูปความสัมพันธระหวางแรงดันเขา Vin กับแรงดันออก Vout ของการวัดโดยใช Oscilloscope<br />

13. ความแตกตางระหวางผลของการจําลองกับผลของการทดลองเปนอยางไร<br />

14. ความถี่ของสัญญาณ A และ B มีคาเทาไร จึงจะเหมาะสมทําใหสามารถเห็นการเปลี่ยนแปลงได<br />

15. ตาราง Truth table ของการจําลองในหัวขอ 3.2 เปนอยางไร อธิบายวาหามาไดอยางไร<br />

16. ตาราง Truth table ของการจําลองในหัวขอ 3.3 เปนอยางไร อธิบายวาหามาไดอยางไร<br />

17. การรวมสัญญาณจากการวัดโดย Oscilloscope ในหัวขอ 4.5 ทําอยางไร<br />

18. ตาราง Truth table ของการทดลองในหัวขอ 4.5 เปนอยางไร อธิบายวาหามาไดอยางไร<br />

รศ.มงคล ลี้ประกอบบุญ<br />

LAB06-4