System-on-Chip Design Flow

System-on-Chip Design Flow

System-on-Chip Design Flow

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

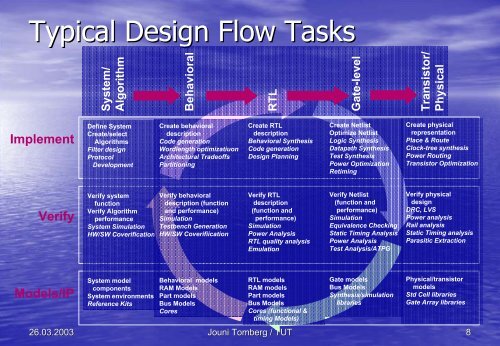

Typical <strong>Design</strong> <strong>Flow</strong> Tasks<br />

Implement<br />

Verify<br />

Models/IP<br />

<str<strong>on</strong>g>System</str<strong>on</strong>g>/<br />

Algorithm<br />

Define <str<strong>on</strong>g>System</str<strong>on</strong>g><br />

Create/select<br />

Algorithms<br />

Filter design<br />

Protocol<br />

Development<br />

Verify system<br />

functi<strong>on</strong><br />

Verify Algorithm<br />

performance<br />

<str<strong>on</strong>g>System</str<strong>on</strong>g> Simulati<strong>on</strong><br />

HW/SW Coverificati<strong>on</strong><br />

<str<strong>on</strong>g>System</str<strong>on</strong>g> model<br />

comp<strong>on</strong>ents<br />

<str<strong>on</strong>g>System</str<strong>on</strong>g> envir<strong>on</strong>ments<br />

Reference Kits<br />

Behavioral<br />

Create behavioral<br />

descripti<strong>on</strong><br />

Code generati<strong>on</strong><br />

Wordlength optimizatiu<strong>on</strong><br />

Architectural Tradeoffs<br />

Partiti<strong>on</strong>ing<br />

Verify behavioral<br />

descripti<strong>on</strong> (functi<strong>on</strong><br />

and performance)<br />

Simulati<strong>on</strong><br />

Testbench Generati<strong>on</strong><br />

HW/SW Coverifiicati<strong>on</strong><br />

Behavioral models<br />

RAM Models<br />

Part models<br />

Bus Models<br />

Cores<br />

26.03.2003 Jouni Tomberg / TUT 8<br />

RTL<br />

Create RTL<br />

descripti<strong>on</strong><br />

Behavioral Synthesis<br />

Code generati<strong>on</strong><br />

<strong>Design</strong> Planning<br />

Verify RTL<br />

descripti<strong>on</strong><br />

(functi<strong>on</strong> and<br />

performance)<br />

Simulati<strong>on</strong><br />

Power Analysis<br />

RTL quality analysis<br />

Emulati<strong>on</strong><br />

RTL models<br />

RAM models<br />

Part models<br />

Bus Models<br />

Cores (functi<strong>on</strong>al &<br />

timing Models)<br />

Gate-level<br />

Create Netlist<br />

Optimize Netlist<br />

Logic Synthesis<br />

Datapath Synthesis<br />

Test Synthesis<br />

Power Optimizati<strong>on</strong><br />

Retiming<br />

Verify Netlist<br />

(functi<strong>on</strong> and<br />

performance)<br />

Simulati<strong>on</strong><br />

Equivalence Checking<br />

Static Timing Analysis<br />

Power Analysis<br />

Test Analysis/ATPG<br />

Gate models<br />

Bus Models<br />

Synthesis/simulati<strong>on</strong><br />

libraries<br />

Transistor/<br />

Physical<br />

Create physical<br />

representati<strong>on</strong><br />

Place & Route<br />

Clock-tree synthesis<br />

Power Routing<br />

Transistor Optimizati<strong>on</strong><br />

Verify physical<br />

design<br />

DRC, LVS<br />

Power analysis<br />

Rail analysis<br />

Static Timing analysis<br />

Parasitic Extracti<strong>on</strong><br />

Physical/transistor<br />

models<br />

Std Cell libraries<br />

Gate Array libraries