In the Name of God, the Compassionate, the Merciful

In the Name of God, the Compassionate, the Merciful

In the Name of God, the Compassionate, the Merciful

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

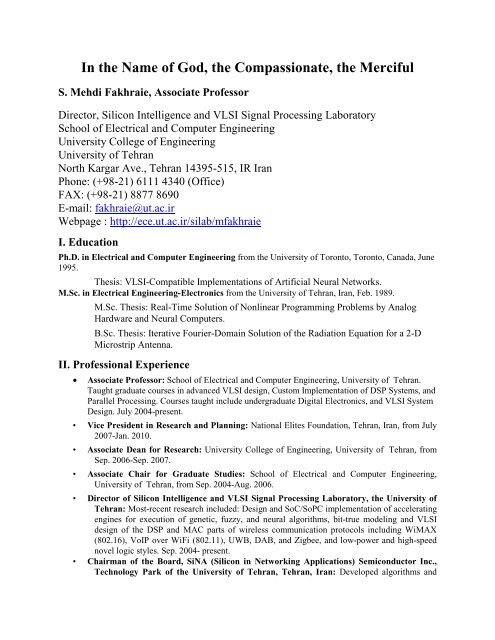

<strong>In</strong> <strong>the</strong> <strong>Name</strong> <strong>of</strong> <strong>God</strong>, <strong>the</strong> <strong>Compassionate</strong>, <strong>the</strong> <strong>Merciful</strong><br />

S. Mehdi Fakhraie, Associate Pr<strong>of</strong>essor<br />

Director, Silicon <strong>In</strong>telligence and VLSI Signal Processing Laboratory<br />

School <strong>of</strong> Electrical and Computer Engineering<br />

University College <strong>of</strong> Engineering<br />

University <strong>of</strong> Tehran<br />

North Kargar Ave., Tehran 14395-515, IR Iran<br />

Phone: (+98-21) 6111 4340 (Office)<br />

FAX: (+98-21) 8877 8690<br />

E-mail: fakhraie@ut.ac.ir<br />

Webpage : http://ece.ut.ac.ir/silab/mfakhraie<br />

I. Education<br />

Ph.D. in Electrical and Computer Engineering from <strong>the</strong> University <strong>of</strong> Toronto, Toronto, Canada, June<br />

1995.<br />

Thesis: VLSI-Compatible Implementations <strong>of</strong> Artificial Neural Networks.<br />

M.Sc. in Electrical Engineering-Electronics from <strong>the</strong> University <strong>of</strong> Tehran, Iran, Feb. 1989.<br />

M.Sc. Thesis: Real-Time Solution <strong>of</strong> Nonlinear Programming Problems by Analog<br />

Hardware and Neural Computers.<br />

B.Sc. Thesis: Iterative Fourier-Domain Solution <strong>of</strong> <strong>the</strong> Radiation Equation for a 2-D<br />

Microstrip Antenna.<br />

II. Pr<strong>of</strong>essional Experience<br />

• Associate Pr<strong>of</strong>essor: School <strong>of</strong> Electrical and Computer Engineering, University <strong>of</strong> Tehran.<br />

Taught graduate courses in advanced VLSI design, Custom Implementation <strong>of</strong> DSP Systems, and<br />

Parallel Processing. Courses taught include undergraduate Digital Electronics, and VLSI System<br />

Design. July 2004-present.<br />

• Vice President in Research and Planning: National Elites Foundation, Tehran, Iran, from July<br />

2007-Jan. 2010.<br />

• Associate Dean for Research: University College <strong>of</strong> Engineering, University <strong>of</strong> Tehran, from<br />

Sep. 2006-Sep. 2007.<br />

• Associate Chair for Graduate Studies: School <strong>of</strong> Electrical and Computer Engineering,<br />

University <strong>of</strong> Tehran, from Sep. 2004-Aug. 2006.<br />

• Director <strong>of</strong> Silicon <strong>In</strong>telligence and VLSI Signal Processing Laboratory, <strong>the</strong> University <strong>of</strong><br />

Tehran: Most-recent research included: Design and SoC/SoPC implementation <strong>of</strong> accelerating<br />

engines for execution <strong>of</strong> genetic, fuzzy, and neural algorithms, bit-true modeling and VLSI<br />

design <strong>of</strong> <strong>the</strong> DSP and MAC parts <strong>of</strong> wireless communication protocols including WiMAX<br />

(802.16), VoIP over WiFi (802.11), UWB, DAB, and Zigbee, and low-power and high-speed<br />

novel logic styles. Sep. 2004- present.<br />

• Chairman <strong>of</strong> <strong>the</strong> Board, SiNA (Silicon in Networking Applications) Semiconductor <strong>In</strong>c.,<br />

Technology Park <strong>of</strong> <strong>the</strong> University <strong>of</strong> Tehran, Tehran, Iran: Developed algorithms and

•<br />

designed ASIC and FPGA microchips and system boards for implementation <strong>of</strong> integrated<br />

broadband gateways for secure <strong>of</strong>fice and home applications. Sep. 2004-present.<br />

Executive Chair, <strong>the</strong> First, Second, and Third National Congresses <strong>of</strong> <strong>the</strong> Elites,<br />

Tehran, Iran, August 2007, August 2008, and Oct. 2009.<br />

• Executive Chair, <strong>the</strong> Second National <strong>In</strong>novations and <strong>In</strong>ventions Festival, Tehran,<br />

Iran, Feb. 2010.<br />

• Executive Chair, <strong>the</strong> First, and Second <strong>In</strong>ternational Conferences on Automotive<br />

Electronics, Tehran, Iran, Feb. 2008 and Feb. 2009.<br />

• Director, ASIC/SOC Design, Valence Semiconductor <strong>In</strong>c., Toronto, Canada: Technical<br />

supervision <strong>of</strong> a team <strong>of</strong> system and ASIC design engineers working on signal integrity and<br />

power-grid analysis <strong>of</strong> Valence HomePlug six million transistor chip, and responsible for<br />

Valence Family Radio System (FRS) baseband 2.5 million transistor chip in TSMC 0.25um<br />

CMOS, a full-digital architecture with DSP-system power, speed and area optimization and<br />

integrated GPS data link, and in charge <strong>of</strong> its physical implementation including layout<br />

delivery and manufacturability tests. November 2002-April 2003.<br />

• Director, VLSI Design <strong>of</strong> Valence <strong>In</strong>tegrated Gateway Architecture, Valence<br />

•<br />

Semiconductor <strong>In</strong>c., Dubai and Canada Offices: Developed architecture and implemented a<br />

dual ARM946-8888, 20-block memory, 20-millioin transistor ASIC for a flexible yet<br />

affordable voice-data gateway in TSMC 0.18um CMOS. January 2001-October 2002.<br />

Consultant, Valence Semiconductor <strong>In</strong>c.: Dubai and Canada Offices, Aug. 2000-Dec. 2000.<br />

• Founding Director <strong>of</strong> VLSI Circuits and Systems Laboratory, <strong>the</strong> University <strong>of</strong><br />

Tehran: Most-recent research included: Design and implementation <strong>of</strong> dedicated DSP<br />

hardware for digital subscriber lines (ADSL line-communication devices), and mobilecommunication<br />

applications; design <strong>of</strong> customized high-performance architectures for parallel<br />

DSP processors; development <strong>of</strong> several CMOS low-power logic styles; implementation <strong>of</strong><br />

analog artificial neural networks using submicron CMOS technologies; design <strong>of</strong> new efficient<br />

architectures for FPGAs and FPGA applications in industrial environments; networks <strong>of</strong><br />

parallel processors and <strong>the</strong>ir applications. September 1996- June 2001.<br />

• Executive Chair, <strong>the</strong> Twelfth IEEE <strong>In</strong>ternational Conference on Mocroelectronics<br />

(ICM 2000), Tehran, Iran, Oct. 30- Nov. 2, 2000, Conference Proceedings available on IEEE<br />

Xplore site: http://ieeexplore.ieee.org .<br />

• Associate Chair <strong>of</strong> Graduate Studies: Department <strong>of</strong> Electrical and Computer Engineering,<br />

University <strong>of</strong> Tehran. September 1999-March 2000<br />

• Director <strong>of</strong> Electronics Group: Department <strong>of</strong> Electrical and Computer Engineering,<br />

University <strong>of</strong> Tehran, since Sep. 1996-March 2000.<br />

• Assistant Pr<strong>of</strong>essor: Department <strong>of</strong> Electrical and Computer Engineering, University <strong>of</strong><br />

Tehran. Taught graduate courses in advanced VLSI design, VLSI array processing, hardware<br />

implementation <strong>of</strong> neural networks and intelligent systems, BiCMOS circuit design, and RF<br />

Microelectronics. Courses taught include undergraduate Electronic Circuits, Digital<br />

Electronics, Computer-Aided Design <strong>of</strong> Digital Circuits, and VLSI System Design. September<br />

1995-July 2004.<br />

• Research Assistant: Optoelectronics Lab, University <strong>of</strong> Toronto. Sept. 1993-Aug. 1995.<br />

• Research Assistant: Computer <strong>In</strong>tegrated Manufacturing and VLSI Research Laboratories,<br />

University <strong>of</strong> Toronto. March 1991-August 1993.<br />

• Teaching Assistant: Department <strong>of</strong> ECE, University <strong>of</strong> Toronto, sessions 1991/1992,<br />

1992/1993, 1993/1994, 1994/1995.

• <strong>In</strong>structor: Department <strong>of</strong> ECE, University <strong>of</strong> Tehran. Feb. 1989-Dec. 1990.<br />

• Project Manager: Electronics Research Centre, University <strong>of</strong> Tehran. Feb. 1987-Aug. 1989.<br />

• Electrical Engineer: Electronics Research Centre, University <strong>of</strong> Tehran. Jan. 1986-Jan. 1987.<br />

• Researcher: Electronics Research Centre, University <strong>of</strong> Tehran. Aug. 1984-Dec. 1986.<br />

III. Special Skills<br />

• Architecture design <strong>of</strong> Network Processors and ASIC implementation <strong>of</strong> dedicated hardware for<br />

high-speed manipulation <strong>of</strong> networking protocols: (Achievement: Valence Gateway processor,<br />

emerged into IBG 20 million transistor product, 2001).<br />

• Design with focus on extreme cost-performance efficiency <strong>of</strong> voice/data multi-protocol<br />

integrated home/<strong>of</strong>fice gateways (Achievement: Valence <strong>In</strong>tegrated Broadband Gateway (IBG)<br />

product, 20 million transistors, 2002).<br />

• Design and optimization <strong>of</strong> dedicated hardware for high-performance signal processing systems<br />

(Achievements: Baseband 2.5 million transistor chip <strong>of</strong> Valence FRS system (2003), UT-VLSI<br />

Lab <strong>In</strong>dustrial Project: multi-protocol Flex/ERMES/POCSAG Pager chip (1999), and VLSI<br />

Lab ADSL baseband processors (2000)).<br />

• Design and implementation <strong>of</strong> general-purpose DSP hardware for mobile communication<br />

applications (Achievements: VLSI Lab variants <strong>of</strong> DSP processors (1996-1999)).<br />

• <strong>In</strong>tegration and implementation <strong>of</strong> image processing systems (Privately-funded activity: FPGA<br />

implementation <strong>of</strong> PCI high-speed image acquisition and processing system for midical and<br />

dental imaging purposes (1999)).<br />

• Development <strong>of</strong> wireless communication systems for sensor fusion, monitoring and control<br />

(VLSI Lab <strong>In</strong>dustrial Project: Custom wireless communication system, FPGA-MCU ASIC<br />

preparation <strong>of</strong> baseband system and fabricated bipolar integrated front end (1997-1999)) .<br />

• Design <strong>of</strong> dedicated hardware for one-way and two-way paging systems (Prepared working<br />

design on 8051 MCU/FPGA based platform for ASIC development environment (1998)).<br />

• Application <strong>of</strong> DSP systems to industrial environments (UT-VLSI Lab study based on developed<br />

ASIC designs (1997)).<br />

• <strong>In</strong>dustrial applications <strong>of</strong> Artificial Neural Networks (University <strong>of</strong> Toronto summer studies<br />

(1997-2000)).<br />

• Simulation, design, hardware implementation, and after-fabrication programming and test <strong>of</strong><br />

custom-designed neural-network hardware (University <strong>of</strong> Toronto(1994-1995)).<br />

• Design and implementation <strong>of</strong> mixed analog-digital circuits (employing memories, buffers,<br />

multiplexers, and dedicated analog processing engines for intelligent systems (1993-1995).<br />

• Certificate <strong>of</strong> Synopsys <strong>In</strong>c. for VHDL syn<strong>the</strong>sis and simulation training courses (1994).<br />

• Full familiarity with Cadence integrated design environment including NCSim Verification,<br />

BuildGtes Extreme Syn<strong>the</strong>sis and Power Optimization, SOC Encounter, Celtic crosstalk<br />

analysis, and Voltage Storm power grid analysis tools (used in making many digital and analog<br />

IC chips).<br />

• Set up <strong>of</strong> <strong>the</strong> environment and teaching <strong>of</strong> VLSI design using MAGIC and LEDIT VLSI design<br />

tools.<br />

• Design, installation, programming, and maintenance <strong>of</strong> computer-controlled IC test systems.<br />

• Programming experience with C and C++ languages: writing system-level and behavioral<br />

simulators for pre-implementation studies. Extensive experience with MATLAB and its signalprocessing<br />

and neural-network toolboxes.<br />

• Familiarity with different PC-based and UNIX-based computational platforms.<br />

• Design and programming <strong>of</strong> various analog and digital data acquisition systems.

• Working and programming <strong>of</strong> HP and Keithley semiconductor analysis instruments.<br />

• Parallel programming and applications <strong>of</strong> parallel array processors.<br />

• <strong>In</strong>tegration and optimization <strong>of</strong> digital systems using integrated circuits technology.<br />

IV. Research <strong>In</strong>terests: Present and Future<br />

• <strong>In</strong>telligent Processor Convergence: I have had plenty <strong>of</strong> activities on design <strong>of</strong> generalpurpose<br />

processors, DSP customized hardware engines, cores for intelligent systems, and<br />

network processors. <strong>In</strong> addition, I have designed and implemented several generations <strong>of</strong><br />

mixed-mode neural network intelligent processing systems. Now, I wish to work on <strong>the</strong><br />

idea <strong>of</strong> “<strong>In</strong>telligent Processor Convergence,” in <strong>the</strong> context <strong>of</strong> <strong>the</strong> massive market for<br />

intelligent signal-processing and home/<strong>of</strong>fice networking products, a context that adopts<br />

<strong>the</strong> best <strong>of</strong> all worlds for highest cost/performnace to supply such pieces <strong>of</strong> hardware to<br />

improve <strong>the</strong> life <strong>of</strong> every human being.<br />

• Network processor and broadband gateway architectures and <strong>the</strong>ir implementation:<br />

I have worked as director <strong>of</strong> an industrial team working on development <strong>of</strong> dedicated<br />

hardware and related s<strong>of</strong>tware for highly integrated, high-speed, and yet-affordable<br />

home gateway processors. I realize that <strong>the</strong>re are many improvements and optimizations<br />

in architecture and implementation <strong>of</strong> gateway chips that would allow <strong>the</strong>m to become<br />

an affordable integral part <strong>of</strong> every home in <strong>the</strong> world.<br />

• Fully-optimized low-power DSP engines for communication systems: My previous<br />

experience includes development <strong>of</strong> custom engines for low-power FRS baseband chip;<br />

two-way and one-way multi-protocol paging systems; and a custom ADSL system.<br />

These activities have led me to identify many improvements in DSP algorithms and<br />

<strong>the</strong>ir implementation which potentially open up new horizons for reducing area, power<br />

and system-integration costs while improving <strong>the</strong> performance.<br />

• Manufacturability and Signal <strong>In</strong>tegrity <strong>of</strong> ASIC chips: Having worked on <strong>the</strong> power<br />

grid analysis and signal integrity <strong>of</strong> <strong>the</strong> Valence six million transistor Home Plug ASIC<br />

chip, I have been in short <strong>of</strong> tools and methodologies to incorporate SI and power<br />

related timing considerations in <strong>the</strong> design cycle right from beginning <strong>of</strong> RTL syn<strong>the</strong>sis<br />

and chip planning. Database convergence, virtual chip prototyping, concept <strong>of</strong> wire<br />

syn<strong>the</strong>sis, realistic interconnect delay estimation, extra delay margins considered from<br />

<strong>the</strong> beginning, and rapid detail routing are all techniques that are partly investigated by<br />

Cadence and Synopsys, but none has been evolved into a mature design flow, and <strong>the</strong>re<br />

are yet many flaws to fill.<br />

• VLSI implementation <strong>of</strong> general DSP processors for communication applications:<br />

Having directed a 15-member team working in collaboration with industry on design and<br />

VLSI implementation <strong>of</strong> a dedicated DSP processor for use in GSM mobile handsets, I<br />

am in a position to clearly recognize that <strong>the</strong> future mobile systems will constitute <strong>of</strong> a<br />

mixture <strong>of</strong> general processors and custom coprocessing hardware. This is a fact<br />

recognized by o<strong>the</strong>r researchers as well yielding to development <strong>of</strong> configurableinstruction<br />

processors and <strong>the</strong>ir required CAD tools. However, packetized-data mobile<br />

systems are in need <strong>of</strong> efficient packet processors as well. This is an area that I feel I am<br />

in a good position to contribute. I have worked on and have suggestions for many<br />

variants <strong>of</strong> such processors to be developed.<br />

• Development <strong>of</strong> hardware-emulation systems and custom ASIC development boards:<br />

Hardware and s<strong>of</strong>tware have been developed at UT-VLSI lab and several ASIC<br />

development industrial projects to provide high-performance FPGA systems for rapid<br />

evaluation <strong>of</strong> complex digital systems with maximum capacity <strong>of</strong> 30 million equivalent<br />

gates. Several generations <strong>of</strong> <strong>the</strong>se projects have been constructed. The one with<br />

100,000 equivalent-gate capacity has been used for DSP processor development<br />

emulation. Ano<strong>the</strong>r embedded system with 8051 CPU, memory, and FPGA was

developed and used in a two-way messaging (pager) project. Nowadays, embedded<br />

system IP providers development systems (e.g. MIPS nad ARM) will make average<br />

users needless <strong>of</strong> custom developments. However, an active development team should<br />

come with <strong>the</strong> expertise and speed to assemble custom development environments.<br />

Such a need appears almost always at interfaces side even when using some existing<br />

development systems, as we have done with ARM <strong>In</strong>tegrated System and our custom<br />

interfaces in Valence Semiconductor <strong>In</strong>c. and with our custom development<br />

environment for integrated broadband gateway ASIC at SiNA Semiconductor <strong>In</strong>c.<br />

• Hardware implementation <strong>of</strong> artificial neural networks (ANNs): Through <strong>the</strong>oretical<br />

analysis, extensive simulations using our custom-designed neural network simulator written in<br />

C, HSPICE circuit simulations, development <strong>of</strong> a new device and its model, and several cycles<br />

<strong>of</strong> chip fabrication, we have designed a new class <strong>of</strong> efficiently-hardware-implementable<br />

ANNs that employ a single MOS transistor as <strong>the</strong>ir synaptic block. The whole idea has been<br />

verified by a 10,000-transistor final test chip including 15 neurons and 270 synapses connected<br />

in three layers. Development <strong>of</strong> denser and more integrated digitally-interfaced analog-anddigital<br />

processing intelligent systems and neural networks are things that I see as future mustto-do<br />

activities.<br />

• Mixed-mode implementation <strong>of</strong> ANNs in submicron CMOS technologies: Developed,<br />

fabricated, and tested a 0.35um analog neural network with 3-D closed-boundary<br />

discriminating surfaces for pattern classification and recognition applications. This<br />

research has brought new ideas towards integration and application <strong>of</strong> mixed mode<br />

analog-digital massively parallel integrated systems with potential applications in<br />

intelligent systems and man-machine interface as outlined above.

V. Publications<br />

Books<br />

[1] S. Mehdi Fakhraie and K.C. Smith, VLSI-Compatible Implementations for Artificial<br />

Neural Networks. Boston: Kluwer Academic Publishers, 1997.<br />

Papers<br />

Journal Papers<br />

[1] F. Firouzi, M. E. Salehi, F. Wang, and S. M. Fakhraie, “An accurate model for s<strong>of</strong>t error<br />

rate estimation considering dynamic voltage and frequency scaling effects,” in Elsevier<br />

Microelectronics Reliability, accepted for publication,<br />

doi:10.1016/j.microrel.2010.08.016.<br />

[2] Mostafa E. Salehi, Mehrzad Samadi, Mehrdad Najibi, Ali Afzali-Kusha, Masoud Pedram,<br />

and Sied Mehdi Fakhraie, “Dynamic voltage and frequency scheduling for embedded<br />

processors considering power/performance trade<strong>of</strong>fs,” in IEEE Transactions on Very<br />

Large Scale <strong>In</strong>tegration (VLSI) Systems, accepted for publication, Digital Object<br />

Identifier: 10.1109/TVLSI.2010.2057520.<br />

[3] H. Parandeh-Afshar, S. M. Fakhraie, and O. Fatemi, “Parallel merged multiplieraccumulator<br />

coprocessor optimized for digital filters,” in Elsevier Journal <strong>of</strong> Computers<br />

& Electrical Engineering, vol. 36, issue 5, pp. 864-873, Sep. 2010.<br />

[4] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, “Bio-inspired imprecise<br />

computational blocks for efficient VLSI implementation <strong>of</strong> S<strong>of</strong>t-Computing Applications,”<br />

in IEEE Trans. Circuits and Systems I: Regular papers, pp. 850-862, vol. 57, no. 4,<br />

April 2010.<br />

[5] Amin Farmahini-Farahani, Shervin Vakili, Sied Mehdi Fakhraie, Saeed Safari, and Caro<br />

Lucas, “Parallel scalable hardware implementation <strong>of</strong> asynchronous discrete particle swarm<br />

optimization,” in Elsevier Journal <strong>of</strong> Engineering Applications <strong>of</strong> Artificial<br />

<strong>In</strong>telligence, vol. 23, no. 2, pp. 177-187, March 2010.<br />

[6] S. Vakili, S. M. Fakhraie, and S. Mohammadi, “Evolvable multi-processor: a novel MPSoC<br />

architecture with evolvable task decomposition and scheduling,” in IET Comput. Digit.<br />

Tech., vol. 4, no. 2, pp. 143–156, March 2010.<br />

[7] Mostafa E. Salehi and Sied Mehdi Fakhraie, “Quantitative analysis <strong>of</strong> packet-processing<br />

applications regarding architectural guidelines for network-processing-engine<br />

development,” in Elsevier Journal <strong>of</strong> System Architecture, vol. 55, no. 7-9, pp. 373–<br />

386, Sep. 2009.<br />

[8] H. R. Mahdiani and S. M. Fakhraie, “A cost-error tunable round-<strong>of</strong>f method: Finite-length<br />

absorption,” IEICE Electronic Express, vol. 6, no. 18, pp. 1312-1317, Sep. 2009.<br />

[9] S. Vakili, S. M. Fakhraie, S. Mohammadi, and A. Ahmadi, “Low-cost fault tolerance in<br />

evolvable multiprocessor systems: A graceful degradation approach,” Journal <strong>of</strong> Zhejiang<br />

University-Science A, co-published with Springer-Verlag GmbH, vol. 10, no. 6, pp.<br />

922-926, June 2009.<br />

[10] M. Hamzeh, H. R. Mahdiani, A. Saghafi, S. M. Fakhraie, and C. Lucas, “Computationally<br />

efficient active rule detection method: Algorithm and architecture,” in Elsevier Fuzzy Sets<br />

and Systems, vol. 160, no. 4, pp. 554-568, Feb. 2009.<br />

[11] F. Kashfi, S. M. Fakhraie, and S. Safari, “Designing an ultra-high-speed multiply-accumulate<br />

structure,” in Elsevier Microelectronics Journal, vol. 39, no. 12, pp. 1476-1484, Dec.<br />

2008.

[12] S. Rahmanian and S. Mehdi Fakhraie, “An optimal structure for implementation <strong>of</strong> digital<br />

filters,” in IEICE Electronic Express, vol. 4, no. 21, pp. 679-683, Nov. 2007.<br />

[13] F. Kashfi, A. Agah, S. Mehdi Fakhraie, and S. Safari, “15 GHz low-voltage-swing carrylookahead<br />

adder,” in IEICE Electronic Express, vol. 4, no. 22, pp. 696-700, Nov. 2007.<br />

[14] Mahdi Hamzeh, Sied Mehdi Fakhraie, and Caro Lucas, "S<strong>of</strong>t real-time fuzzy task<br />

scheduling for multiprocessor systems," in <strong>In</strong>ternational Journal <strong>of</strong> <strong>In</strong>telligent<br />

Technology, vol. 2, no. 4, pp. 211-216, Sep. 2007.<br />

[15] R. Rafati, S. Mehdi Fakhraie, and K. C. Smith, "A 16-bit barrel-shifter implemented in<br />

data-driven dynamic logic," in IEEE Trans. Circuits and Systems I: Regular papers, pp.<br />

2194-2202, vol. 53, no. 10, Oct. 2006.<br />

[16] S. Rahimian Omam, S. M. Fakhraie, and O. Shoaei, “Minimizing <strong>the</strong> adder cost in multiple<br />

constant multipliers,” in IEICE Electronic Express, vol. 3, no. 14, pp. 340-346, July 2006.<br />

[17] A. Pedram, M. R. Jamali, T. Pedram, S. M. Fakhraie, and C. Lucas, “Local linear model<br />

tree (LOLIMOT) reconfigurable parallel hardware,” in Transactions on Engineering,<br />

Computing and Technology, Poland, vol. 13, pp. 96-101, May 2006.<br />

[18] E. Rohani and S. Mehdi Fakhraie, "Round-<strong>of</strong>f error in block floating point structures," in<br />

IEE Electronics Letters, vol. 42, no. 3, Feb. 2006.<br />

[19] R. Rafati and S. Mehdi Fakhraie, "Data-driven dynamic logic," in Journal <strong>of</strong> <strong>the</strong> Faculty<br />

<strong>of</strong> Engineering <strong>of</strong> <strong>the</strong> University <strong>of</strong> Tehran, Fall 2005, (in Farsi).<br />

[20] S. Shamshiri, S. M. Fakhraie, and C. Lucas, "A genetic-algorithm solution for designing<br />

optimal forwarding tables," in Nasir J. <strong>of</strong> Science and Engineering, vol. 1, no. 1, Summer<br />

2005, (in Farsi).<br />

[21] S. Shamshiri and S. M. Fakhraie, "Genetic algorithm memory minimization for designing<br />

reconfigurable address lookup engine," in <strong>In</strong>t. J. <strong>of</strong> Computational <strong>In</strong>telligence and<br />

Applications, Imperial College Press, vol. 5, no. 1, pp. 69-80, March 2005.<br />

[22] S. R. Abdollahi, S. M. Fakhraie, and M. Kamarei, "A crystal-based low-voltage all-digital<br />

programmable ring oscillator," in Analog <strong>In</strong>tegrated Circuits and Signal Processing,<br />

Springer Science (Formerly published by Kluwer Academic Publishers), vol. 43, no. 2,<br />

pp. 147 – 157, May 2005.<br />

[23] Mehran Nadjarbashi, S. Mehdi Fakhraie, and Alireza Kaviani, “On routing architecture for<br />

hybrid FPGA,” in <strong>In</strong>t. J. <strong>of</strong> Science and Technology: Scientia Iranica, vol. 11, no. 3, pp.<br />

159-164, Summer 2004.<br />

[24] S. M. Fakhraie, H. Farshbaf, and K.C. Smith, "Scalable closed-boundary analog neural<br />

networks," in IEEE Trans. Neural Networks, vol. 15, no. 2, pp. 492-504, March 2004.<br />

[25] M. H. Tehranipour, S. M. Fakhraie, M. R. Movahedin, and Z. Navabi, "A low-cost at-speed<br />

BIST architecture for embedded processor and SRAM cores," in Journal <strong>of</strong> Electronic<br />

Testing, Theory and Applications, Kluwer Academic Publishers, vol. 20, pp. 155-168,<br />

April 2004.<br />

[26] M. H. Tehranipour, S. M. Fakhraie, M. Nourani, Z. Navabi, and M. R. Movahedin,<br />

"Embedded test for processor and memory cores in system-on-chips," in <strong>In</strong>t. J. <strong>of</strong> Science<br />

and Technology: Scientia Iranica, vol. 10, no. 4, pp. 486-494, Oct. 2003.<br />

[27] H. Zarei, O. Shoaei, and S. M. Fakhraie, “A 37-mW fully integrated GMSK modulator for<br />

DRRS standard in 0.6-um digital CMOS process,” in IEEE Trans. Circuits and Systems<br />

II, vol. 49, no. 7, pp. 513-520, July 2002.<br />

[28] B. S. Biria, S. M. Fakhraie, and C. Lucas, “Improvement <strong>of</strong> neural networks generalization<br />

by adaptive regularization parameters,” in Amirkabir Journal <strong>of</strong> Science and<br />

Technology, vol. 11, no. 43, pp. 348-360, Spring 2000, (in Farsi).

[29] A. Shamaie, S. M. Fakhraie, and B. Benhabib, “A new technique for accurate estimation <strong>of</strong><br />

partly-occluded-ellipse parameters,” in <strong>In</strong>t. J. <strong>of</strong> Science and Technology: Scientia<br />

Iranica, Electrical Engineering Issue, Fall 1999.<br />

[30] S. Mehdi Fakhraie, A. Konrad, and K.C. Smith, “Neuro-computation techniques in<br />

sampled-data electromagnetic-field problems,” in IEEE Trans. Magnetics, vol. 30, no. 5,<br />

pp. 3637-3640, Sep.1994.

Reviewed Conference Papers (Published in Proceedings <strong>of</strong> <strong>In</strong>ternational Conferences):<br />

[31] A. Yazdanbakhsh, M. E. Salehi, S. Safari, and S. M. Fakhraie, “Locality considerations in<br />

exploring custom instruction selection algorithms,” in Proc. 2nd Asia Symposium on<br />

Quality Electronic Design (ASQED2010), Penang, Malaysia, pp. 157-162, Aug. 2010.<br />

[32] F. Firouzi, S. Kiamehr, P. Monshizadeh, M. Saremi, A. Afzali-Kusha, and S. M. Fakhraie,<br />

“A model for transient fault propagation considering glitch amplitude and rise-fall time<br />

mismatch,” in Proc. 2nd Asia Symposium on Quality Electronic Design (ASQED2010),<br />

Penang, Malaysia, pp. 89-92, Aug. 2010.<br />

[33] S. R. Abdollahi, H. S. Al-Raweshidy, S. Mehdi Fakhraie,R. Nilavalan, and M. Kamarei,<br />

“Full duplex 60 GHz millimeter wave transmission over multi-mode fiber,” in Proc. Second<br />

<strong>In</strong>ternational Conference on Ubiquitous and Future Networks (ICUFN 2010), Jejo<br />

Island, Korea, pp. 222-226, June 2010.<br />

[34] M. Ahmadi and S. M. Fakhraie, “Optimization <strong>of</strong> Viterbi decoder parameters for WRAN<br />

system,” in Proc. 2nd <strong>In</strong>ternational Conference on Future Computer and<br />

Communication (ICFCC), 2010, Wuhan, China, pp. V3-53-56, May 2010.<br />

[35] M. Ahmadi, E. Rohani, Pooya Monshizadeh Naeeni, and S. M. Fakhraie, “Modeling and<br />

performance evaluation <strong>of</strong> IEEE 802.22 physical layer,” in Proc. 2nd <strong>In</strong>ternational<br />

Conference on Future Computer and Communication (ICFCC), 2010, Wuhan, China,<br />

pp. V3-62-66, May 2010.<br />

[36] A. Azarpeyvand, M. E. Salehi, F. Firouzi, A. Yazdanbakhsh, and S. M. Fakhraie, “<strong>In</strong>struction<br />

reliability analysis for embedded processors,” in Proc. IEEE 13th <strong>In</strong>ternational<br />

Symposium on Design and Diagnostics <strong>of</strong> Electronic Circuits and Systems (DDECS),<br />

2010, Vienna, Austria, pp. 23-26, April 2010.<br />

[37] A. Rahimi, M. E. Salehi, S. Mohammadi, S. M. Fakhraie, A. Azarpeyvand,<br />

“Energy/throughput trade-<strong>of</strong>f in a fully asynchronous NoC for GALS-based MPSoC<br />

architectures,” in Proc. 5th <strong>In</strong>ternational Conference on Design and Technology <strong>of</strong><br />

<strong>In</strong>tegrated Systems in Nanoscale Era (DTIS), 2010, Hammamet, Tunisia, pp. 1-6, March<br />

2010.<br />

[38] F. Firouzi, M. Salehi, A. Azarpeyvand, S. M. Fakhraie, and F. Wang, “Reliability<br />

considerations in dynamic voltage and frequency scaling schemes,” in Proc. 5th<br />

<strong>In</strong>ternational Conference on Design and Technology <strong>of</strong> <strong>In</strong>tegrated Systems in Nanoscale<br />

Era (DTIS), 2010, Hammamet, Tunisia, pp. 1-4, March 2010.<br />

[39] A. Yazdanbakhsh, M. E. Salehi, and S. M. Fakhraie, “Architecture-aware graph-covering<br />

algorithm for custom instruction selection,” in Proc. 5th <strong>In</strong>ternational Conference on<br />

Future <strong>In</strong>formation Technology (FutureTech), 2010, Busan, Korea, pp. 1-6, May 2010.<br />

[40] P. M. Naini, S. M. Fakhraie, and A. N. Avanaki, “Sudoku Bit Arrangement for Combined<br />

Demosaicking and Watermarking in Digital Camera,” in Proc. Second <strong>In</strong>ternational<br />

Conference on Advances in Databases Knowledge and Data Applications (DBKDA),<br />

2010, Menuires, France, pp. 41-44, April 2010.<br />

[41] Z. Sharifi Mehrjardi, N. Kazemian Amiri, and S. M. Fakhraie, “Bit-width optimization <strong>of</strong><br />

CS-ACELP speech coder by SIMULINK: Core layer <strong>of</strong> <strong>the</strong> new G.729.1 standard,” in Proc.<br />

14th <strong>In</strong>ternational CSI Computer Conference, 2009, (CSICC 2009), pp. 507-511, 20-21<br />

Oct. 2009.

[42] P. Monshizadeh Naeeni, A. Nasiri Avanaki, and S. M. Fakhraie, “A new approach for<br />

combined demosaicking and watermarking in digital camera pipeline,” in Proc. Fifth<br />

<strong>In</strong>ternational Joint Conference on INC, IMS and IDC, 2009, (NCM '09), pp. 1246-1250,<br />

25-27 Aug. 2009.<br />

[43] S. Vakili, S. M. Fakhraie, S. Mohammadi, and A. Ahmadi, “Particle swarm optimization<br />

for run-ime task decomposition and scheduling in evolvable MPSoC,” in Proc.<br />

<strong>In</strong>ternational Conference on Computer Engineering and Technology 2009, vol. 2, pp.<br />

28-32, 22-24 Jan. 2009.<br />

[44] R. Yousefi, A. Jalili, and S. M. Fakhraie, “Frequency domain testing: A new approach in<br />

online test <strong>of</strong> VLSI digital signal processing systems,” in Proc. <strong>In</strong>ternational Conference<br />

on Computer Engineering and Technology 2009, vol. 2, pp. 136-140, 22-24 Jan. 2009.<br />

[45] A. Jalili, R. Yousefi, S. M. Fakhraie, and S. Nader-Esfahani, “Effects <strong>of</strong> different mobile<br />

channel conditions on IEEE 802.20,” in Proc. <strong>In</strong>ternational Conference on Computer<br />

Engineering and Technology 2009, vol. 2, pp. 287-291, 22-24 Jan. 2009.<br />

[46] A. Ahmadi, S. M. Fakhraie, and C. Lucas, “Behavioral fault model for neural networks,” in<br />

Proc. <strong>In</strong>ternational Conference on Computer Engineering and Technology 2009, vol. 2,<br />

pp. 71-75, 22-24 Jan. 2009.<br />

[47] A. Ahmadi, M. H. Sargolzaie, S. M. Fakhraie, C. Lucas, and S. Vakili, “A low-cost faulttolerant<br />

approach for hardware implementation <strong>of</strong> artificial neural networks,” in Proc.<br />

<strong>In</strong>ternational Conference on Computer Engineering and Technology 2009, vol. 2, pp.<br />

93-97, 22-24 Jan. 2009.<br />

[48] A. Jalili, S. M. Fakhraie, and S. Nader-Esfahani, “Performance evaluation <strong>of</strong> IEEE 802.20<br />

PHY layer,” in Proc. <strong>In</strong>ternational Conference on Computer Engineering and<br />

Technology 2009, vol. 2, pp. 161-165, 22-24 Jan. 2009.<br />

[49] F. Kashfi,S. M. Fakhraie, and S. Safari, “A 65nm 10GHz pipelined MAC structure,” in<br />

Proc. IEEE <strong>In</strong>ternational Symposium on Circuits and Systems, 2008, (ISCAS 2008), pp.<br />

460-463, 18-21 May 2008.<br />

[50] R. Yousefi, M. H. Sargolzaie, and S. M. Fakhraie, “Low cost concurrent error detection for<br />

lattice wave digital filters,” in Proc. <strong>In</strong>ternational Symposium onTelecommunications,<br />

2008, (IST 2008), pp. 598-601, 27-28 Aug. 2008.<br />

[51] E. Rohani and S. M. Fakhraie, “Optimum design <strong>of</strong> Viterbi decoder for high speed data<br />

telecommunication receivers with 802.16a case study,” in Proc. <strong>In</strong>ternational Symposium<br />

onTelecommunications, 2008, (IST 2008), pp. 246-250, 27-28 Aug. 2008.<br />

[52] Z. Pajouhi, S. M. Fakhraie, and S. H. Jamali, “Hardware implementation <strong>of</strong> a 802.11n<br />

MIMO OFDM transceiver,” in Proc. <strong>In</strong>ternational Symposium onTelecommunications,<br />

2008, (IST 2008), pp. 414-419, 27-28 Aug. 2008.<br />

[53] R. Yousefi, A. Ahmadi, and S. M. Fakhraie, “Design flow for hardware implementation <strong>of</strong><br />

digital filters,” in Proc. <strong>In</strong>ternational Symposium onTelecommunications, 2008, (IST<br />

2008), pp. 586-591, 27-28 Aug. 2008.<br />

[54] A. Farmahini-Farahani, S. M. Fakhraie, and S. Safari, “Scalable architecture for on-chip<br />

neural network training using swarm intelligence,” in Proc. Design, Automation and Test<br />

in Europe, 2008, (DATE '08), pp. 1340-1345, 10-14 March 2008.<br />

[55] R. Yousefi, M. H. Sargolzaie, and S. M. Fakhraie, “Online and <strong>of</strong>fline test unification in<br />

digital filters,” in Proc. <strong>In</strong>ternational Conference on <strong>In</strong>novations in <strong>In</strong>formation<br />

Technology, 2008, (IIT 2008), pp. 111-115, 16-18 Dec. 2008.

[56] R. Yousefi and S. M. Fakhraie, “Frequency domain concurrent error detection in DSP<br />

systems,” in Proc. <strong>In</strong>ternational Conference on <strong>In</strong>novations in <strong>In</strong>formation Technology,<br />

2008, (IIT 2008), pp. 54-58, 16-18 Dec. 2008.<br />

[57] S. Vakili, S. M. Fakhraie, and S. Mohammadi, “Designing an MPSoC architecture with runtime<br />

and evolvable task decomposition and scheduling: A neural network case study,” in<br />

Proc. <strong>In</strong>ternational Conference on <strong>In</strong>novations in <strong>In</strong>formation Technology, 2008, (IIT<br />

2008), pp. 106-110, 16-18 Dec. 2008.<br />

[58] M. Hamzeh, S. Arab, S. M. Fakhraie, and C. Lucas, “An improvement on LEACH<br />

algorithm with a fuzzy processor,” in Proc. 14th Asia-Pacific Conference on<br />

Communications, 2008, (APCC 2008), pp. 1-5, 14-16 Oct. 2008.<br />

[59] N. Sedaghati-Mokhtari, M. Nazm-Bojnordi, A. Hormati, and S. M. Fakhraie, “An efficient<br />

and extendable modeling approach for VLIW DSP processors,” in Proc. 13th <strong>In</strong>ternational<br />

Computer Society <strong>of</strong> Iran Computer Conference, March 9-11, 2008, Kish Isl., Iran,<br />

published by Springer-Verlag Berlin, Advances in Computer Science and Engineering,<br />

vol. 6, pp. 267-274, 2008.<br />

[60] Mostafa E. Salehi, S. M. Fakhraie, A. Banaiyan, and A. Hormati, “Design <strong>of</strong> a custom<br />

packet switching engine for network applications,” in Proc. 13th <strong>In</strong>ternational Computer<br />

Society <strong>of</strong> Iran Computer Conference, March 9-11, 2008, Kish Isl., Iran, published by<br />

Springer-Verlag Berlin, Advances in Computer Science and Engineering, vol. 6, pp.<br />

786–790, 2008.<br />

[61] N. Kazemian Amiri, S. M. Fakhraie,G. A. Hosein-Zadeh, and S. M. Mousavinejad,<br />

“Modeling <strong>of</strong> ITU-T G.729 codec with bit-width optimization for intensive computation<br />

blocks,” in Proc. <strong>In</strong>ternatonal Conference on Microelectronics, 2007, (ICM 2007), pp.<br />

47-50, 29-31 Dec. 2007.<br />

[62] S. A. Sadrossadat, N. Kazemian Amiri, and S. M. Fakhraie, “An efficient multi-operand<br />

addition structure,” in Proc. <strong>In</strong>ternatonal Conference on Microelectronics, 2007, (ICM<br />

2007), pp. 73-76, 29-31 Dec. 2007.<br />

[63] B. Zamanlooy, A. Ayatollahi, S. M. Fakhraie, M. Chahardori, “<strong>In</strong>vestigating different circuit<br />

styles for digital circuits using organic transistors,” in Proc. <strong>In</strong>ternational Symposium on<br />

<strong>In</strong>tegrated Circuits, 2007, (ISIC '07), pp. 5-8, 26-28 Sept. 2007.<br />

[64] A. Saghafi and S. M. Fakhraie, “An exact analysis <strong>of</strong> <strong>the</strong> linear serial acquisition for ultrawideband<br />

communication systems,” in Proc. IEEE <strong>In</strong>ternational Conference on Ultra-<br />

Wideband, 2007, (ICUWB 2007), Singapore, pp. 880-883, 24-26 Sep. 2007.<br />

[65] A. Saghafi and S. M. Fakhraie, “Optimized baseband design <strong>of</strong> an ultra-wideband impulse<br />

radio receiver,” in Proc. IEEE <strong>In</strong>ternational Conference on Ultra-Wideband, 2007,<br />

(ICUWB 2007), Singapore, pp. 805-808, 24-26 Sep. 2007.<br />

[66] A. Farmahini-Farahani, S. M. Fakhraie, and S. Safari, “SOPC-based architecture for discrete<br />

particle swarm optimization,” in Proc. 14 th IEEE <strong>In</strong>ternational Conference on<br />

Electronics, Circuits and Systems, 2007, (ICECS 2007), Marrakech, Morocco, pp. 1003-<br />

1006, 11-14 Dec. 2007.<br />

[67] N. Sedaghati-Mokhtari, M. N. Bojnordi, A. Farmahini-Farahani, M. Mousavinezhad, and S.<br />

M. Fakhraie, “Simulation <strong>of</strong> voice processing applications through VLIW DSP<br />

architectures,” in Proc. 14 th IEEE <strong>In</strong>ternational Conference on Electronics, Circuits and<br />

Systems, 2007, (ICECS 2007), Marrakech, Morocco, pp. 291-293, 11-14 Dec. 2007.

[68] N. Sedaghati-Mokhtari, M. N. Bojnordi, and S. M. Fakhraie, “MDST: Multiprocessor DSP<br />

simulation toolkit for voice processing applications,” in Proc. 15 th <strong>In</strong>ternational<br />

Symposium on Modeling, Analysis, and Simulation <strong>of</strong> Computer and<br />

Telecommunication Systems, 2007, (MASCOTS '07), Istanbul, Turkey, pp. 173-178, 24-26<br />

Oct. 2007.<br />

[69] A. Farmahini-Farahani, M. Laali, A. Moghimi, and S. M. Fakhraie, S. Safari, “Mesh<br />

architecture for hardware implementation <strong>of</strong> particle swarm optimization,” in Proc.<br />

<strong>In</strong>ternational Conference on <strong>In</strong>telligent and Advanced Systems, 2007, (ICIAS 2007),<br />

Kuala Lumpur, Malaysia, pp. 1300-1305, 25-28 Nov. 2007.<br />

[70] S. M. Mortazavi Zanjani, S. Rahimian Omam, S. M. Fakhraie, and O. Shoaei,<br />

“Experimental evaluation <strong>of</strong> different realizations <strong>of</strong> recursive CIC filters,” in Proc.<br />

Canadian Conference on Electrical and Computer Engineering, 2006, (CCECE '06),<br />

Ottawa, Canada, pp. 1056-1059, May 2006.<br />

[71] S. M. Mortazavi Zanjani, S. Rahimian Omam, S. M. Fakhraie, and O. Shoaei, “Algorithmic<br />

design <strong>of</strong> high-precision low-power multi-stage decimation filters,” in Proc. 49th IEEE<br />

<strong>In</strong>ternational Midwest Symposium on Circuits and Systems, 2006, (MWSCAS '06), vol.<br />

2, pp. 184-187, 6-9 Aug. 2006.<br />

[72] Somayyeh Rahimian Omam, S. M. Mortazavi Zanjani, S. M. Fakhraie, and O. Shoaei,<br />

“Design <strong>of</strong> high-precision low-power interpolation modules with modified SINC filters,” in<br />

Proc. 49th IEEE <strong>In</strong>ternational Midwest Symposium on Circuits and Systems, 2006,<br />

(MWSCAS '06), vol. 1, pp. 620-624, 6-9 Aug. 2006.<br />

[73] Ardavan Pedram, Masoud Daneshtalab, and Sied Mehdi Fakhraie “An efficient parallel<br />

architecture for matrix computations,” in Proc. 24 th Norchip Conference, pp. 171-174, Nov.<br />

2006.<br />

[74] Somayyeh Rahimian Omam, S. M. Mortazavi Zanjani, S. M. Fakhraie, and O. Shoaei,<br />

“Implementation <strong>of</strong> multiplier block with reduced adder cost,” in Proc. 13 th IEEE<br />

<strong>In</strong>ternational Conference on Electronics, Circuits and Systems, 2006, (ICECS 2006), pp.<br />

842-845, 10-13 Dec. 2006.<br />

[75] S. M. Mortazavi Zanjani, S. M. Fakhraie, O. Shoaei, and M. E. Salehi, “Design <strong>of</strong> FIR<br />

filters using identical subfilters <strong>of</strong> even length,” in Proc. <strong>In</strong>ternational Conference on<br />

Microelectronics, 2006, (ICM '06), pp. 83-86, 16-19 Dec. 2006.<br />

[76] M. Najibi, M. Salehi, A. A. Kusha, M. Pedram, S. M. Fakhraie, and H. Pedram, “Dynamic<br />

voltage and frequency management based on variable update intervals for frequency setting,”<br />

in Proc. IEEE/ACM <strong>In</strong>ternational Conference on Computer-Aided Design, 2006,<br />

(ICCAD '06), pp. 755-760, 5-9 Nov. 2006.<br />

[77] H. Esmaeilzadeh, M. R. Jamali, P. Saeedi, A. Moghimi, C. Lucas, S. M. Fakhraie, "NNEP,<br />

design pattern for neural-network-based embedded systems," in 14 th <strong>In</strong>t. Conf. Mixed<br />

Design 2007 (MIXDES 2007), Poland, pp. 673-678, June 2007.<br />

[78] Amir Agah, S. Mehdi Fakhraie, and A. Emami-Neyestanak, "Tertiary-Tree 12-GHz 32-bit<br />

Adder in 65nm Technology," in Proc. IEEE <strong>In</strong>t. Symposium Circuits and Systems<br />

(ISCAS07), New Orleans, USA, pp. 3006-3009, May 2007.<br />

[79] Ahmad Saghafi and S. Mehdi Fakhraie, "A new search space reduction technique for<br />

acquisition <strong>of</strong> UWB signals in multipath channels," in IEEE 65th Vehicular Technology<br />

Conference (VTC2007-Spring), Dublin, Ireland, pp. 1559-1563, April 2007.

[80] A. Farmahini-Farahani, M. Kamal, S. M. Fakhraie, and S. Safari, “HW/SW partitioning<br />

using discrete particle swarm,” in Proc. Great Lakes Symposium on VLSI, Stresa-Lago<br />

Maggiore, Italy, pp. 359-364, Mar. 11-13, 2007.<br />

[81] N. Kazemian Amiri and S. M. Fakhraie, “Digital network echo cancellation using genetic<br />

algorithm and combined GA-LMS method,” in Proc. Asian Pacific Conference on Circuits<br />

and Systems (APCCAS’06), Singapore, pp. 1822-1825, Dec. 4-7, 2006.<br />

[82] Z. Pajouhi and S. M. Fakhraie, ”A novel neural network GA-optimized controller for QoS<br />

support in wireless MACs,” in Proc. Asian Pacific Conference on Circuits and Systems<br />

(APCCAS’06), Singapore, pp. 1527-1530, Dec. 4-7, 2006.<br />

[83] M. Nabipoor, S. A. Khodaian, N. Sedaghati-Mokhtari, S. M. Fakhraie, and S. H. Jamali, "A<br />

high-speed low-complexity VLIS SISO architecture," in Proc. Asian Pacific Conference on<br />

Circuits and Systems (APCCAS’06), pp. 1512-1515, Singapore, Dec. 4-7, 2006.<br />

[84] A. Saghafi and S. M. Fakhraie, "Rapid Acquisition <strong>of</strong> Ultra-Wideband Signals in Multipath<br />

Environments," in Proc. Asian Pacific Conference on Circuits and Systems<br />

(APCCAS’06), pp. 1818-1821, Singapore, Dec. 4-7, 2006.<br />

[85] N. Moezi-Madani, H. Holisaz, and S. M. Fakhraie, "Digital audio broadcasting system<br />

modeling and hardware implementation," in Proc. Asian Pacific Conference on Circuits<br />

and Systems (APCCAS’06), pp. 1814-1817, Singapore, Dec. 4-7, 2006.<br />

[86] E. Rahmani, S. M. Fakhraie, and M. Kamarei, “Finding Agent-Based Energy-Efficient<br />

Routing in Sensor Networks using Parallel Genetic Algorithm”, in Proc. <strong>In</strong>t. Conf.<br />

Microelectronics 2006 (ICM06), Saudi Arabia, pp. 119-122, Dec. 16-19, 2006.<br />

[87] S. Rahmanian, E. Rahmani, A. Nasiri, and S. M. Fakhraie, “An Optimal Structure for<br />

Implementation <strong>of</strong> Digital Filters,” in Proc. <strong>In</strong>t. Conf. Microelectronics 2006 (ICM06),<br />

Saudi Arabia, pp. 95-98, Dec. 16-19, 2006.<br />

[88] A. Pedram, M. Daneshtalab, N. Sedaghati-Mokhtari, and S. M. Fakhraie, “A highperformance<br />

memory-efficient parallel hardware for matrix computation in signal processing<br />

applications,” in Proc. <strong>In</strong>t. Symposium on Communication and <strong>In</strong>formation Technology<br />

(ISCIT06), pp. T2D-2-7, Bangkok, Thailand, Oct. 18-20, 2006.<br />

[89] F. Montazeri, M. Salmani-Jelodar, S. N. Fakhraie, and S. M. Fakhraie, "Evolutionary<br />

multiprocessor task scheduling," in Proc. PARELEC 2006, Poland, pp. 68-76, Sep. 2006.<br />

[90] A. Pedram, M. R. Jamali, S. M. Fakhraie, and C. Lucas,"Reconfigurable parallel hardware<br />

for computing local linear neuro-fuzzy model," in Proc. PARELEC 2006, Poland, pp. 198-<br />

201, Sep. 2006.<br />

[91] A. Banaiyan, H.R. Mahdiani, and S. M. Fakhraie, "S<strong>of</strong>tware implementation issues <strong>of</strong><br />

existing and new defuzzificztion methods," in Proc. 2006 IEEE World Congress<br />

Computational <strong>In</strong>telligence, Vancouver, Canada, pp. 8476-8481, July 2006.<br />

[92] M. Salmani Jelodar, Najmeh Fakhraie, Faeze Montazeri, S. Mehdi Fakhraie, and M. Nili<br />

Ahmadabadi, "A representation for genetic-algorithm-based multiprocessor task scheduling,"<br />

Proc. 2006 IEEE World Congress Computational <strong>In</strong>telligence, Vancouver, Canada, pp.<br />

1044-1051, July 2006.<br />

[93] M. Salmani Jelodar, Mehdi Kamal, S. Mehdi Fakhraie, and M. Nili Ahmadabadi, "SOPCbased<br />

parallel genetic algorithm," in Proc. 2006 IEEE World Congress Computational<br />

<strong>In</strong>telligence, Vancouver, Canada, pp. 9705-9711, July 2006.<br />

[94] A. Banaiyan, H. R. Mahdiani, and S. Mehdi Fakhraie, "PiFie: A platform-independent fuzzy<br />

instruction set extension," in Proc. NAFIPS06, Montreal, Canada, June 2006.

[95] A. Banaiyan, M. Salmani Jelodar, and S. Mehdi Fakhraie, "ISA extension to general purpose<br />

processors for fuzzy and genetic algorithm applications," in Proc. NAFIPS06, Montreal,<br />

Canada, June 2006.<br />

[96] H. Esmaeilzadeh, P. Saeedi, B. N. Araabi, C. Lucas, and S. M. Fakhraie, “Neural network<br />

stream processing core (NnSP) for embedded systems,” in Proc. IEEE <strong>In</strong>t. Symposium<br />

Circuits and Systems (ISCAS06), pp. 2773-2776, Greece, May 2006.<br />

[97] H. Esmaeilzadeh, A. Moghimi, E. Ebrahimi, C. Lucas, Z. Navabi, and S. M. Fakhraie,<br />

“DCim++: A C++ library for object oriented hardware design and distributed simulation,” in<br />

Proc. IEEE <strong>In</strong>t. Symposium Circuits and Systems (ISCAS06), pp. 1283-1286, Greece,<br />

May 2006.<br />

[98] F. Kashfi and S. M. Fakhraie, “Implementation <strong>of</strong> a high-speed low-power 32-bit adder in<br />

70nm technology,” in Proc. IEEE <strong>In</strong>t. Symposium Circuits and Systems (ISCAS06), pp.<br />

9-12, Greece, May 2006.<br />

[99] H. R. Mahdiani, A. Banaiyan, and S. M. Fakhraie, “Hardware implementation and<br />

comparison <strong>of</strong> new defuzzification techniques in fuzzy processors,” in Proc. Symposium<br />

Circuits and Systems (ISCAS06), pp. 4619-4622, Greece, May 2006.<br />

[100] M. Salmani Jelodar, S. M. Fakhraie, and M. Nili Ahmadabadi, "Two-stage morphological<br />

filter design using genetic algorithms," in Proc. IEEE <strong>In</strong>t. Conf. Engineering <strong>of</strong> <strong>In</strong>telligent<br />

Systems (ICEIS06), pp. 129-133, Islamabad, Pakistan, May 2006.<br />

[101] H. Holisaz, S. Shamshiri, F. Baharvand, and S. Mehdi Fakhraie, "Hardware Accelerator IP<br />

core for wireless 802.16 MAC," in Proc. Third Wireless and Optical Communication<br />

Networks (WOCN), pp. 1-5, <strong>In</strong>dia, April 2006.<br />

[102] H. Hollisaz, N. Moezzi Madani, and S. Mehdi Fakhraie, "A quantitative approach to digital<br />

filter implementation," Proc. IEEE <strong>In</strong>ternational Conference on Microelectronics 2005,<br />

pp. 160-164, Pakistan, Dec. 2005.<br />

[103] N. Moezzi-Madani, E. Rohani, and S. Mehdi Fakhraie, "Hardware considerations for<br />

digital audio broadcasting system," Proc. IEEE <strong>In</strong>ternational Conference on<br />

Microelectronics 2005, pp. 209-212, Pakistan, Dec. 2005.<br />

[104] S. M. Mortazavi Zanjani, S. M. Fakhraie, and O. Shoaei, "A comparative study and design<br />

<strong>of</strong> decimation filter for high-precision audio data converters," Proc. IEEE <strong>In</strong>ternational<br />

Conference on Microelectronics 2005, pp. 139-143, Pakistan, Dec. 2005.<br />

[105] M. Nazm-Bojnordi, N. Sedaghati-Mokhtari, and S. Mehdi Fakhraie, "A self-testing fully<br />

pipelined implementation for <strong>the</strong> advanced encryption standard," Proc. IEEE <strong>In</strong>ternational<br />

Conference on Microelectronics 2005, pp. 260-263, Pakistan, Dec. 2005.<br />

[106] N. Moezzi Madani, J. Hadi, and S. Mehdi Fakhraie, "Design and implementation <strong>of</strong> a fully<br />

digital 4FSK demodulator," Proc. European Conference on Circuit Theory and Design,<br />

pp. 277-280, Ireland, Dec. 2005.<br />

[107] A. Banaiyan, H.R. Mahdiani, and S.M. Fakhraie, "Cost-performance co-analysis in VLSI<br />

implementation <strong>of</strong> existing and new defuzzification methods," Proc. <strong>In</strong>ternational<br />

Conference on Computational <strong>In</strong>telligence for Modeling Control and Automation –<br />

CIMCA, Austria, Nov. 2005.<br />

[108] E. Rohani and S. M. Fakhraie, "Reducing round-<strong>of</strong>f error in an ADSL modem with blockfloating-point<br />

structure," in Proc. <strong>In</strong>ternational Symposium on Telecommunications<br />

(IST2005), Shiraz, Iran, Sep. 2005.

[109] M. Alisafaee, S. Ataee, S. M. Fakhraie, "Bandwidth-enhanced waste-free control technique<br />

for multi-queue network buffers," in Proc. <strong>In</strong>ternational Symposium on<br />

Telecommunications (IST2005), Shiraz, Iran, Sep. 2005.<br />

[110] G. R. Chaji and S. M. Fakhraie, "A low-power high-performance digital circuit for deep<br />

submicron technologies," in Proc. IEEE NEWCAS05, Quebec, Canada, June 19-22, 2005.<br />

[111] M. Alisafaee, and S. M. Fakhraie, Mohammad Tehranipoor "Architecture <strong>of</strong> an embedded<br />

queue management engine for high-speed network devices," in Proc. 2005 IEEE <strong>In</strong>t’l<br />

Midwest Symposium on Circuits and Systems, Cincinnati, USA, Aug. 2005.<br />

[112] Hadi Esmaeilzadeh, Farhang Farzan, Neda Shahidi, Sied Mehdi Fakhraie, Caro Lucas, and<br />

Mohammad Tehranipoor, " NnSP: Embedded neural networks stream processor," in Proc.<br />

2005 IEEE <strong>In</strong>t’l Midwest Symposium on Circuits and Systems, Cincinnati, USA, Aug.<br />

2005.<br />

[113] Saeed Shamshiri, S. Mehdi Fakhraie, and Zainalabedin Navabi, "Designing optimal<br />

forwarding tables with genetic algorithm," Proc. ACM SIGCOMM Workshop 2005,<br />

Beijing, China, April 2005.<br />

[114] Mehdi Salmani Jelodar, Sied Mehdi Fakhraie, and Majid Nili Ahmadabadi, "A new<br />

approach for training <strong>of</strong> artificial neural networks using population based incremental<br />

learning (PIBL), Proc. <strong>of</strong> <strong>the</strong> <strong>In</strong>t. Conf. Computational <strong>In</strong>telligence (ICCI 2004),<br />

Istanbul, Turkey, pp. 165-168, Dec. 2004.<br />

[115] Hadi Esmaeilzadeh, Hamed Farshbaf, Caro Lucas, and Sied Mehdi Fakhraie, "Digital<br />

implementation for conic section function networks," Proc. IEEE <strong>In</strong>t. Conf.<br />

Microelectronics 2004 (ICM2004), Tunis, Tunisia, pp. 564-567, Dec. 2004.<br />

[116] S. Shamshiri, and Sied Mehdi Fakhraie, "Parallel alias reduction for MP3 decoding," Proc.<br />

IEEE <strong>In</strong>t. Conf. Microelectronics 2004 (ICM2004), Tunis, Tunisia, pp. 438-441, Dec.<br />

2004.<br />

[117] M. Ghannad Rezaie, F. Farbiz, and Sied Mehdi Fakhraie, "An analytical approach to<br />

hardware-friendly adaptive learning rate neural networks," Proc. IEEE <strong>In</strong>t. Conf.<br />

Microelectronics 2004 (ICM2004), Tunis, Tunisia, pp. 320-323, Dec. 2004.<br />

[118] S. Shamshiri, S. Mehdi Fakhraie, and C. Lucas, "A genetic algorithm solution for<br />

designing optimal forwardign tables," Proc. Sixth Conf. <strong>In</strong>telligent Systems (CIS 2004),<br />

Kerman, Iran, Nov. 2004.<br />

[119] S. R. Abdollahi, S. M. Fakhraie, M. Kamaeri, and S. E. Abdollahi, "A 68MHz multichannel<br />

all-digital programmable oscillator," Proceedings 2003 10th IEEE <strong>In</strong>ternational<br />

Conference on Electronics, Circuits and Systems, 2003 (ICECS 2003),vol. 2 , pp. 475-<br />

478, 14-17 Dec. 2003.<br />

[120] S. R. Abdollahi, M. Kamaeri, and S. M. Fakhraie, "Semi-coherent GFSK receiver for<br />

DECT standard," Proceedings 2003 10th IEEE <strong>In</strong>ternational Conference on<br />

Electronics, Circuits and Systems, 2003 (ICECS 2003),vol. 3 , pp. 1244-1247, 14-17<br />

Dec. 2003.<br />

[121] Seyed Reza Abdollahi, Seyed Mehdi Fakhraei, Bertan Bakkaloglu, and Mahmoud<br />

Kamarei, "A crystal-based digital ring oscillator," Proceedings 2003 IEEE <strong>In</strong>ternational<br />

Conference on Field-Programmable Technology (FPT), Tokyo, Japan, pp. 319-323,<br />

Dec. 15-17, 2003.<br />

[122] Mohammad Tehranipour, Mehrdad Nourani, Mehdi Fakhraie, and Ali Afzali-Kusha,<br />

“Systematic test program generation for SoC testing using embedded processors,” ISCAS<br />

2003, Bangkok, Thailand, vol. 5, pp. 541-544, May 2003.<br />

[123] G. R. Chaji, R. M. Pourrad, S. M. Fakhraie, and M. H. Tehranipour, “EUTDSP: A design<br />

study <strong>of</strong> a new VLIW-based DSP architecture,” ISCAS 2003, Bangkok, Thailand, vol. 4,<br />

pp. 137-140, May 2003.

[124] S. M. Fakhraie, M. H. Tehranipour, M. R. Movahedin, and M. Nourani, "Fast prototyping<br />

<strong>of</strong> a DSP core," 45th Midwest Symposium on Circuits and Systems, vol. 2, Page(s): 215<br />

-218, 2002.<br />

[125] M. H. Tehranipour, M. Nourani, S. M. Fakhraie, and C. A. Papachristou, "Test<br />

optimization <strong>of</strong> bus-structured SoCs using embedded processor," 45th Midwest<br />

Symposium on Circuits and Systems, vol. 1, Page(s): 168-171, 2002.<br />

[126] R. Rafati, A. Z. Charaki, G. R. Chaji, S. M. Fakhraie, and K. C. Smith, “Comparison <strong>of</strong> a<br />

17b multiplier in dual-rail Domino and dual-rail D3L logic styles,” ISCAS 2002,<br />

Scottsdale, Arizona, vol. 3, pp. 257-260, May 26-29 2002.<br />

[127] G. R. Chaji, S. M. Fakhraie, and K. C. Smith, “Pseudo dynamic logic (SDL): A highspeed<br />

and low-power logic family,” ISCAS 2002, Scottsdale, Arizona, vol. 3, pp. 245-248,<br />

May 26-29 2002.<br />

[128] S. R. Abdollahi, S. M. Fakhraie, and Sayfe Kiaei, “An all-digital programmable digitallycontrolled-oscillator<br />

(DCO) for digital wireless applications,” ISCAS 2002, Scottsdale,<br />

Arizona, vol. 4, pp. 101-104, May 26-29 2002.<br />

[129] G. R. Chaji, S. M. Fakhraie, and K. C. Smith, “High-speed low-power adder design with a<br />

new logic style: Pseudo Dynamic Logic (SDL),” Proc. IEEE <strong>In</strong>t. Conf. Microelectronics<br />

2001 (ICM2001), (Rabat, Morocco), Oct.29-31 2001.<br />

[130] H. R. Mahdiany, A. Hormati, and S. M. Fakhraie, “A hardware accelerator for DSP system<br />

design: University <strong>of</strong> Tehran DSP hardware emulator (UTDHE),” Proc. IEEE <strong>In</strong>t. Conf.<br />

Microelectronics 2001 (ICM2001), (Rabat, Morocco), Oct.29-31 2001.<br />

[131] M. Tehranipour, Z. Navabi, and S. M. Fakhraie, “A low-cost BIST architecture for<br />

microprocessor/DSP cores,” Proc. Third Electronics Circuits and Systems Conf.<br />

(ECS’01), (Bratislava, Slovakia), Sep. 5-7 2001.<br />

[132] H. Zarei, O. Shoaei, and S. M. Fakhraie, “A low-power fully integrated Gaussian-MSK<br />

modulator based on <strong>the</strong> sigma-delta fractional-N frequency syn<strong>the</strong>sis,” Proc. ISCAS 2001<br />

(Sydney, Australia), vol. 4, pp. 100-103, May 2001.<br />

[133] M. Tehranipour, Z. Navabi, and S. M. Fakhraie, “An efficient BIST method for testing <strong>of</strong><br />

embedded SRAMs,” in Proc. ISCAS 2001, (Sydney, Australia), vol. 5, pp. 73-76, 6-9 May<br />

2001.<br />

[134] H. Zarei, O. Shoaei, S. M. Fakhraie, and M. M. Zakeri, “A 1.4 GHz/ 2.7 V programmable<br />

frequency divider for DRRS standard in 0.6 /spl mu/m CMOS process,” Proc. 7th IEEE<br />

<strong>In</strong>ternational Conference on Electronics, Circuits and Systems, 2000, (ICECS 2000),<br />

(Jounieh, Lebanon), vol. 2, pp. 887 –890, Dec. 2000.<br />

[135] S. R. Abdollahi, S. M. Fakhrai, and M. M. Zakeri, “Performance <strong>of</strong> phase locked loop<br />

GFSK demodulator in a multipath channel,” in Proc. 3rd <strong>In</strong>t. Symp. Wireless Personal<br />

Multimedia Communications (WPMC’00), (Bangkok, Thailand), pp. 825-829, Nov. 12-<br />

15, 2000.<br />

[136] S. A. Khodaian, S. H. Jamali, R. Hoshyar, S. M Fakhrai, and A. S. Bahai, “Threshold<br />

LogMAP SISO block for FPGA implementation <strong>of</strong> turbo decoder,” in Proc. 3rd <strong>In</strong>t.<br />

Symp. Wireless Personal Multimedia Communications (WPMC’00), (Bangkok,<br />

Thailand), pp. 538-542, Nov. 12-15, 2000.<br />

R. Rafati, A. Z. Charaki, S. M. Fakhraie, and K. C. Smith, “Data-driven dynamic logic versus<br />

NP-CMOS logic, a comparison,” in Proc. Twelfth IEEE <strong>In</strong>t. Conf. Microelectronics<br />

(ICM’2000), (Tehran, Iran), pp. 57-60, Oct. 31-Nov. 2, 2000.<br />

[137] Mehran Nadjarbashi, S. Mehdi Fakhraie, and Alireza Kaviani, “On routing structure for <strong>the</strong><br />

hybrid field programmable architecture,” Proc. Twelfth IEEE <strong>In</strong>t. Conf.<br />

Microelectronics (ICM’2000), (Tehran, Iran), pp. 259-264, Oct. 31-Nov. 2, 2000.

[138] Hossein Zarei, Omid Shoaei, S. M. Fakhraie, and M. M. Zakeri, “A low-power multimodulus<br />

divider in 0.6um digital CMOS technology,” Proc. Twelfth IEEE <strong>In</strong>t. Conf.<br />

Microelectronics (ICM’2000), (Tehran, Iran), pp. 359-362, Oct. 31-Nov. 2, 2000.<br />

[139] M. Haji-rostam, M. Maddah-Ali, A. Haft-Baradaran, M. T. Kilani, S. M. Fakhraie, M.<br />

Sharifkhani, and O. Shoaei, “Kalman-filtering timing recovery scheme for orthogonal<br />

frequency domain multiplexing (OFDM) systems,” in Proc. ICASSP’2000, (Istanbul,<br />

Turkey), pp. V-2681-2684, June 5-9 2000.<br />

[140] R. Rafati, S. M. Fakhraie, and K. C. Smith, “Low-power data-driven dynamic logic<br />

(D3L),” in Proc. ISCAS’2000, (Geneva, Switzerland), pp. I-752-755, 28-31 May 2000.<br />

[141] F. Bahmani, S. M. Fakhraie, and A. Khakifirooz, “A rail-to-rail one-Volt constant-Gm<br />

CMOS opamp,” in Proc. ISCAS’2000, (Geneva, Switzerland), pp. II-669-672, 28-31 May<br />

2000.<br />

[142] A. Kheirkhahi, S. M. Fakhraie, and M. Kamarei, “Algorithmic design <strong>of</strong> a 900 MHz<br />

CMOS RF power amplifier introducing SPICE-Smith chart method,” Proc. European<br />

Solid State Circuits Conference 1999 (ESSCIRC’99), (Germany), 17-20 Sept. 1999.<br />

[143] O. Nasibi, M. Nourani, S. M. Fakhraie, A. Zakeri, and A. Ghalambor-Dezfoli, “Multiaccess<br />

integrated memory management for deeply-pipelined processors,” Proc. Eleventh<br />

IEEE <strong>In</strong>t. Conf. Microelectronics (ICM’99), (Kuwait), pp. 285-289, 22-24 Nov. 1999.<br />

[144] M. Samady, M. Movahedin, S. M. Fakhraie, Z. Navabi, and A. Ghalambor-Dezfoli,<br />

“Implementation <strong>of</strong> serial port interconnections for integrated circuits,” Proc. Eleventh<br />

IEEE <strong>In</strong>t. Conf. Microelectronics (ICM’99), (Kuwait), pp. 291-294, 22-24 Nov. 1999.<br />

[145] A. Kheirkhahi, S. M. Fakhraie, and M. Kamarei, “A low-voltage high efficiency digitally<br />

programmable DC/DC converter,” Proc. Eleventh IEEE <strong>In</strong>t. Conf. Microelectronics<br />

(ICM’99), (Kuwait), pp. 281-284, 22-24 Nov. 1999.<br />

[146] F. Bahmany and S. M. Fakhraie, “A rail-to-rail 1-Volt CMOS opamp,” Proc. Eleventh<br />

IEEE <strong>In</strong>t. Conf. Microelectronics (ICM’99), (Kuwait), pp. 217-219, 22-24 Nov. 1999.<br />

[147] A. Sodagar, S. M. Fakhraie, and K. C. Smith, “A low-voltage Current-Controlled<br />

Oscillator with low supply dependency,” Proc. Tenth IEEE <strong>In</strong>t. Conf. Microelectronics<br />

(ICM’98), (Monastir, Tunisia), pp. 282-285, Dec. 14-16, 1998.<br />

[148] A. H. Abutalebi and S. M. Fakhraie, “A submicron analog neural network with an<br />

adjustable-level output unit,” Proc. Tenth IEEE <strong>In</strong>t. Conf. Microelectronics (ICM’98),<br />

(Monastir, Tunisia), pp. 294-297, Dec. 14-16, 1998.<br />

[149] F. Baharvand and S. M. Fakhraie, “A reduced lookup table for SRAM-based FPGA logic<br />

blocks,” Proc. Ninth IEEE <strong>In</strong>t. Conf. Microelectronics (ICM’97), (Bandung, <strong>In</strong>donesia),<br />

pp. 138-141, Oct. 8-10, 1997.<br />

[150] A. H. Abutalebi and S. M. Fakhraie, “Submicron analog multipliers: Overview,<br />

comparison, and modelling,” Proc. Ninth IEEE <strong>In</strong>t. Conf. Microelectronics (ICM’97),<br />

(Bandung, <strong>In</strong>donesia), pp. 85-88, Oct. 8-10, 1997.<br />

[151] S. Mehdi Fakhraie, J. M. Xu, and K. C. Smith, “Design and implementation <strong>of</strong><br />

SynapseMOS (SyMOS) Artificial Neural Networks,” Proc. Eighth <strong>In</strong>t. Conf.<br />

Microelectronics (ICM’96), (Cairo, Egypt), pp. 71-74, Dec. 14-16, 1996.<br />

[152] S. Mehdi Fakhraie, J. M. Xu, and K. C. Smith, “Application <strong>of</strong> analog quadratic neural<br />

networks (AQNNs) to function approximation problems,” Proc. <strong>In</strong>t. Conf. <strong>In</strong>telligent and<br />

Cognitive Systems, (Tehran, Iran), pp. 43-48, Sep. 1996.<br />

[153] S. Mehdi Fakhraie, J. M. Xu, and K. C. Smith, “Design <strong>of</strong> CMOS Quadratic Neural<br />

Networks,” Proc. IEEE Pacific Rim Conf. on Communications, Computers, and Signal<br />

Processing, (Victoria, BC, Canada) May 17-19, 1995.

[154] S. Mehdi Fakhraie, K. C. Smith, and J. M. Xu, “Comparison <strong>of</strong> three different architectures<br />

for MOS-Compatible quadratic synapses,” Proc. IEEE <strong>In</strong>t. Symp. Speech, Image<br />

Processing, and Neural Networks, (Hong Kong), pp. 483-6, April 13-16, 1994.<br />

[155] S. Mehdi Fakhraie and K. C. Smith, “Synapse-MOS (SyMOS) Transistors: <strong>In</strong>telligent<br />

MOS transistors with learning thresholds,” Proc. Canadian Conf. VLSI’93 (Banff,<br />

Alberta, Canada), pp. 7.28-33, Nov. 14-16, 1993.<br />

[156] S. Mehdi Fakhraie, A. Konrad, and K. C. Smith, “Application <strong>of</strong> neuro-computation<br />

techniques to sampled-data electromagnetic-field problems,” Records <strong>of</strong> <strong>the</strong> Ninth<br />

COMPUMAG Conf., (Miami, Florida), pp. 72-73, Nov. 1993.<br />

[157] S. Mehdi Fakhraie and K. C. Smith, “Generalized artificial neural networks,” Proc.<br />

Canadian Conf. Elec. and Comp. Eng. (Vancouver, BC, Canada), pp. 469-472, Sept. 14-<br />

17, 1993.

Reviewed Conference Papers (Published in <strong>the</strong> Proceedings <strong>of</strong> Local Conferences):<br />

[158] Z. Pajouhi and S. M. Fakhraie, “A new technique for implementation <strong>of</strong> continuous-time<br />

digital signal processing,” in Proc. 18 th Iranian Conf. Electrical Engineering<br />

(ICEE2010), Isfahan, Iran, May 2010.<br />

[159] S. Rahmanian, S. M. Fakhraie, and A. Nabavi, “Optimal bit-true model for implementation<br />

<strong>of</strong> a digital audio broadcasting OFDM system,” in Proc. 17 th Iranian Conf. Electrical<br />

Engineering (ICEE2009), Tehran, Iran, 12-14 May 2009.<br />

[160] Mohammad Reza Ghaderi, Omid Shoaei, and Sied Mehdei Fakhraie, “A novel ultra-lowvoltage<br />

CMOS RF-DC converter for long range passive RFID applications,” in Proc. 16 th<br />

Iranian Conf. Electrical Engineering (ICEE2008), Tehran, Iran, 2008.<br />

[161] E. Rahmani, S. M. Fakhraie, and M. Kamarei, “Design and modeling <strong>of</strong> physical layer <strong>of</strong><br />

IEEE 802.15.4 standard,” in Proc. 15 th Iranian Conf. Electrical Engineering<br />

(ICEE2007), Tehran, Iran, 15-17 May 2007, (in Farsi).<br />

[162] M. Nabipoor, S. A. Khodaian, S. Rahmanian, and S. M. Fakhraie, “Hardware consideration<br />

for S<strong>of</strong>t-<strong>In</strong>put S<strong>of</strong>t-Output (SISO) block <strong>of</strong> turbo decoder,” in Proc. 15 th Iranian Conf.<br />

Electrical Engineering (ICEE2007), Tehran, Iran, 15-17 May 2007.<br />

[163] Z. Pajouhi and S. M. Fakhraie, “Performance analysis <strong>of</strong> a time-domain equalizer in a<br />

WiMax system,” in Proc. 15 th Iranian Conf. Electrical Engineering (ICEE2007),<br />

Tehran, Iran, 15-17 May 2007.<br />

[164] M. E. Salehi, A. Hormati, A. Banaiyan, and S. M. Fakhraie, “A proposed architecture for<br />

layer-2 packet processing,” in Proc. 15 th Iranian Conf. Electrical Engineering<br />

(ICEE2007), Tehran, Iran, 15-17 May 2007.<br />

[165] A. Farmahini-Farahani and S. M. Fakhraie, “SOPC-based particle swarm optimization," in<br />

Proc. 12 th <strong>In</strong>ternational CSI Computer Conference (CSICC' 2007), Tehran, Iran, Feb.<br />

2007.<br />

[166] P. Saeedy and S. M. Fakhraie, "Co-processor for genetic algorithms," in Proc. 14 th Iranian<br />

Conf. Electrical Engineering (ICEE2006), Tehran, Iran, April 2006.<br />

[167] N. Sedaghati-Mokhtari, S. Rahmanian, and S. M. Fakhraie, "Hardware implementation<br />

analysis for digital filters," in Proc. 14 th Iranian Conf. Electrical Engineering<br />

(ICEE2006), Tehran, Iran, April 2006.<br />

[168] M. Salehi, M. Najibi, H. Pedram, A. Afzali-Kousha, and S. M. Fakhraie, "Implementation<br />

<strong>of</strong> dynamic control system for voltage and frequency for power reduction <strong>of</strong> processors," in<br />

Proc. 14 th Iranian Conf. Electrical Engineering (ICEE2006), Tehran, Iran, April 2006<br />

(in Persian).<br />

[169] M. Salmani Jelodar, H. Kamal, S. M. Fakhraie, and M. Nili Ahmadabadi, "SOPC-based<br />

parallel genetic algorithm," in Proc. 14 th Iranian Conf. Electrical Engineering<br />

(ICEE2006), Tehran, Iran, April 2006.<br />

[170] Sedigheh Hashemi and S. M. Fakhraie, "A novel technique for design and optimization <strong>of</strong><br />

FIR digital filters using genetic algorithms," in Proc. 14 th Iranian Conf. Electrical<br />

Engineering (ICEE2006), Tehran, Iran, April 2006.<br />

[171] H. Parande Afshar and S. Mehdi Fakhraie, "Parallel merged multiplier-accumulator<br />

coprocessor optimized for audio filters," in Proc. 11 th <strong>In</strong>ternational CSI Computer<br />

Conference (CSICC' 2006), Tehran, Iran, Jan. 2006.<br />

[172] M. Salmani Jelodar, S. Mehdi Fakhraie, M. Nili Ahmadabadi, "Improving morphological<br />

filters by intelligent algorithms," in Proc. Conf. Computational <strong>In</strong>telligence, Tehran, Iran,<br />

2005.

[173] H. Esmailzadeh, A. Pedram, A. Alaghi, B. N. Araabi, C. Lucas, and S. M. Fakhraie,<br />

"Neural network parallel data flow processor architecture," Proc. 13 th Iranian Conf.<br />

Electrical Engineering (ICEE2005), Zanjan, Iran, May 2005.<br />

[174] M. B. Vahidfar, S. M. Fakhraie, and M. Fardis, "Delta sigma enhanced, low SFDR, area<br />

efficient digital FM modulator," Proc. 13 th Iranian Conf. Electrical Engineering<br />

(ICEE2005), Zanjan, Iran, vol. 1, pp. 427-430, May 2005.<br />

[175] M. AliSafaee and S. M. Fakhraie, "Design and alalysis <strong>of</strong> a double bandwidth memory for<br />

network routers and switches," Proc. 13 th Iranian Conf. Electrical Engineering<br />

(ICEE2005), Zanjan, Iran, May 2005 (in Persian).<br />

[176] M. Alisafaee, Z. Navabi, and S. M. Fakhraie, "Doubling memory bandwidth for singlequeue<br />

network buffers using uniform distribution methods," Proc. 10 th Annual CSI Conf.<br />

(CSICC'2005), Tehran, Iran, pp. 172-179, Feb. 2005.<br />

[177] H. Kalantari, H. pedram, and S. M. Fakhraie, "A meth<strong>of</strong> for high-level energy estimation<br />

in template-based QDI asynchronous circuits," Proc. 10 th Annual CSI Conf.<br />

(CSICC'2005), Tehran, Iran, pp. 180-187, Feb. 2005.<br />

[178] S. shamshiri and S. M. Fakhraie, "Enhanced full expansion compression method for fast IP<br />

address lookup with minimum memory consumption," Proc. 10 th Annual CSI Conf.<br />

(CSICC'2005), Tehran, Iran, pp. 212-221, Feb. 2005.<br />

[179] M. Haji-Rostam, M. A. Maddah-Ali, A. Haft-Baradaran, M. T. Kilani, S. M. Fakhraie, M.<br />

Sharifkhani, and O. Shoaei, “A robust timing recovery scheme based on Kalman-filtering<br />

for OFDM systems,” Proc. Eighth Iranian Conf. Electrical Engineering, (Isfahan, Iran),<br />

pp. vol. 4, pp. 87-92, May 17-19, 2000.<br />

[180] M. Haji-Rostam, M. Sharifkhani, A. Haft-Baradaran, M. T. Kilani, O. Shoaei, S. M.<br />

Fakhraie, and A. Adibi, “System design <strong>of</strong> an ADSL modem based on ANSI T1.413,”<br />

Proc. Eighth Iranian Conf. Electrical Engineering, (Isfahan, Iran), vol. 4, pp. 173-180,<br />

May 17-19, 2000.<br />

[181] H. Zarei, M. M. Zakeri, O. Shoaei, and S. M. Fakhraie, “Design <strong>of</strong> a multi-modulus<br />

fractional-N low-power high-speed frequency divider,” Proc. Eighth Iranian Conf.<br />

Electrical Engineering, (Isfahan, Iran), May 17-19, 2000.<br />

[182] R. Rafati and S. M. Fakhraie, “Data-driven dynamic logic (D3L),” Proc. Seventh Iranian<br />

Conf. Electrical Engineering, (Tehran, Iran), pp. Ele. 61-68, 17-19 May, 1999.<br />

[183] A. Kheirkhahi, S. M. Fakhraie, M. Kamarei, “Design <strong>of</strong> CMOS-RF power amplifiers using<br />

SPICE-Smith chart method,” Proc. Seventh Iranian Conf. Electrical Engineering,<br />

(Tehran, Iran), pp. Ele.29-36, 17-19 May, 1999.<br />

[184] M. Samady, S. M. Fakhraie, Z. Navabi, and A. Ghalambor-Dezfoli, “Modelling and<br />

hardware implementation <strong>of</strong> a FIR filter with programmable architecture,” Proc. Seventh<br />

Iranian Conf. Electrical Engineering, (Tehran, Iran), 17-19 May, 1999.<br />

[185] B. Sajadi-Birea and S. M. Fakhraie, “Application <strong>of</strong> generalization-enhancement<br />

techniques to hand-written character recognition,” Proc. Fourth Annual <strong>In</strong>ternational<br />

Conf. Computer Society <strong>of</strong> Iran, (Tehran, Iran), Dec. 23-25, 1998.<br />

[186] A. H. Abutalebi and S. M. Fakhraie, “Universal characterization <strong>of</strong> a basic differential<br />

stage and a Gilbert multiplier by a general functional MOS model,” Proc. Sixth Iranian<br />

Conf. Electrical Engineering, (Tehran, Iran), pp. III67-72, 12-14 May, 1998.<br />

[187] A. Sodagar and S. M. Fakhraie, “Design <strong>of</strong> a digital CCO with low supply dependency,”<br />

Proc. Sixth Iranian Conf. Electrical Engineering, (Tehran, Iran), pp. III73-77, 12-14<br />

May, 1998.<br />

[188] S. Safari and S. M. Fakhraie, “Design <strong>of</strong> a hardware accelerator for Viterbi algorithm,”<br />

Proc. Sixth Iranian Conf. Electrical Engineering, (Tehran, Iran), pp. III99-104, 12-14<br />

May, 1998.

[189] B. Sajadi-Birea and S. M. Fakhraie, “A generalization enhancement method for artificial<br />

neural networks in function approximation applications,” Proc. Sixth Iranian Conf.<br />

Electrical Engineering, (Tehran, Iran), 12-14 May, 1998.<br />

[190] F. Baharvand and S. M. Fakhraie, “Design <strong>of</strong> an optimized architecture for <strong>the</strong> logic blocks<br />

<strong>of</strong> FPGA ICs,” Proc. Third Annual <strong>In</strong>ternational Conf. Computer Society <strong>of</strong> Iran,<br />

(Tehran, Iran), pp. 206-214, Dec. 23-25, 1997.<br />

[191] B. Alizadeh, S. M. Fakhraie, and Z. Navabi, “Rapid design <strong>of</strong> complex VLSI systems by<br />

using a multi-level simulation environment in VHDL,” Proc. Third Annual <strong>In</strong>ternational<br />

Conf. Computer Society <strong>of</strong> Iran, (Tehran, Iran), pp. 221-228, Dec. 23-25, 1997.<br />

[192] Atid Shamaie, S. M. Fakhraie, and B. Benhabib, “Accurate estimation <strong>of</strong> partly-occluded<br />

ellipse Parameters,” Proc. Fifth Iranian Conf. on Electrical Engineering, (Tehran, Iran),<br />

pp. 5-24-33, May 7-9, 1997.<br />

[193] F. Baharvand, and S. M. Fakhraie, “On designing reduced lookup tables for logic blocks <strong>of</strong><br />

SRAM-based FPGAs,” Proc. Fifth Iranian Conf. on Electrical Engineering, (Tehran,<br />

Iran), pp. 1-178-186, May 7-9, 1997.<br />

[194] S. Mehdi Fakhraie, J.M. Xu, and K.C. Smith, “Design <strong>of</strong> a new class <strong>of</strong> CMOS-compatible<br />

artificial neural networks,” Proc. Fourth Iranian Conf. on Electrical Engineering,<br />

(Tehran, Iran), pp. 489-97, May 1996.<br />