Dispositivos de las tecnologÃas CMOS - Departamento de ...

Dispositivos de las tecnologÃas CMOS - Departamento de ...

Dispositivos de las tecnologÃas CMOS - Departamento de ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

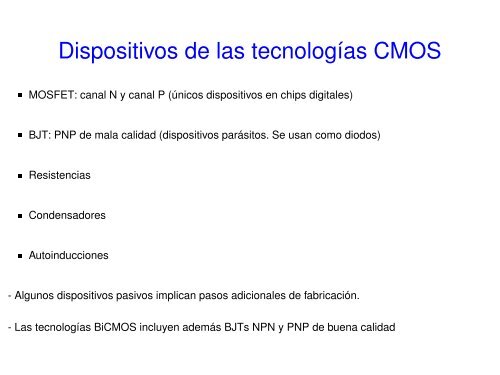

<strong>Dispositivos</strong> <strong>de</strong> <strong>las</strong> tecnologías <strong>CMOS</strong><br />

MOSFET: canal N y canal P (únicos dispositivos en chips digitales)<br />

BJT: PNP <strong>de</strong> mala calidad (dispositivos parásitos. Se usan como diodos)<br />

Resistencias<br />

Con<strong>de</strong>nsadores<br />

Autoinducciones<br />

- Algunos dispositivos pasivos implican pasos adicionales <strong>de</strong> fabricación.<br />

- Las tecnologías Bi<strong>CMOS</strong> incluyen a<strong>de</strong>más BJTs NPN y PNP <strong>de</strong> buena calidad

z<br />

Transistor BJT vertical<br />

y<br />

x<br />

x<br />

C<br />

B<br />

E<br />

C B E<br />

P + N + P +<br />

N<br />

P<br />

Ic<br />

− PNP<br />

BJT<br />

− El colector siempre es el sustrato<br />

N<br />

P<br />

Aplicaciones:<br />

− Referencias <strong>de</strong> tensión Band−Gap<br />

− Muy poca ganancia<br />

(β =5)<br />

F

Transistor BJT Lateral<br />

z<br />

E<br />

y<br />

x<br />

G<br />

B<br />

SUB<br />

x<br />

C<br />

SUB<br />

B<br />

C G<br />

E<br />

SUB<br />

B<br />

C<br />

E<br />

G<br />

P<br />

P + N + P + P +<br />

N<br />

Ic<br />

Isub<br />

N<br />

P<br />

− PNP<br />

− Terminales B y G conectados juntos para evitar conducción<br />

por MOSFET parásito<br />

− Hay un PNP vertical parásito que también conduce

(5 cuadros)<br />

W<br />

RESISTENCIAS<br />

(Lámina conductora: 2 dimensiones)<br />

Nº <strong>de</strong> cuadros = L / W<br />

R = ρ x Nº <strong>de</strong> cuadros<br />

1 c 1 c 1 c 1 c 1 c<br />

L<br />

Parámetros:<br />

− L<br />

− W<br />

− N. of Bends (número <strong>de</strong> pliegues)<br />

1 c 1 c 1 c 1 c 1 c<br />

0.6c<br />

1 c 1 c 1 c 1 c<br />

1 c<br />

(13.2 cuadros)<br />

1 c<br />

1 c<br />

(11 cuadros)<br />

1 c<br />

1 c<br />

1 c<br />

1 c<br />

1 c<br />

1 c<br />

0.6c<br />

1 c<br />

1 c<br />

1 c<br />

1 c<br />

1 c

S<br />

A<br />

B<br />

RNWELL<br />

1000 Ω /<br />

RDIFFP<br />

140 Ω /<br />

P<br />

P + N + N +<br />

N<br />

S A B<br />

P +<br />

A B<br />

S<br />

A B<br />

N +<br />

N<br />

P<br />

S<br />

A<br />

B<br />

RPOLY<br />

8 Ω /<br />

50 Ω /<br />

P<br />

Oxido grueso<br />

A<br />

B

Resistencias<br />

- Las resistencias construidas en el silicio (RNWELL, RDIFFP) se pue<strong>de</strong>n consi<strong>de</strong>rar como transistores<br />

J-FET con una tensión <strong>de</strong> pinch-off muy gran<strong>de</strong>.<br />

- Esto se traduce en unas <strong>de</strong>pen<strong>de</strong>ncias <strong>de</strong> la resistencia con el voltaje y la temperatura ma<strong>las</strong>.<br />

ρ □ (Ω/□) Coef. V (ppm/V) Coef. T (ppm/K) Tolerancia<br />

RNWELL 1000 10000 8000 40 %<br />

RDIFFP 140 200 1500 30 %<br />

RPOLY 8 100 900 30 %<br />

RPOLY HR 50 100 590 20 %<br />

METAL 1 0.07 - - 70 %

CONDENSADORES MOS<br />

cap.<br />

UNION MOS<br />

varactor<br />

C<br />

LF<br />

Cox<br />

P<br />

Acumulación<br />

HF ~1/3 Cox<br />

Inversión<br />

0<br />

V<br />

Con<strong>de</strong>nsador <strong>de</strong> ACUMULACION<br />

(varactor)<br />

Con<strong>de</strong>nsador <strong>de</strong> INVERSION<br />

(transistor)<br />

N + N + N + P +<br />

P +<br />

P<br />

N<br />

P<br />

N

Con<strong>de</strong>nsadores MOS <strong>de</strong> acumulación<br />

No se necesitan pasos adicionales en su fabricación. (<strong>CMOS</strong> éstandar)<br />

Alta <strong>de</strong>nsidad <strong>de</strong> capacidad (fF/µm 2 ). Mayor que otros tipos <strong>de</strong> con<strong>de</strong>nsador<br />

Tiene polaridad. Requiere un nivel <strong>de</strong> DC.<br />

Varactor. C(V). Coeficiente <strong>de</strong> voltaje malo.<br />

Coeficiente <strong>de</strong> temperatura malo.<br />

Aplicaciones: Varactor, Desacoplo <strong>de</strong> alimentación...

Con<strong>de</strong>nsador <strong>de</strong> Doble Polisilicio<br />

Con<strong>de</strong>nsador MIM<br />

Z<br />

X<br />

Oxido grueso<br />

Poly 2<br />

Poly 1<br />

Metal N<br />

Siliciuro<br />

Y<br />

Con<strong>de</strong>nsador interdigitado<br />

X

Con<strong>de</strong>nsadores <strong>de</strong> doble poly / MIM<br />

Necesitan pasos <strong>de</strong> fabricación adicionales<br />

No tienen polaridad<br />

Asimétricos. La capacidad parásita al sustrato es mucho mayor en la placa inferior<br />

Precisos<br />

Con<strong>de</strong>nsadores interdigitados<br />

No necesitan pasos <strong>de</strong> fabricación adicionales<br />

Simétricos<br />

Densidad <strong>de</strong> capacidad aceptable en tecnologías <strong>CMOS</strong> finas<br />

Poco precisos. Tolerancia: 40 %

AUTO INDUCCIONES<br />

− Capas <strong>de</strong> metal grueso<br />

(menor resistencia serie)<br />

− Sustrato <strong>de</strong> alta resistividad<br />

(poco dopado)<br />

− Rango: <strong>de</strong>cenas <strong>de</strong> nH<br />

(f > 1GHz)<br />

− Qmax ~ 10<br />

− Mo<strong>de</strong>lado: ASITIC<br />

A B<br />

A B<br />

A<br />

C1<br />

L<br />

SUB<br />

Rs<br />

B<br />

C2

TRANSISTOR MOSFET<br />

D<br />

G<br />

I D<br />

B<br />

V DS<br />

I<br />

D<br />

LINEAR<br />

TRIODO<br />

OHMICA<br />

V GS<br />

SATURACION<br />

S<br />

I Dsat<br />

SATURACION<br />

V<br />

GS<br />

CORTE<br />

CORTE<br />

V<br />

DS<br />

V T<br />

V GS

TRANSISTOR MOSFET en SATURACION (V DS > V OV )<br />

I D = K P<br />

2<br />

W<br />

L<br />

(V GS − V T ) 2 ; Definimos: V OV = (V GS − V T )<br />

I D = K P<br />

2<br />

W<br />

L V 2 OV<br />

K P <strong>de</strong>pen<strong>de</strong> <strong>de</strong> la tecnología y <strong>de</strong>l tipo <strong>de</strong>l transistor (canal N o P).<br />

K P = µ 0 C OX unida<strong>de</strong>s : A/V 2<br />

µ 0 : Mobilidad <strong>de</strong> los portadores en el canal (m 2 /(V · s)). La mobilidad <strong>de</strong> los electrones suele<br />

triplicar a la <strong>de</strong> los huecos.<br />

C OX = ε 0ε SiO2<br />

t ox<br />

: Capacidad <strong>de</strong>l óxido <strong>de</strong> puerta por unidad <strong>de</strong> área (F/m 2 )<br />

W y L son el ancho y largo <strong>de</strong>l canal <strong>de</strong>l MOSFET

TRANSISTOR MOSFET en SATURACION<br />

La corriente <strong>de</strong>pen<strong>de</strong> ligeramente <strong>de</strong> V DS :<br />

I D = K P<br />

2<br />

W<br />

L (V GS − V T ) 2 (1 + λV DS )<br />

I<br />

D<br />

1/r = ds<br />

I D0<br />

λ<br />

I D0<br />

V GS<br />

−1/λ<br />

V<br />

DS<br />

λ <strong>de</strong>pen<strong>de</strong> <strong>de</strong> la longitud <strong>de</strong>l canal: λ ∝ 1<br />

L−L 0

Mo<strong>de</strong>lo simple <strong>de</strong> PEQUEÑA SEÑAL <strong>de</strong>l MOSFET<br />

g m = ∂I D<br />

∂V GS<br />

1<br />

r ds<br />

= ∂I D<br />

∂V DS<br />

G<br />

D<br />

v g v r ds<br />

gs<br />

m gs<br />

S,B<br />

g m = K P<br />

W<br />

L V OV =<br />

√<br />

2I D K P<br />

W<br />

L<br />

= 2I D<br />

V OV<br />

r ds = 1<br />

λI D

TRANSISTOR MOSFET en región TRIODO / LINEAL / OHMICA (V DS < V OV )<br />

I D = K P<br />

W<br />

L<br />

[<br />

(V GS − V T ) V DS − 1 ]<br />

2 V DS<br />

2<br />

Para V DS → 0, tenemos: I D ≈ K P<br />

W<br />

L<br />

V OV V DS = V DS<br />

r ON<br />

r ON =<br />

1<br />

K P<br />

W<br />

L<br />

V OV

Efecto <strong>de</strong> la tensión <strong>de</strong>l sustrato (V B ≠ V S )<br />

V<br />

G<br />

V<br />

V<br />

D<br />

S<br />

V<br />

B<br />

- El sustrato se comporta como la puerta <strong>de</strong> un JFET parásito<br />

- Aumenta la tensión umbral efectiva:<br />

V T = V T H0 + γ<br />

(√<br />

φ − V BS −<br />

√ )<br />

φ<br />

(φ ≈ 0,6V )<br />

- Transconductancia adicional (resta ganancia):<br />

g mb =<br />

γ<br />

2 √ φ − V BS<br />

g m

Mo<strong>de</strong>lo <strong>de</strong> pequeña señal incluyendo el efecto <strong>de</strong>l sustrato<br />

G<br />

D<br />

vgs<br />

g v m gs<br />

g<br />

mbv bs<br />

r ds<br />

S<br />

v bs<br />

B

MOSFET en alta frecuencia: Capacida<strong>de</strong>s parásitas<br />

SATURACION<br />

S<br />

C GS<br />

G<br />

C GB<br />

D<br />

C GD<br />

C<br />

SB<br />

C<br />

DB<br />

B<br />

Si la fuente y el sustrato están unidos: C GStot = C GS + C GB , C DS = C DB<br />

C GS ≈ 2 3 W · L · C OX<br />

C GD = C over · W

MOSFET en alta frecuencia: Mo<strong>de</strong>lo <strong>de</strong> pequeña señal<br />

Cgd<br />

G<br />

D<br />

Cgs<br />

g m<br />

v gs<br />

r ds<br />

Cds<br />

S<br />

ω T ≈ g m<br />

C gs<br />

= 3 2<br />

µ 0 V OV<br />

L 2<br />

(∼ 14 GHz, canal N, V OV = 200 mV, L = 0,35 µm)

MOSFET en alta frecuencia: Capacida<strong>de</strong>s parásitas<br />

TRIODO (Interruptores, Con<strong>de</strong>nsadores MOS <strong>de</strong> inversión)<br />

S<br />

C GS<br />

G<br />

D<br />

G<br />

Mo<strong>de</strong>lo normal<br />

1/2 W·L·Cox<br />

D<br />

r ON<br />

Mo<strong>de</strong>lo no cuasi−estático<br />

D<br />

W·L·Cox 1/2r ON<br />

G<br />

C SB<br />

B<br />

C DB<br />

1/2 W·L·Cox<br />

S<br />

1/2r ON<br />

S<br />

C GS = W · L · C OX

MOSFET en débil inversión / conducción subumbral<br />

1000<br />

Id (uA)<br />

100<br />

10<br />

1<br />

0.1<br />

α exp(Vov)<br />

Débil<br />

inversión<br />

Kp W<br />

L Vov<br />

2<br />

2<br />

Fuerte<br />

inversión<br />

0.01<br />

Conducción<br />

subumbral<br />

0.001<br />

-0.3 -0.2 -0.1 0 0.1 0.2 0.3 0.4<br />

Vov (V)<br />

I D,wi = W L I t exp<br />

(<br />

VOV<br />

nKT/q<br />

) {<br />

n : slope factor (∼ 1,5)<br />

I t : corriente para V OV = 0

RUIDO<br />

v<br />

v<br />

n1<br />

n2<br />

v n<br />

Señales NO correlacionadas: Se suman <strong>las</strong> POTENCIAS:<br />

v 2 n = v 2 n1 + v2<br />

n2<br />

- Densidad espectral (unida<strong>de</strong>s: V/ √ Hz o A/ √ Hz )<br />

- Ruido total en una banda <strong>de</strong> frecuencias (<strong>de</strong> f 0 a f 1 ):<br />

V 2 N,tot = ∫ f1<br />

f 0<br />

v n (f) 2 df<br />

- Si v n (f) = cte (ruido blanco) queda:<br />

V 2 N,tot = v2 n B<br />

(B = f 1 − f 0 = ancho <strong>de</strong> banda)

Ruido. Tipos. Fuentes físicas<br />

* Ruido blanco: <strong>de</strong>nsidad espectral constante<br />

Ruido térmico. Resistencias. Se <strong>de</strong>be al movimiento aleatorio <strong>de</strong> los electrones.<br />

v 2 n = 4KT R<br />

Ruido “shot”. Barreras <strong>de</strong> potencial (diodos, BJT...). Se <strong>de</strong>be al valor discreto <strong>de</strong> la carga <strong>de</strong>l<br />

electrón. (el electrón pasa o no pasa la barrera).<br />

i 2 n = 2qI (q : carga <strong>de</strong>l electron)<br />

* Ruido “flicker”: <strong>de</strong>nsidad espectral ∝ 1/f . Ruido rosa<br />

Origen poco claro, aunque se cree que se <strong>de</strong>be a la captura y emisión <strong>de</strong> portadores <strong>de</strong>s<strong>de</strong><br />

impurezas, estados superficiales, etc.

MOSFET: Fuentes <strong>de</strong> ruido<br />

D<br />

2<br />

log(i d )<br />

2<br />

(g v )<br />

m nf<br />

G<br />

v nf<br />

i<br />

n<br />

flicker<br />

i 2 n<br />

térmico<br />

S,B<br />

f<br />

corner<br />

log(f)<br />

Ruido térmico en el canal:<br />

i 2 n = 4KT γ g m (0,66 < γ < 2,5)<br />

Ruido Flicker. Dominante para frecuencias bajas (f < f corner ):<br />

v nf (f) 2 =<br />

K f<br />

C 2 ox W L f

MOSFET. Otras fuentes <strong>de</strong> ruido (importantes para LNAs)<br />

D<br />

G<br />

v ng<br />

R<br />

G<br />

v nb<br />

R<br />

B<br />

S,B<br />

- Las resistencias generan un voltaje <strong>de</strong> ruido v 2 n = 4KT R<br />

- El polisilicio <strong>de</strong> la puerta pue<strong>de</strong> tener una resistencia apreciable, R G , que da lugar a un ruido:<br />

v 2 n,poly = 4KT ρ □ poly W/L<br />

12 n 2<br />

n: número <strong>de</strong> puertas <strong>de</strong>l transistor (con un contacto a cada lado).<br />

- Sustrato poco dopado =>R B gran<strong>de</strong>. El ruido térmico <strong>de</strong>l sustrato da lugar a una corriente:<br />

i 2 nb = 4KT R B g 2 mb

MATCHING<br />

En el mundo analógico no existen dos valores iguales ( 1 − 1 ≠ 0 :)<br />

MISMATCH ≡ Variación <strong>de</strong> un parámetro <strong>de</strong> un dispositivo relativa al <strong>de</strong> otros dispositivos nominalmente<br />

idénticos <strong>de</strong>l mismo C. I.<br />

Causas <strong>de</strong>l MISMATCH<br />

• Variaciones sistemáticas<br />

◦ Gradientes: Parámetros tecnológicos <strong>de</strong>pendientes <strong>de</strong> la posición en la oblea<br />

◦ Efectos <strong>de</strong> bor<strong>de</strong><br />

◦ Efectos <strong>de</strong>l entorno <strong>de</strong>l dispositivo. Proximidad a otras estructuras<br />

• Variaciones estadísticas (aletorias)

MATCHING <strong>de</strong> transistores<br />

I D + ∆I D = K P + ∆K P<br />

2<br />

W + ∆W<br />

L + ∆L [V GS − (V T + ∆V T )] 2<br />

Mismatch <strong>de</strong> corriente: ∆I D<br />

I D<br />

∆K P : <strong>de</strong>bido a variaciones <strong>de</strong>l espesor <strong>de</strong>l óxido <strong>de</strong> puerta y <strong>de</strong>l dopado <strong>de</strong>l sustrato (movilidad<br />

<strong>de</strong> portadores)<br />

∆V T : <strong>de</strong>bido a variaciones en el dopado <strong>de</strong>l sustrato y a la carga atrapada en el óxido <strong>de</strong> puerta<br />

∆W , ∆L : Variaciones <strong>de</strong> la geometría <strong>de</strong>l transistor <strong>de</strong>bidas a la litografía

Estrategias para el buen MATCHING<br />

Utilizar dispositivos idénticos (misma W , misma L ). Para obtener ratios ≠ 1 se conectan dispositivos<br />

en paralelo o serie<br />

• De este modo los efectos <strong>de</strong> bor<strong>de</strong> son los mismos en todos los dispositivos.<br />

• Dispositivo gran<strong>de</strong> ≡ ∑ dispositivos pequeños<br />

I<br />

2I<br />

I<br />

2I<br />

MAL:<br />

W/L<br />

2W/L<br />

BIEN:<br />

W/L<br />

W/L<br />

W/L

Estrategias para el buen MATCHING<br />

Los dispositivos <strong>de</strong>ben estar próximos<br />

• Menor efecto <strong>de</strong> los gradientes<br />

• Layout entrelazado<br />

G1<br />

G2<br />

M1 M2 M1 M2<br />

S1<br />

D1<br />

S2<br />

D2

Estrategias para el buen MATCHING<br />

Layout <strong>de</strong> CENTROIDE COMÚN<br />

• Cancelación <strong>de</strong> efectos <strong>de</strong> gradientes (<strong>de</strong>rivadas impares)<br />

M1<br />

M2<br />

M2<br />

M1

Estrategias para el buen MATCHING<br />

Las corrientes <strong>de</strong>ben fluir en la misma dirección<br />

• Gradientes <strong>de</strong> dopado =>Campo eléctrico en el sustrato =>movilidad <strong>de</strong>pendiente <strong>de</strong> la dirección<br />

MAL<br />

BIEN<br />

I1 I2 I1 I2<br />

M1 M2 M1 M2

Estrategias para el buen MATCHING<br />

<strong>Dispositivos</strong> DUMMY<br />

• No se conectan<br />

• Hacen que el entorno sea similar en todos los dispositivos activos (Un entorno distinto pue<strong>de</strong><br />

generar errores en la litografía)<br />

DUMMY<br />

DUMMY<br />

DM M1 M2 M3 M4<br />

DM

Estrategias para el buen MATCHING<br />

Mismatch estadístico<br />

• N dispositivos en paralelo =>σ N = σ/ √ N<br />

• Mismatch inversamente proporcional al área activa <strong>de</strong>l dispositivo<br />

Valores típicos para el matching (estimación muy grosera)<br />

Transistores 1 %<br />

Resistencias 1 %<br />

Con<strong>de</strong>nsadores MIM, doble poly 0.1 %